高精度音频多位sigma-delta调制器设计

石立春 ,杨银堂,李迪,吴笑峰,丁瑞雪,梁宏军

(1. 西安电子科技大学 微电子学院,宽禁带半导体材料与器件教育部重点实验室,陕西 西安,710071;2. 西安通信学院 基础部,陕西 西安,710106)

sigma-delta(即 ΣΔ)模数转换器(即 sigma-delta ADC)[1-3]采用过采样技术和噪声整形技术降低了对转换器中模拟电路的设计要求,并且此种类型转换器与现代标准CMOS工艺特别兼容,成为实现中低速高精模数转换器的首选转换器,在数字音频、语音处理、电子测量和语音通讯等领域得到广泛应用。sigmadelta ADC由ΣΔ调制器(SDM)和数字抽样滤波器组成。sigma-delta调制器是sigma-delta ADC的核心部分,其结构选择和电路参数设计决定着整个转换器的采样速率和转换精度等主要性能指标。1位和多位ΣΔ调制器(分别指量化器精度或分辨率为1位和多位的ΣΔ调制器)是数字音频领域高精度转换广泛采用的2种方法。1位ΣΔ调制器[4-6]由于采用1位的量化器具有固有的优良的线性特征。然而,在给定过采样率的情况下,1位调制器具有式样噪声(Pattern or idle tones),其分辨率也有限。因此,为得到高分辨率以及减小式样噪声,1位调制器通常采用高阶结构,然而,高阶1位调制器的量化误差间距大,需要具有高压摆率才能快速稳定地运放,但这导致电路对衬底噪声和基准电压的摆动更加敏感。多位ΣΔ调制器[7-9]具有以下优点:(1)量化位数每增加1位,调制器转换精度提高6 dB;(2)多位量化器中的积分步长小,使得运放对摆率和带宽的要求比 1位量化器中运放的要求较低;(3)多位调制器具有多个量化等级使得可以输入较大的信号幅度,同时,由于量化器的量化噪声相关性变小,因此,调制器的式样噪声也小。但多位调制器也存在以下弊端:反馈回路中多位 DAC元件失配会导致信号的谐波失真。为了解决这个问题,多位调制器必须采用动态元件匹配技术[10-12]。本文作者设计了1个内部采用4位量化器的二阶单环 sigma-delta调制器,同时采用CLA(Clocked averaging algorithm)技术提高多位DAC的线性度。为了增强积分器的稳定性,还采用了动态频率补偿技术。模拟调制器处理的信号带宽为 24 kHz,在工作时钟为6.144 MHz、过采样率为128时,调制器信噪比(SNR)为103 dB,调制器输出信号无杂波动态范围为 102 dB。本文从调制器系统结构的选取、各电路模块的设计以及测试结果等进行介绍和讨论。

1 sigma-delta调制器结构

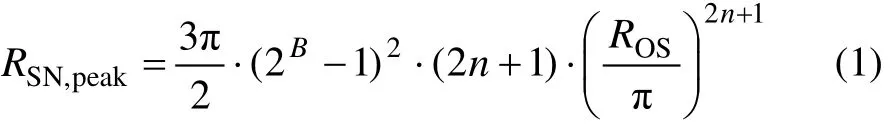

1个过采样率为ROS、内部量化器为B位的n阶调制器的最大信噪比可表示为[1-2]:

其中:RSN,peak为峰值信噪比;ROS为过采样率。

由于单环高阶调制器存在稳定性问题,多级高阶调制器(MASH)结构具有电路复杂及级间泄漏缺点。本文作者采用能够绝对稳定的二阶单环结构,这样还可以减少调制器的子模块数量,从而减小芯片面积和功耗。由于调制器处理音频信号,信号带宽小,可以选择大的过采样率(128),这样,调制器的采样频率为6.144 MHz。为实现设计目标,内部量化器位数确定为4,这时,由式(1)可知最大信噪比可达118 dB,这也给电路的其他噪声留有一定的余量。

调制器结构如图1所示。在传统结构上增加1条由信号输入端到第2个积分器输入端前馈通路(如图1中虚线所示),从而减小第1个积分器的输出幅度,进一步降低了第1个积分器中放大器对摆率和带宽的要求。这样能使放大器的增益进一步增大,由此减小噪声和负载电容,提高调制器的信噪比。

图1中量化器是4位量化器,由于反馈多位DAC中电容器件参数的失配会产生非线性,从而会降低调制器的性能,所以,设计中采用一种动态元件匹配(Dynamic element matching,DEM)技术和CLA技术,以降低这种非线性因素的影响。

2 调制器的电路实现

2.1 调制器电路结构

调制器电路采用开关电容(Switched-capacitor, SC)技术,以全差分电路来实现,从而可以减小时钟馈通、偶次谐波、衬底和电源噪声等电路非理想因素的影响。

图1 ΣΔ调制器的结构Fig.1 High-level sigma-delta modulator topology

图2 调制器的开关电容电路Fig.2 Switched-capacitor circuit of modulator

图2所示为2阶ΣΔ调制器的电路图,包括2个开关电容积分器、1个4位ADC、1个动态元件匹配(DEM)模块以及2个由开关电容阵列实现的多位DAC。

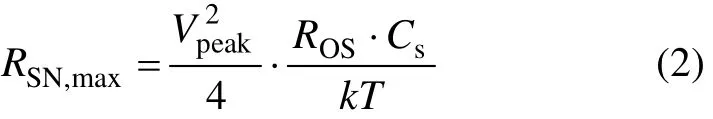

由开关电容构成的全差分式积分器传输函数取决于开关电容网络的相对值,与开关电容网络的绝对值无关。但是,由于实际开关存在导通电阻,SC采样网络会引入开关热噪声(kT/C噪声),如果电容过小,使得开关热噪声比量化噪声大得多,从而成为限制整个系统信噪比的主要因素。尤其是第1级积分器之中的采样电路,其引入的噪声会直接叠加在输入信号上。因此,必须确定积分器的采样电容,使其开关热噪声不影响调制器的性能。电容Cs与系统最大信噪比RSN,max以及过采样率ROS之间的关系[13]为:

式中:Vpeak为输入信号的电位峰值;k为玻尔兹曼常量;T为热力学温度。为了使第1个积分器采样电容以及反馈 DAC中电容阵列所引入的热噪声不影响调制器精度,经过计算,第1个积分器的采样电容取为4.8 pF,DAC电容阵列为4 pF。由于调制器环路的噪声整形功能,第2级积分器的采样噪声得到调制,对系统信噪比的影响大大减小,所以,第2个积分器采样电容以及反馈DAC中电容阵列可以取小些,取第1级积分电路中电容的1/4可满足要求。

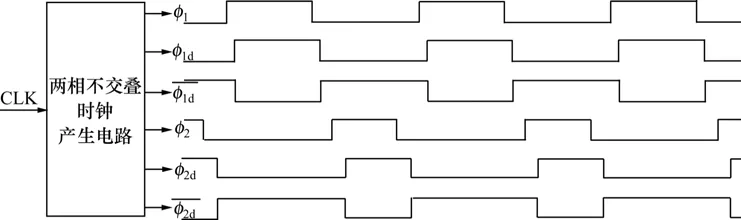

调制器工作电压为5 V,为获得最大的输入输出动态范围,积分器输入输出共模电平设计为相同并等于基准电压,为 2.4 V。调制器的工作频率为 6.144 MHz,由片外提供6.144 MHz时钟信号CLK,并经片上2相不交叠时钟产生电路(图3),产生2个相互不重叠的时钟信号φ1和φ2,以及φ1和φ2的延迟信号φ1d和φ2d,来控制积分器的采样和积分。φ1d和φ2d的利用消除了采样开关的时钟馈通对信号的影响。

2.2 模块电路设计

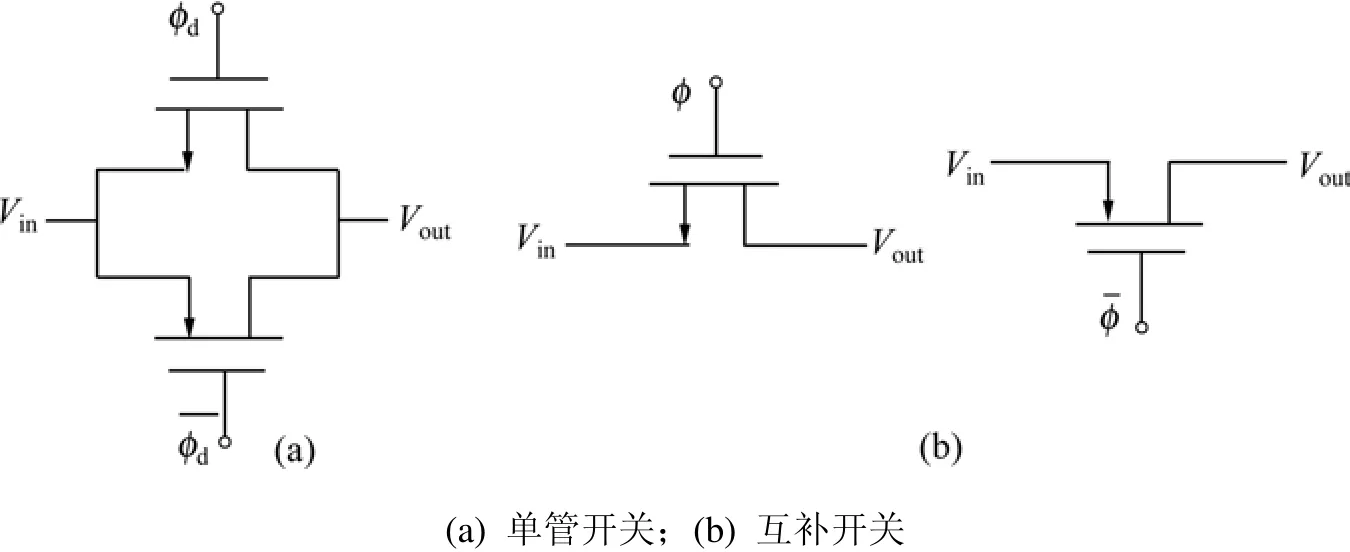

2.2.1 开关设计

开关电路结构如图4所示,采用传输门或者单个MOS管实现。为了减少采样信号受噪声干扰,采样电容采用下极板采样。图 2中受φ1d和φ2d控制的开关一端连接电容的下极板,另一端直接与信号或者与虚地相连。这些开关的热噪声会直接对积分器性能产生较大的影响,因此,这些开关采用传输门实现。传输门开关导通时晶体管工作于线性区,等效导通电阻为NMOS和PMOS管导通电阻的并联,比单个MOS管开关导通电阻小,从而可减小开关热噪声的影响。其他开关对调制器性能影响小,采用单个 PMOS或NMOS管实现。由于系统电源电压为5 V,因此,不需要时钟电压升高电路,由时钟产生电路产生的时钟直接驱动开关中NMOS和PMOS管。

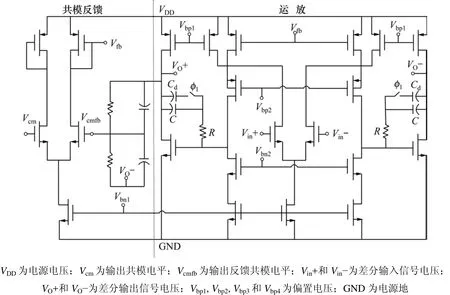

2.2.2 放大器设计

积分器是ΣΔ调制器的主要模块,开关电容积分器由于精度高,易于在深亚微米的工艺中实现,因此,成为设计高精度转换器的首选积分器。开关电容积分器的核心是运算放大器,第1个积分器中两级全差分结构的A类放大器电路如图5所示。采用带连续时间共模反馈的折叠式共源共栅结构,其差分输入和差分输出结构以及共模负反馈网络可以有效地抑制输出共模电平的变化,从而使电路具有更强的稳定性。

图3 时钟方案Fig.3 Clock scheme

图4 开关电路结构Fig.4 Circuit structure of switches

图5 放大器电路Fig.5 Amplifier schematic

放大器的性能参数指标主要包括开环直流增益、单位增益带宽、压摆率以及输出摆幅。其中,开环直流增益和单位增益带宽主要影响积分器的增益误差和极点误差,压摆率决定积分器的建立速度,输出摆幅则决定积分器的输出范围。为了增大输入、输出摆幅,使输入、输出共模电平同为2.4 V(接近1/2电源电压,2.5 V),并与基准电压相等,这样也可简化积分器设计。放大器采用RC频率补偿,并在补偿电容C上并联1个开关电容Cd进行动态补偿。在采样相时,运放工作接近全负反馈状态,开关电容Cd接入,使得运放的相位裕度增大,稳定性增加;在积分相时,将开关电容Cd断开,增加运放的单位增益带宽和摆率,以减小积分器积分泄露和输出建立时间。放大器的性能如表1所示,其中:运放引入的误差对调制器整体性能的影响可以忽略。第2级积分器中放大器的结构与第1级中的相同。由于其负载电容比第1级积分器中放大器负载电容小,并且引入的噪声被一级积分器整形,所以,第2个运放性能要求比第1个的运放性能稍低。

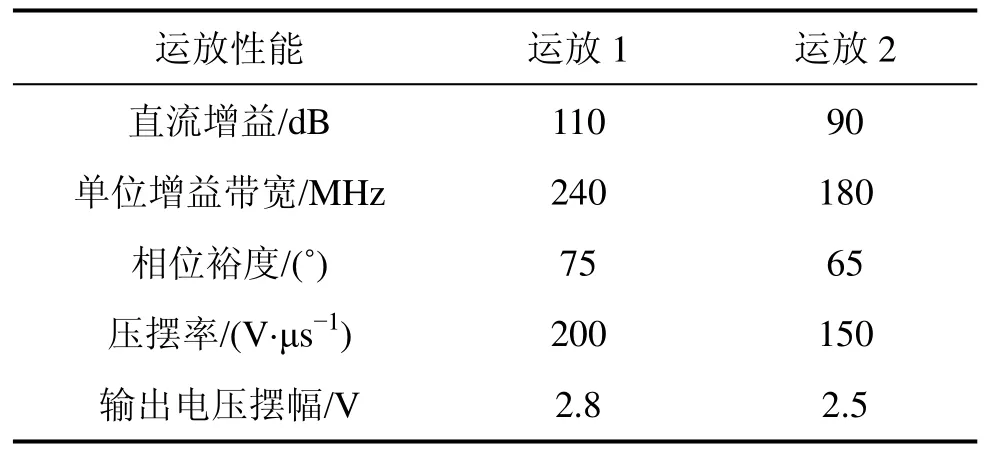

表1 放大器性能参数Table 1 Amplifier performances

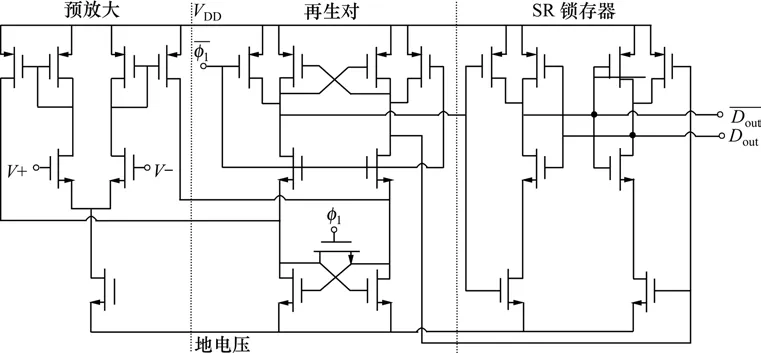

2.2.3 量化器的实现

多位ΣΔ调制器的量化器通常是1个快闪ADC。4位量化器的电路结构如图6所示。采用Mid-Tread量化方式,1/2满刻度电压通过电阻分压产生8个正的参考电压等级,通过开关电容方案可以产生8个负的参考电压等级,差分信号通过开关电容采样实现与参考电压相减,然后,送入差分比较器进行比较,比较结果构成16等级温度计码。温度计码经编码器转化为5线4位二进制码输出到调制器外。

量化器设计的重点是比较器,比较器失调电压大会导致量化器输出产生气泡错误。这种错误会产生大的样点间反馈间距,从而使积分器输出电压不完全稳定。为了减小比较器的输入失调电压,采用预放大锁存比较器[14-16],预放大同时也减小了踢回噪声对积分器输出的影响。比较器电路结构如图7所示,该结构包含1个差分输入的预放大放大器、2个再生对和1个 RS锁存器。在保持相,预放大器的输出被限制在亚稳定点,同时,PMOS再生对也被重设为电源电压VDD。在锁存相,2个再生对打开产生1个数字输出,并被锁定。

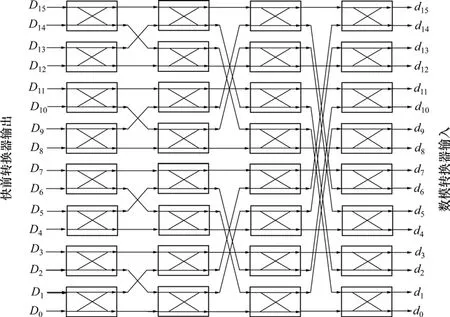

2.2.4 DEM模块设计

多位调制器最主要的缺点是对反馈 DAC的非线性误差敏感。DAC非线性误差主要来源于内部电容阵列间的失配。由这种非线性误差引入的噪声是直接叠加在输入信号之上的,对整个调制器信噪比的影响十分明显,所以,必须采用动态元件匹配(DEM)技术,来减少DAC的非线性误差。本文采用CLA技术[12],将反馈路径打乱,减小非线性误差。实现CLA的DEM模块如图8所示。量化器的输出温度计码的反馈路径经DEM混乱后再送入DAC。DEM中每一个子模块根据输入的1对信号间的关系确定传输路径,当2个信号不同时则改变传输路径输出,各模块输出信号重新组合,送入下一级模块进行重复操作,共进行4次路径的选择,使温度计码信号伪随机送入DAC,从而使得 DAC的电路中由固定失配引起的非线性误差被CLA转变为一个宽带的噪声,这样,分布在信号带内的噪声能量减小,由此对调制器的性能影响减弱。

图6 4位量化器的电路结构Fig.6 Circuit structure of 4-bit quantizer

图7 预放大闩锁比较器Fig.7 Latch comparator with preamp

图8 采用CLA技术的DEM模块Fig.8 DEM module with CLA

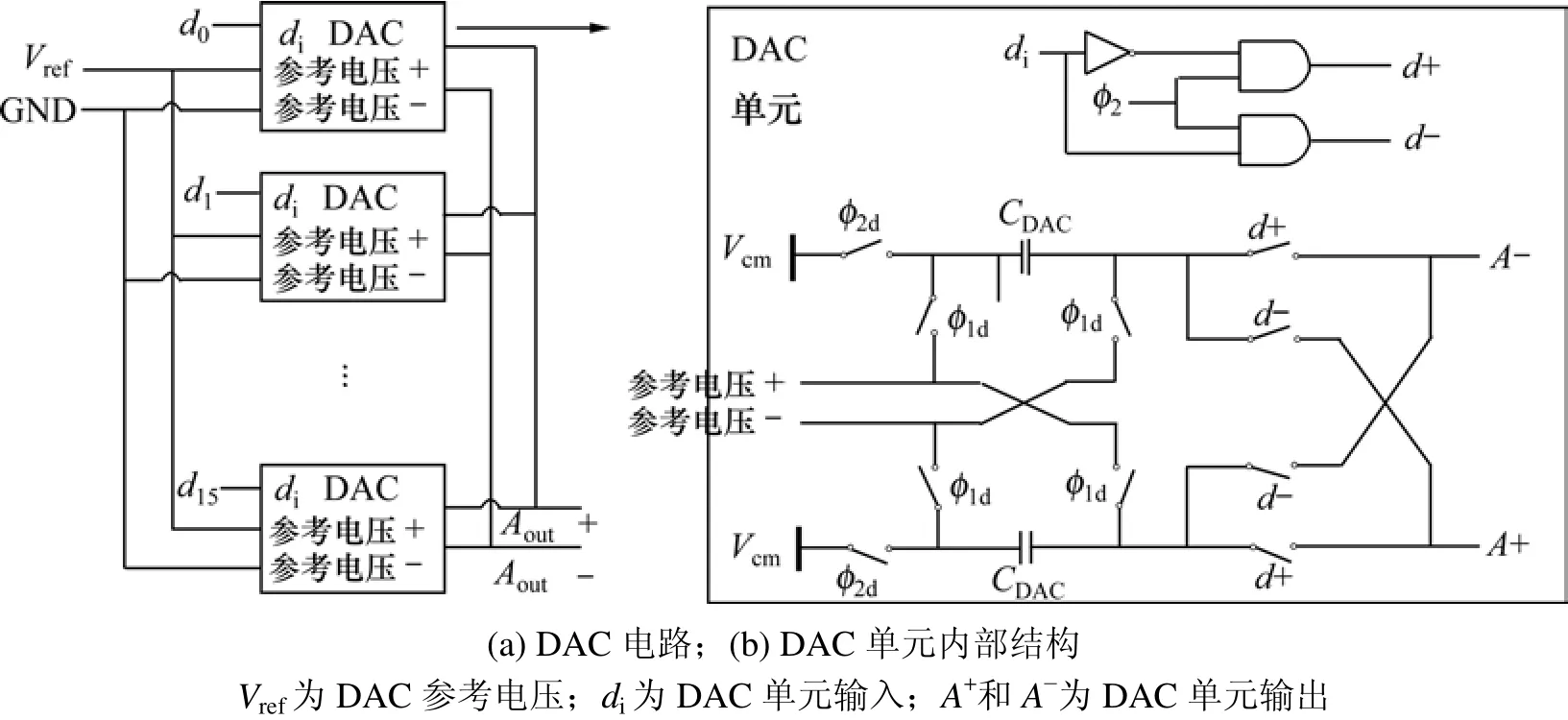

图9 DAC电路Fig.9 DAC circuit topology

2.2.5 反馈DAC设计

2个DAC都采用开关电容实现。2个DAC结构如图9所示,它们都由16个相同的DAC单元组成。2个DAC除各自DAC单元中电容单元不同外,结构完全相同。在采样相,DAC单元内2个电容各自充电电量为C×Vref和-C×Vref(其中:C为电容,Vref为参考电压);积分相根据反馈信号决定2个电容与积分器的哪一个输入端相连,与同一积分输入端相连的 16个CDCA电容经电荷代数求和实现反馈数字信号到模拟电压的转换,同时与输入信号相减并完成积分过程。

3 集成电路版图设计

集成电路版图设计对实现集成电路性能是至关重要的,它决定着电路尤其是模拟集成电路设计的成败。本文作者对调制器版图进行设计,为了保证差分放大器精确匹配,采用对称和平衡技术进行版图设计,特别是输入差分对还使用分半交叉以达到高的匹配精度。为了减弱电源对电路的干扰,调制器内部采用 2路电源线供电:一路供给处理数字信号的 DEM单元和2相不交叠时钟产生电路;另一路供给2个积分器。对这2部分电路进行严格隔离。比较器输出信号高、低电平的快速转换,会对积分器产生干扰,因此,对比较器和积分器间也进行隔离。为了去除电源抖动的干扰,在电源线之间还加入一些MOS电容。

4 结果分析

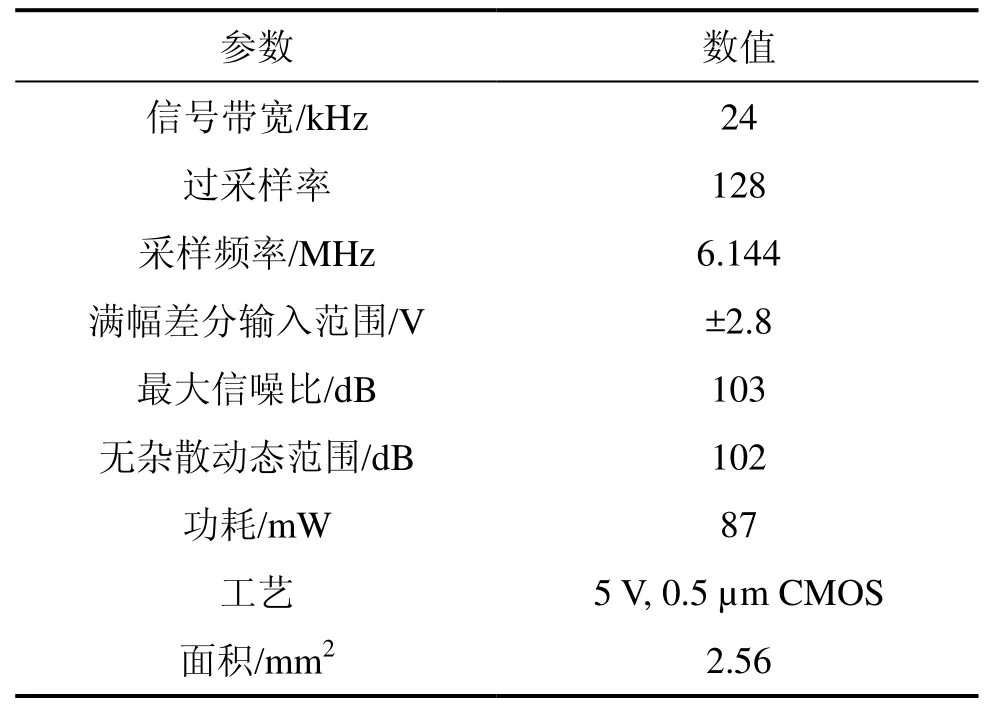

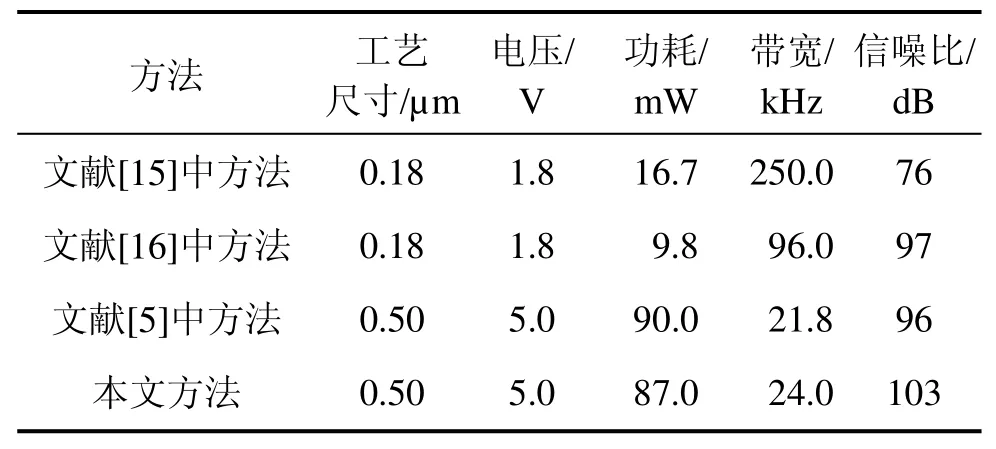

本设计采用0.5 µm CMOS工艺实现,整个芯片包括调制器电路,焊点总面积为2.56 mm2。在5 V工作电压下,功耗为87 mW。在过采样频率为6.144 MHz,过采样率为128时,给调制器输入幅度为-1 dB、频率为20 kHz的差分正弦信号,并将调制器输出结果进行采集,送入MATLAB中采用16 384点快速傅里叶变换(FFT)分析,测得调制器的信噪比为 103 dB,输出信号无杂散动态范围为102 dB,有效精度约为17位。调制器芯片主要性能参数如表2所示,本文研究结果与相关文献结果的对比如表3所示。可见:调制器分辨率精度达到更高的信噪比,与同尺寸为 0.5 µm的CMOS工艺[5]相比功耗也有所降低。

表2 调制器芯片性能Table 2 Performance and specification of modulator

表3 sigma-delta调制器性能的对比Table 3 Performances of some sigma-delta modulators

5 结论

(1)设计了 1个高精度多位 ΣΔ(sigma-delta)调制器。该调制器采用4位量化器提高调制器的精度,利用CLA技术增加多位DAC的线性度,使用动态频率补偿技术增强积分器的稳定性。

(2)调制器用0.5 μm CMOS工艺实现,芯片总面积为2.56 mm2。在5 V电源电压下工作,当输入信号带宽为24 kHz,过采样频率为6.144 MHz,过采样率为128时,调制器的信噪比(SNR)可达103 dB,功耗为87 mW。

(3)该调制器与数字抽取滤波器可构成高精度ΣΔ模数转换器,应用于数字音频领域。

[1]Candy J C, Temes G C. Oversampling delta-sigma data converters theory, design and simulation[M]. New Jercy: IEEE Press, 1992.

[2]Schreier R, Temes G C. Understanding delta-sigma data converters[M]. New Jercy: IEEE Press, 2005.

[3]Schreier R. An empirical study of higher-order single-bit delta-sigma modulators[J]. IEEE Trans Circuits Syst II, 1993,40(8): 461-466.

[4]Zierhofer C M. Adaptive sigma-delta modulation with one-bit quan-tization[J]. IEEE Trans on Circuits and Sys II, 2000, 47(5):408-415.

[5]CHEN Lei, ZHAO Yuan-fu, GAO De-yuan, et al. A 16-bit stere audio ΣΔ A/D Converter[J]. Chinese Journal of Semiconductors,2006, 27(7): 1183-1188.

[6]Geerts Y, Steyaert M, Sansen W. Design of multi-bit delta-sigma A/D converters[M]. Boston: Kluwer Academic Press, 2002.

[7]LU X. J. A novel signal-predicting multibit delta-sigma modulator[C]//Proc of the IEEE Int Conf on Electronics, Circuits and Sys. Tel-Aviv, Israel, 2004: 105-108.

[8]Leung B H, Sutarja S. Multi-bit sigma-delta A/D converters incorporating a novel class of dynamic element matching techniques[J]. IEEE Trans Circuits Syst II, 1992, 39 (1): 35-51.

[9]Chen F, Leung B H. A high resolution multibit sigma-delta modulator with individual level averaging[J]. IEEE Journals of Solid State Circuits, 1995, 30(4): 453-460.

[10]Yasuda A, Tanimoto H, Lida T. A third-order Δ-Σ modulator using second-order noise-shaping dynamic-element matching[J].IEEE Journals of Solid State Circuits, 1998, 33(12): 1879-1886.

[11]Brooks T L, Robertson D H, Kelly DF, et al. A cascaded sigma-delta pipeline A/D converter with 1.25 MHz signal bandwidth and 89 dB SNR[J]. IEEE Journals of Solid State Circuits, 1997, 32(12): 1896-1906.

[12]Kwan T, Adams R, Libert R. A stereo multibit ΣΔ DAC with asynchronous master-clock interface[J]. IEEE Journals of Solid State Circuits, 1996, 31(12): 1881-1887.

[13]Hauser M W, Broderson R W. Circuit and technology considerations for MOS delta-sigma A/D converters[C]//Proc IEEE International Symposium on Circuits and Systems. San Jose, USA, 1986: 1310-1315.

[14]吴笑峰, 刘红侠, 石立春, 等. 新型高速低功耗CMOS动态比较器的特性分析[J]. 中南大学学报: 自然科学版, 2009, 40(5):1354-1359.WU Xiao-feng, LIU Hong-xia, SHI Li-chun, et al. Characteristic analysis of an high speed low power CMOS dynamic comparator[J]. Journal of Central South University: Science and Technology, 2009, 40(5): 1354-1359.

[15]陈建球, 任俊彦, 许俊, 等. 一个用于GSM的80 dB动态范围Σ-Δ调制器[J]. 半导体学报, 2007, 28(2): 294-301.CHEN Jian-qiu, REN Jun-yan, XU Jun, et al. An 80 dB dynamic range Σ-Δ modulator for a GSM system[J]. Chinese Journal of Semiconductors, 2007, 28(2): 294-301.

[16]CAO Ying, REN Teng-long, HONG Zhi-liang. A 16 bit 96 kHz Chopper-Stabilized sigma-delta ADC[J]. Chinese Journal of Semiconductors, 2007, 28(8): 1204-1210.