基于Virtex-5 FPGA的系统监测器设计

刘庆良,卢荣军,李建清

(东南大学 仪器科学与工程学院,AMS研究中心,江苏 南京 210096)

FPGA广泛应用于通信、数字信号处理、工业控制、航天航空等领域。FPGA作为应用中的基础或核心模块,密切监测其片上以及周围的物理环境。Xilinx Virtex-5 FPGA系列器件自带系统监测器模块。设计人员可利用该监测器模块设计能方便监测其片上温度和供电电压的监测系统;另外,外部传感器与其外部模拟输入通道互联,该监测系统能够监测多达17个外部物理参数。

在数字多普勒接收机中,利用Xilinx Virtex-5系列XC5VSX50T器件内置的系统监测器(System Monitor)模块设计一个系统监测器,用于监测板上器件工作时的温度和供电电压。Virtex-5 FPGA器件中的系统监测器模块提供报警、自动定序和数据平均等常规功能,因此,根据实际需要就可轻松设计满足要求的系统监测器。

图1 Virtex-5系统监测器模块结构图

1 Virtex-5系统监测器模块

1.1 系统监测器模块架构

图1给出Virtex-5系统监测器模块[1]的结构。它主要由A/D转换器、片上传感器、寄存器文件接口、通信端口等组成[2]。

图1中,10位,200 kS/s的A/D转换器是该系统监测器模块的核心,其模拟输入范围为0~1 V,10位分辨率下,该A/D转换器能够处理精度约为1 mV的输入电压。系统监测器模块内置温度传感器和供电传感器,用于监测器件温度和电压。温度传感器产生与器件温度成比例的电压输出,供应传感器获得系统监测器的电源信息,它们通过模拟多路复用器与A/D转换器相连。A/D转换器将这些传感器上的测量值转换为数字量,然后把转换后的测量结果写入对应的状态寄存器。 此外,VP,VN,VAUXP[15:0],VAUXN[15:0]17 对外部模拟输入通道,经多路复用器接入,输入测量值经A/D转换器转换为数字量后,转换结果写入到状态寄存器。这17个外部模拟通道外接相应传感器后,可用于监测片外的物理参数,如板上其他器件的温度。

该系统监测器模块共有128个16位的寄存器 (00h~7Fh),前 64 个为状态寄存器(00h~3Fh),后 64个为控制寄存器(40h~7Fh)。状态寄存器存储片上传感器和外部模拟输入通道所监测的物理参数经A/D转换器转换的数字量,状态寄存器只能读操作,不能初始化。状态寄存器还能存储器件最近一次上电或系统监测器模块最近一次复位后片上传感器所监测物理参数的最大值或最小值。A/D转换器转换后的10位数字量存放在寄存器的最高10位。而控制寄存器用于设置系统监测器的操作模式、操作功能以及所监测参数的阈值。控制寄存器通过通信端口读写操作,控制寄存器主要分为配置寄存器,测试寄存器,顺序寄存器和警告寄存器。

系统监测器模块的通信端口由动态再配置端口(DRP)、JTAG TAP端口以及状态和控制端口组成。通过FPGA的架构接口,即DRP访问系统监测器模块的状态寄存器和控制寄存器,而且可在任何时刻动态配置和读取相应寄存器。另外,Virtex-5系统监测器模块还具有另一个功能,即通过JTAG TAP访问系统监测器模块所有功能。系统监测器模块允许通过JTAG TAP控制器和DRP双重访问,并提供相应的仲裁方案管理可能出现的竞争现象。状态端口指示A/D转换器的工作状态和报警输出,如BUSY信号为高电平时,A/D转换器进行数据采集转换;ALARM[2],ALARM[1]和 ALARM[0]分别对应VCCAUX,VCCINT和温度报警输出。控制端口为相关操作模式提供控制信号。

1.2 系统监测器模块的工作原理

系统监测器模块的核心A/D转换器可工作在连续采样或事件驱动的时序模式下[3]。连续采样模式指A/D转换器在当前转换周期结束时自动开始新的转换;事件驱动模式指在当前转换周期结束后,用户必须通过相关的控制端口提供的控制信号初始化下一个转换操作。通过设置配置寄存器0(40h)设定A/D转换器的工作模式。

系统监测器的模拟输入为单端信号或差分信号。A/D转换器专用输入VP和VN以及辅助模拟输入VAUXP[15:0]和VAUXN[15:0]都由单端源或差分源驱动。由于辅助模拟输入带宽较低,因此必须在差分模式下,差分源才能驱动模拟输入。设定配置寄存器0(40h)可选择模拟输入模式。在嘈杂的数字环境中,A/D转换器采用差分采样的模拟输入能够减少共模噪声信号的影响,进而改善A/D转换器性能[4]。

系统监测器模块包含通道定序器,测量平均、最大值和最小值,内部传感器自动报警以及传感器和A/D转换器校准等功能。根据设计应用的要求设置相应的寄存器,选取所需的系统监测器模块功能。

系统监测器模块通过模拟多路复用器将片上或外部的监测对象信息输入到A/D转换器,A/D转换器再将测量值转换为数字量,并输入到相应的寄存器。同时,与相应最大最小值状态寄存器的值相比较,该测量值若大于最大值或小于最小值,则更新最大最小值状态寄存器的值。当最大最小值状态寄存器的值大于相应控制寄存器所设置的阈值时,触发其对应警告输出。另外,当片上的温度大于出厂设定的125℃时,则产生过热警告。

1.3 时钟设置

系统监测器模块的A/D转换器需要一个5 MHz范围内的时钟源,该时钟源可由内部时钟或外部时钟提供。外部时钟提供时钟源是通过时钟控制端口DCLK接入。由于内部时钟可分频,因此,8~200 MHz范围内的时钟都可作为时钟源。当未检测到外部时钟源时,系统监测器模块为DCLK提供一个50 MHz的内部时钟晶振,用作时钟源。

2 系统监测器的应用设计

该系统监测器用于监测片上温度和VCCAUX。片上温度的上限值为85℃,警告复位触发温度是60℃;VCCAUX的阈值范围是2.375~2.625 V。图2为该系统监测器设计原理图。

图2 系统监测器设计原理图

该设计采用一个20 MHz的外部时钟作为系统监测器的时钟源。 CHANNEL[4:0]总线连至 DADDR[4:0],DADDR[6:5]连至逻辑0;DEN连至EOC输出;DRP写使能信号DWE和系统监测器复位信号RESET连至逻辑0。BUSY信号用于指示A/D转换器状态,监测A/D转换器转换率。ALM[2]和ALM[0]信号用于监测片上温度和VCCAUX的状态。当片上温度或VCCAUX超出设定阈值时,与其对应的tem_alarm和vccaux_alarm将产生高电平警告。温度或VCCAUX的测量值可在输出result[9:0]上检测。

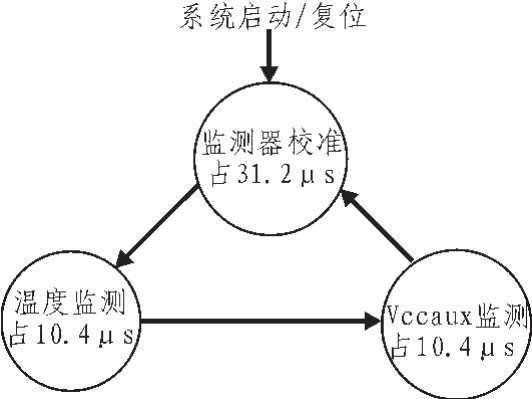

该设计中将通道CHANNEL[4:0]连接到DRP的地址端口DADDR[4:0],作为DRP的地址输入。EOC连接到 DRP的使能输入端口DEN。当EOC变为高电平时,DEN有效,锁定DADDR地址,即为当前通道的地址,将当前监测的测量值输出到DO总线。该设计中的系统监测器的工作状态机如图3所示,各工作状态按配置顺序自动切换。

图3 系统监测器的工作状态机

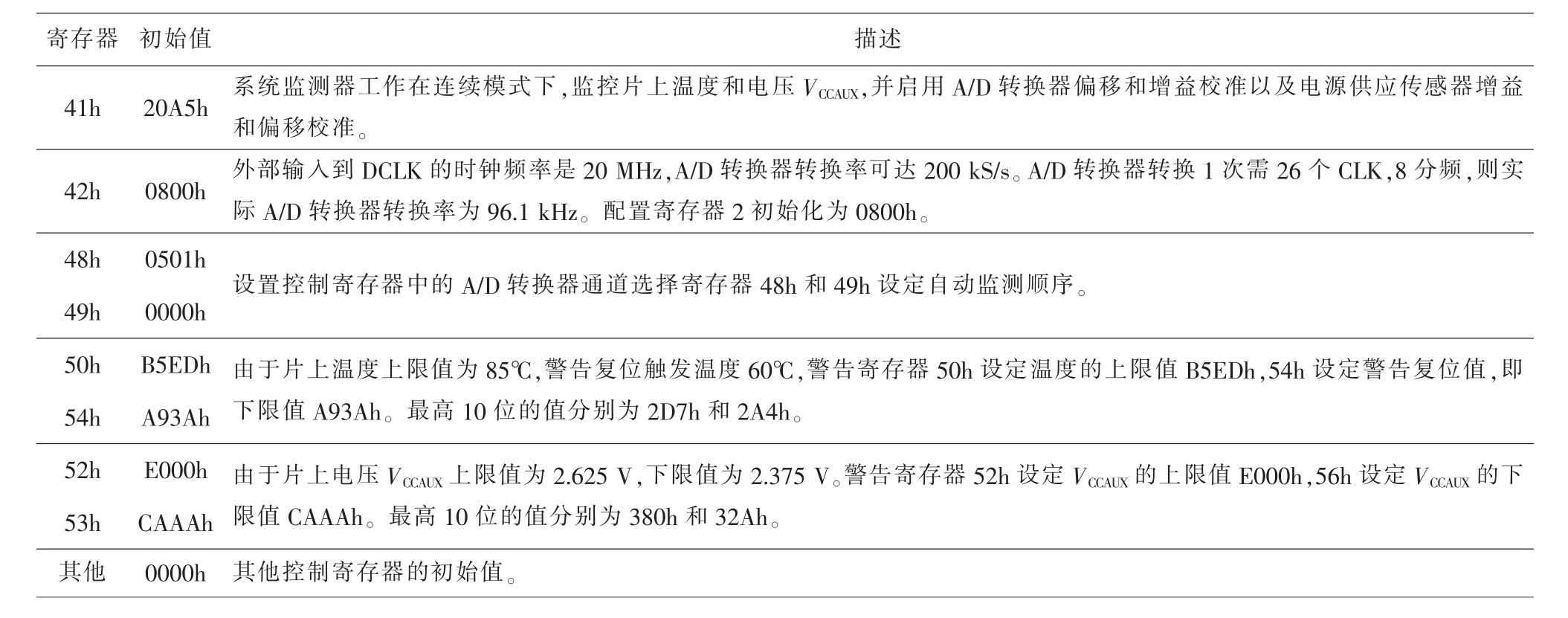

根据设计要求,计算系统监测器的控制寄存器的参数值,对其控制寄存器进行初始化。具体参数设置和描述见表1。

表1 系统监测器的控制寄存器初始化值

该设计选用Virtex-5系列中的XC5VSX50T器件,开发平台为Xilinx ISE10.1i[5]。在ISE中可用System Monitor模块进行设计,也可采用基于System Monitor CORE Generator进行图形化参数设计。这里采用前一种方法。根据设计要求,用Verilog HDL以及ISE提供的系统监测器模块编写描述设计行为的硬件描述语言代码[6],并按上述初始值初始化对应的控制寄存器。

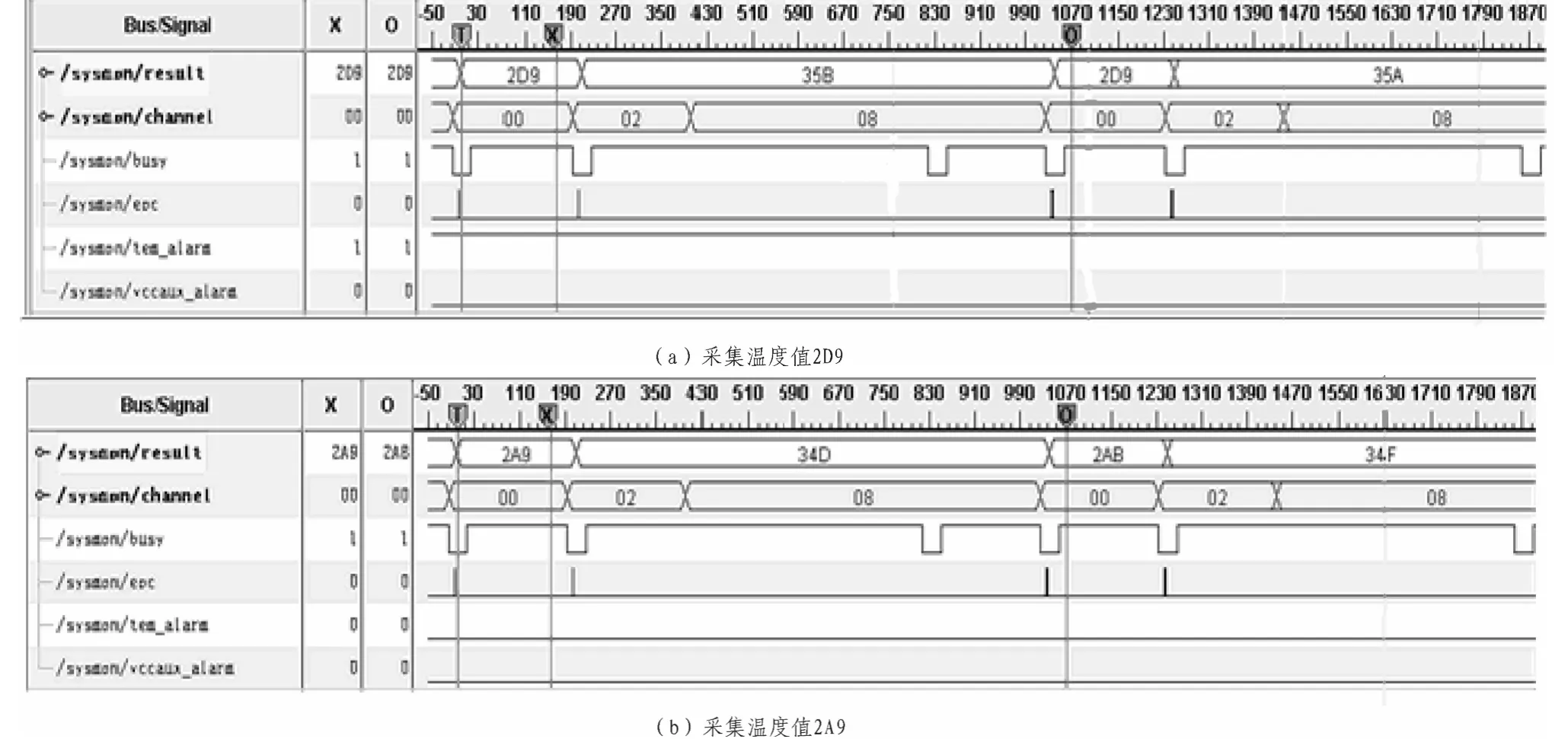

根据系统监测器提供的激励文件格式,为设计编写模拟激励文件,然后在ModelSim平台中对该设计进行仿真,其仿真结果如图4所示。

图4 设计仿真结果

图4中,channel显示通道按设定的顺序进行监测。第1个转换是校准通道08,占31.2 μs;第2个转换是温度传感器通道00,占 10.4 μs;第 3 个转换是 VCCAUX传感器通道 02,占 10.4 μs。在每次转换结束时eoc输出一个时钟周期的高电平,该高电平使DRP的使能端口有效,此时锁定地址,将对应状态寄存器值输出到DO总线,最高10位为A/D转换器转化数字量,输出到result上。当通道处在校准通道08时,DO总线对应输出值是前一通道对应寄存器的值,在该设计中为VCCAUX传感器通道02对应的控制寄存器的值。当检测到对应监测对象的测量值超出设定的阈值,tem_alarm或vccaux_alarm输出为高电平警告。如图4中Cursor5光标指示的00通道,此时测量值为2B4h,大于初始化的警告复位触发温度 (60℃)对应的值2A4h,所以此时tem_alarm为高电平警告输出。

3 硬件调试

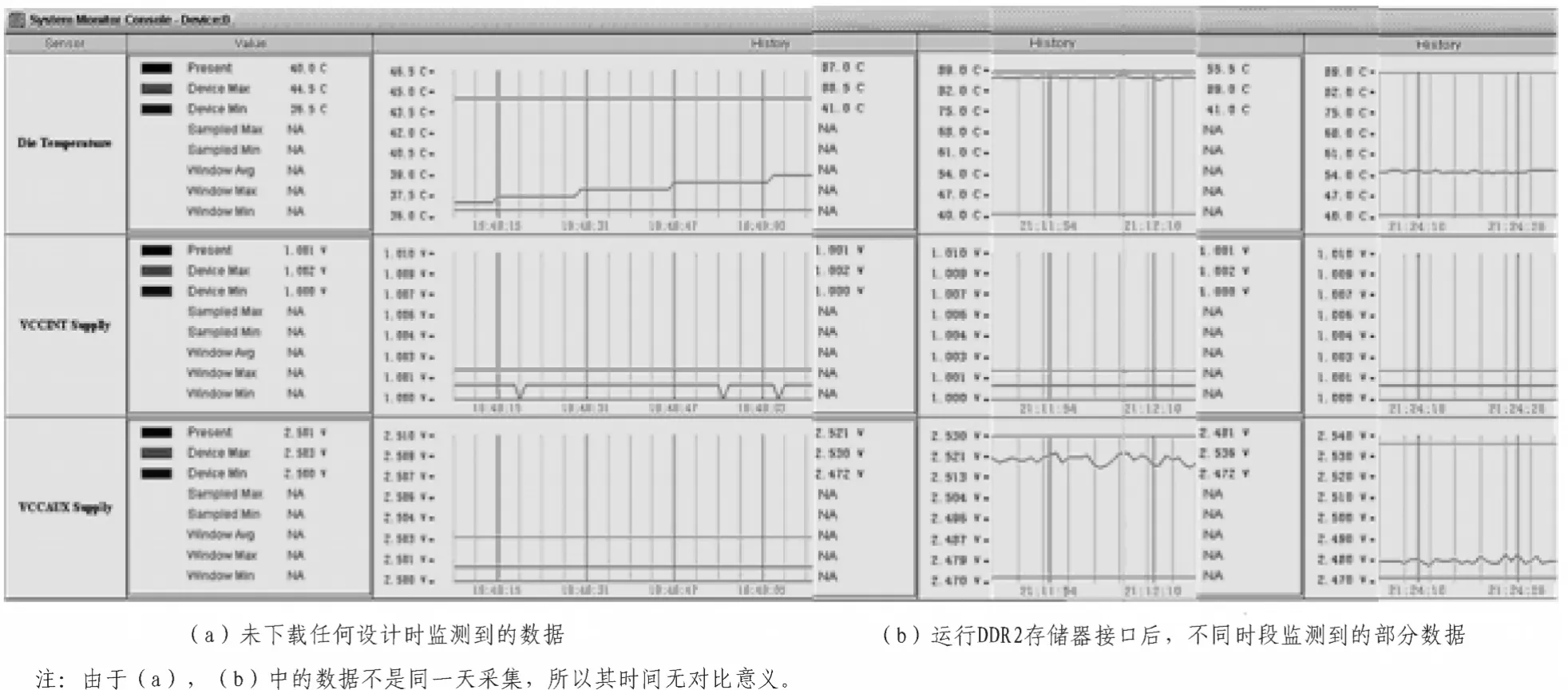

3.1 JTAG接口访问

通过JTAG TAP访问系统监测器的所有功能,实现模拟测试和访问。ChipScope分析器可访问系统监测器,而且这种访问功能还能集成到其他JTAG测试和编程环境中。图5为器件上电在未下载任何设计前监测到的温度和供应电压的数据以及下载DDR2存储器接口设计并运行后,不同时段监测到的温度和供应电压的数据。图5(a)中未下载任何设计之前,器件温度和供应电压都比较稳定。图5(b)中在运行DDR2存储器接口后,器件功耗增加,温度不断升高且供应变压随着温度的升高波动越来越大;对器件散热处理,观测到温度降低后,电压波动变小;取消散热处理后,温度升高,电压波动变大。监测器件的温度和供应电压等有重要意义。

3.2 设计调试

在应用设计实现之后,将生成的位流文件载入器件中,配置器件。然后,通过ChipScope观测系统监测器的内部信号的值。图6显示器件在下载DDR2存储控制器接口设计并运行后,ChipScope中采集到的温度和VCCAUX数值。首先设置温度警告有效触发,即温度警告为高电平时,开始采集数据,图6(a)采集到温度传感通道监测值为2D9,大于警告温度上限2D7;然后设置温度警告为低电平触发,即复位警告温度有效后开始采集数据,对器件降温,图6(b)采集到温度传感通道监测到值为2A9,小于警告温度上限2D7。而供应电压在监测范围内,故无警告输出,vauxcc_alarm恒为低电平。

图5 XC5VSX50T器件的温度和供应电压监测

图6 实例设计的内部信号监测

4 结束语

FPGA作为应用设计的基础或核心模块,监测与其相关的物理参数非常重要,如通过监测片上温度,确保FPGA工作在器件允许的温度范围内,避免器件因过热而损坏[7]。在数字多普勒接收机中设计系统监测器,用于监测接收机工作时FPGA器件(XC5VSX50T)的温度和供应电压,使其工作在允许的温度和供应电压范围。另外,通过外部传感器,系统监测还可用于监测17个外部的物理参数。Virtex-5 FPGA系列的器件集成了系统监测器模块,为该系列器件在实际应用中实现内外部物理对象的监测提供一种简单而高效的解决方案。

[1]Xilinx公司.Virtex-5 FPGA system monitor[DB/OL].2009.http://www.xilinx.com/support/documentation/user_guides/ug192.pdf.

[2]Xilinx 公司.Virtex-5 FPGA user guide[DB/OL].2009.http://www.xilinx.com/support/documentation/user_guides/ug190.pdf.

[3]Anthony Collins.利用Virtex-5系统监控器加强系统管理和诊断[J].半导体器件应用,2008(12):111-112.

[4]田 耘.无线通信FPGA设计[M].北京:电子工业出版社,2008.

[5]孙 航,胡灵博,于联锋.Xilinx可编程逻辑器件应用与系统设计[M].北京:电子工业出版社,2008.

[6]Samir PalnitKar.Verilog HDL数字设计与综合[M].北京:电子工业出版社,2004.

[7]Clive“Max”Maxfield.FPGA设计指南[M].北京:人民邮电出版社,2007.