DisplayPort像素分析卡的研究

邢志伟

(哈尔滨工业大学 深圳研究生院,深圳 518055)

0 引言

DisplayPort是一种新型的显示接口标准,由于其相对DVI/HDMI来说具有高带宽、整合性好、内外接口通吃、相关产品设计简单、高度可扩展性、内容保护技术更可靠等技术上的明显优势,其应用范围也越来越广泛。

但是目前对于DisplayPort信号进行测试的手段还比较简单,主要依靠示波器对信号的测量进行眼图分析等处理对信号传输质量进行简单的评判。本文介绍了DisplayPort像素分析卡的研究,提出了一种全新的测试手段。它针对数字信号的特点,对其传输的每个像素的每一位进行分析,不仅可以检测出信号传输过程中出现的错误,甚至可以将错误精确定位到哪一条lane、哪一个像素。

1 硬件设计

DP像素分析卡的硬件电路主要由DP接口模块、PCI接口模块、DDR模块、主控FPGA模块以及相应的系统电源电路模块等部分组成。其结构框图如图1所示。使用时将本测试卡插到PC机主板的PCI插槽上,同时将DP输入接口与显卡的DP输出接口用DP数据线连接起来,之后在PC端启动驱动与控制程序就可以对其进行操作了。

由于我们要测的是DP数据在打包生成和传输时有可能出现的错误,因此就要求DP PEA必须保证板卡上数据解析及其传输有非常高的可靠性及稳定性,同时由于DP数据的传输速率达10.8Gbps,因此对保证信号完整性有非常高的要求。在线路布局时进行了周密设计考虑[1,3]。

图1 DP像素分析卡结构框图

1.1 反射的抑制

1)保证信号在整个路径传播时所感受的瞬态阻抗不变,每条信号线都具有完整的返回路径,并且以地平面做为高速信号线的参考平面;

2)尽量减少传播路径上的过孔数量[2];3)对信号线进行端接。

1.2 串扰的抑制

抑制串扰主要是减少多个信号路径和返回路径间的互容和互感。PEA布线时主要采取了以下措施[4]:

1)保持相邻信号路径的间距至少为线宽的3倍;

2)使表面线条的耦合长度尽可能短,对于远端串扰严重的耦合长度较长的传输线采用带状线布局;

1.3 传输线延时的控制

1)DP 主链路差分对间小于5ps的不对称以保证DP spec的要求;

2)DP接收芯片输出像素数据小于20ps的不对称设计

3)Memory Clock、地址、数据、DQS、DQM信号线间等长设计,并且保证同数据线间具有相同的拓扑结构;

4)各差分线间小于1ps的等长设计。

1.4 电磁干扰的抑制

减小电磁干扰的主要策略为减小驱动共模电流的电压,增大共模电流路径的阻抗,屏蔽和滤波[4]。

1)使所有布线与板子边缘的距离至少为线宽的5倍;

2)对高速敏感数据线采用带状线布局,将高速或大电流器件放大离I/O接口尽量远的地方;

3)在芯片附近放置足够的去耦电容,使电源平面和地平面相邻并尽可能接近,尽可能使用更多的电源平面与地平面对;避免封闭出现谐振;

2 主控模块程序设计

DP像素分析卡中的主控模块FPGA是整个系统功能实现的核心,它实现了系统与外界PCI接口、DP接收器以及DDR的通信和控制,同时也实现了核心功能逻辑。其程序总体架构如图2所示。

图2 主控模块FPGA程序模块架构图

其主要功能模块与其功能为:

1)时钟同步模块。为系统中的其他模块提供同步的时钟输出。

2)DP数据接收模块。其主要功能为接收来自DP接口的图像信息数据。

3)DP数据分析模块。它实现了DP传输数据的分析验错。它从DDR中读出预存的参考图像数据以及当前错误计数数据,将接收到的DP图像数据与参考图像数据按位异或,如有错误产生则累加至相应的错误计数数据,将更新后的error计数数据写入DDR中。

4)PCI FIFO模块。它接收PCI接口输入的控制数据等并根据设计的通讯协议对其进行解析并分发到相应的模块,同时也将系统各模块的运行状态及结果发送给PC端。

5)MBIST检测模块。它实现了内存的自检测,负责实现存储器缺陷检测解决方案。

6)DDR FIFO模块。它是系统与DDR通信的输入输出FIFO,负责管理DDR数据的输入和输出。同时,它内部实现了几个状态机,负责调试协调其它与DDR读写相关的功能模块的运行,包括主状态机、读状态机、写状态机、数据获取状态机、数据分析状态机、MBIST检测状态机。

7)CROSSBAR通路选择模块,本系统中很多功能模块都需要对DDR进行读写操作,但DDR引脚并不能同时连接到多个模块上,因此设计了此模块决定当前内存读写操作应该连接到哪个功能模块。

8)PCI通信模块。负责接受PCI输入的控制命令及数据,同时将系统运行产生的状态及结果数据发送到PCI。

9)DDR通信模块。它实现了对DDR的读、写操作控制。

3 实验结果

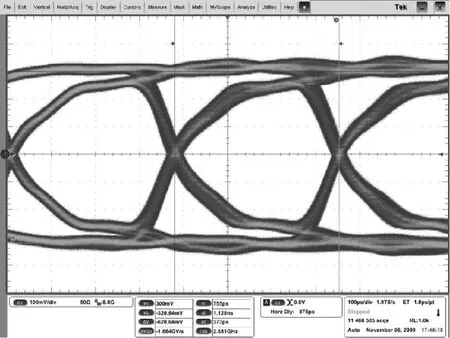

对实际DP信号进行眼图分析的波形如图3所示。可以看出,信号眼图张开得相当好,其眼高、眼宽、信号jitter等均满足DP协议标准。系统信号完整性设计满足需求。

对主控模块程序的逻辑验证由PCI配置与信号生成文件、DP数据生成模型文件、DDR模型文件等实现。PCI配置与信号生成文件按系统实际工作流程生成控制系统工作的各信号并发送给FPGA程序。DP数据生成模型生成DP图像数据与DP格式数据信号, DDR模型文件实现了DDR读、写等操作。

图3 DP信号2.7Gbps时信号眼图

生成参考图像数据及其地址并写入缓存时各相关信号波形如图4所示。生成算法为从0开始递增。可以看到,pci_test_data_reg和pci_test_addr_reg分别为生成的参考图像数据及其地址。

图4 生成参考图像数据相关信号波形图

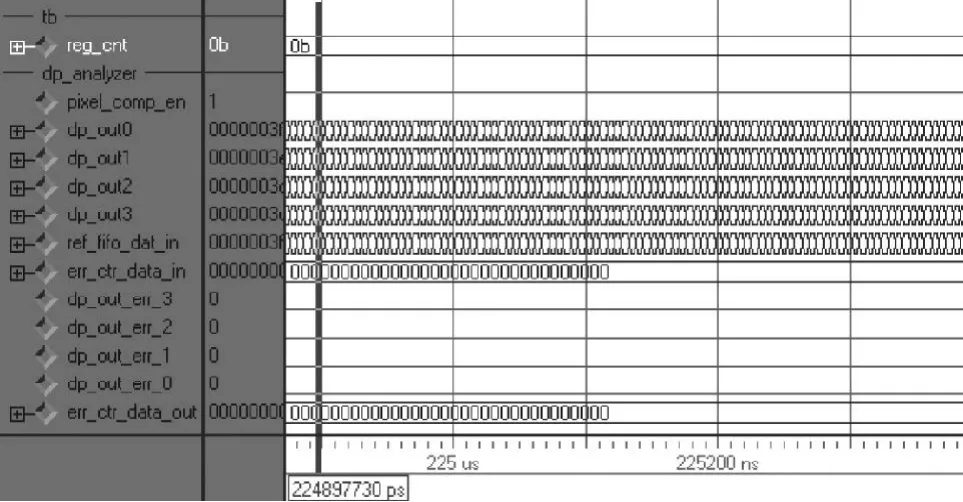

图5所示为DP数据分析模块运行时各相关信号的波形图。可以看出,当DP数据传输过程中没有错误发生时,系统判断出错误数为0。

图5 DP数据比较分析相关信号波形图

4 结论

本文详细分析了DP像素分析卡的硬件电路设计和FPGA程序的设计,实验结果显示:硬件电路设计部分信号完整性好,不会在板上带入误差;FPGA程序可以根据PCI接口输入的配置和控制命令,协调系统各模块一致运行,实现预期的系统功能。

[1] Eric Bogatin.Signalty Integrity: Simplified.Prentice Hall PTR,2003.

[2] 周杰.高速PCB设计的布局布线优化方法.电子工程专辑,2003,8.

[3] Hall,S.H.,Hall,G.W.,and McCall,J.A.High Speed Digital System Design.Hoboken,NJ:John Wiley and Sons,2000.

[4] Johnson,Howard,and Graham,Martin.High Speed Digital Design.Upper Saddle River,NJ:Prentice Hall,1993.