一种单锁相环最大比极化分集合成算法的FPGA实现*

李湘鲁,黄 强

(中国工程物理研究院电子工程研究所 绵阳621900)

1 引言

对于4种基本分集方式(极化分集、频率分集、空间分集、时间分集),在遥测接收系统中主要应用极化分集方式,它经济可靠、技术成熟。在测控应用中,下行信号中存在着两个相互正交的极化波。由于目标的姿态变化、多径效应等因素的影响,两种极化分量相对大小可能随时变化,因此在测控接收机中应有相应的极化分集接收能力[1],以抗起伏衰落、提高输入信号S/N并且克服天线单极化存在的深零点影响。

目前,国内外采用最普遍的方案为三环路锁相分集接收方案。它由3个锁相环路组成,1个主环,2个副环,3个锁相环均采用同一个参考源为基准。主环跟踪合成载波,两个副环分别跟踪两个极化支路的载波,以保证两支路相加时相位保持一致。另外,还有两种方案也有采用:共模与差模环极化合成方案以及左旋、右旋双环合成方案[2,3]。这3种方案的不足在于:至少需要2套锁相环电路,并且需要一个参考源为基准才能工作。

针对以上3种方案在中频实现相对比较复杂,本文提出一种基于复基带的检前最大比分集合成算法,该方案不需要参考源,只需要1套锁相环电路,性能优良,工程实现相对简单。

2 最大比分集合成算法

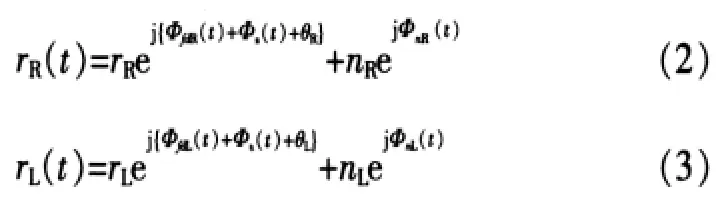

极化分集合成的关键技术是最大比值合成器和分集锁相环。分集锁相环保证两正交极化分量同相相加,而最大比值合成器则保证输出的S/N为最佳。

最大比合成(MRC),就是在接收端有D个分集支路,经过相位调整之后,按照适当的增益系数,同相相加进行合并。结合项目实际,就是分别有左旋极化支路和右旋极化支路2个分集支路参与合成。最大比值的合成器实现如下的运算:S=SRCR+SLCL,其中SR和SL分别为右旋和左旋信号的幅度,CR和CL为各自的加权因子。测出SR和SL(可利用其AGC电压来求得)就可以计算出CR和CL,从而实现上面的计算,它的输出就是最大比合成。图1所示就是一个最大比合成图。

最大比例系数的计算为:

极化分集合成另一关键技术的分集锁相环结构如图2所示。由于此方案建立在同相合成基础上,因此它保留了同相合成的所有优点,同时具有最佳的合成信噪比输出,在实现方式上,同相的方案实现是采用两路叉积鉴相的方式,此方式具有控制精度高,控制速度快,电路稳定性高等优点。

设通道R、通道L输入复基带信号为:

式中:rR、rL、nR、nL分别为通道 R 和通道 L 信号和噪声的幅度,ΦfdR(t)、ΦnR(t)分别为通道 R 多普勒频率产生的相位、通道 R噪声产生的相位,θR为通道 R的初始相位,ΦfdL(t)、ΦnL(t)分别为通道 L 多普勒频率产生的相位、通道L 噪声产生的相位,θL为通道 L 的初始相位,Φs(t)为调制信号产生的相位。

通过叉积鉴相,得到环路滤波器输入信号为:

可以看出,检相输出中完全消除了调制信号分量Φs(t),因此环路滤波器的设计可以不考虑信号带宽的影响,为了跟踪较大的频率差或相位差,同时提高锁定速度,可以适当增大环路滤波器的带宽。

3 仿真分析

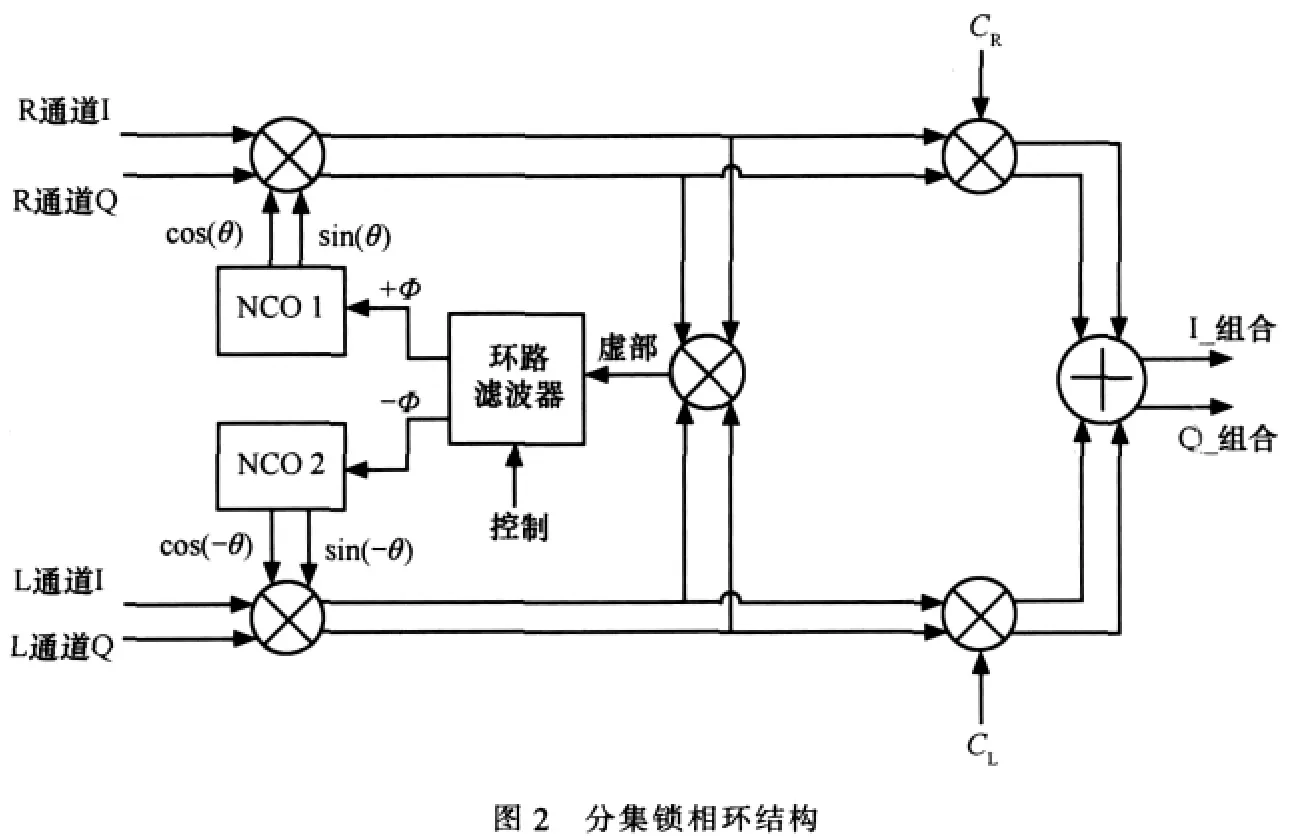

针对一个复基带线性调频信号,设两通道初始频差20 Hz,初始相差110°,信噪比为 10 dB,得到处理前后的结果如图3所示。

可见两路信号经过分集算法处理后,其频率和相位已经调整到一致并且用时很短。

4 FPGA硬件实现

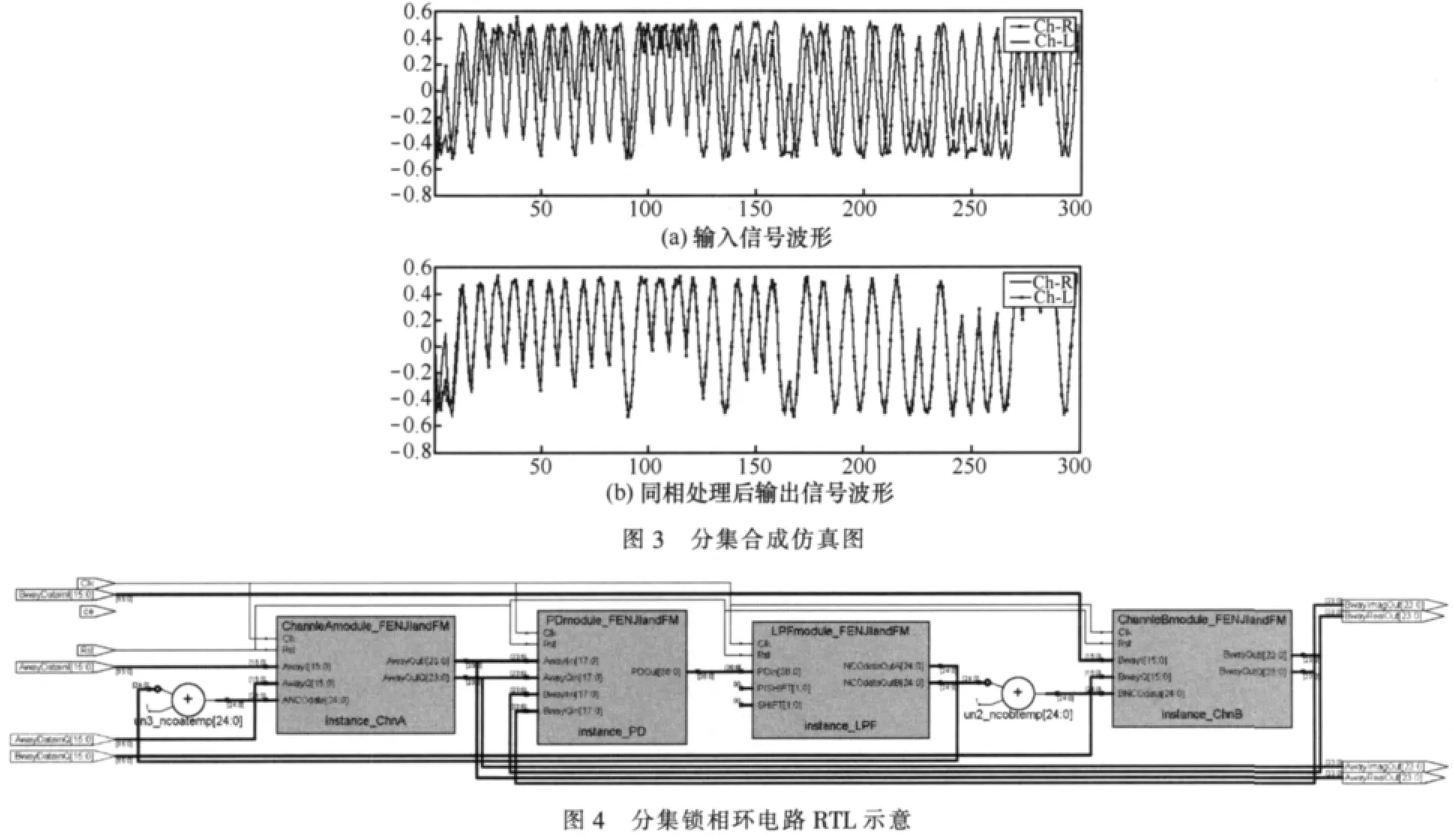

图4为整个分集合成锁相环电路RTL原理图,主要分为鉴相器、环路滤波器、左旋支路NCO和右旋支路NCO 4个模块。

本电路使用Xilinx公司的Virtex4系列XC4VLX200芯片进行综合,使用了Slice 1 207个,占全部的1.3%,RAMB16s资源使用8个,占全部3%。整个电路可以工作到252 MHz。

5 结束语

本文针对复基带信号,提出了检前最大比分集合成算法。由于相位调整锁相环采用叉积鉴相,消除了调频信号的影响,因此环路带宽不受信号带宽的限制,简化锁相环的工程实现复杂度,且能够跟踪较大的频率差,锁定速度快。该算法已成功实现并运用于某数传接收机中,性能稳定优良,经过测试可以达到2.8 dB左右的灵敏度增益。

1 刘嘉兴.载人航天USB测控系统及其关键技术.宇航学报,2005,26(11)

2 张睿.数字分集接收机的研究.重庆大学硕士学位论文,2005

3 吴初辉,李宗利.遥测信号数字极化分集接收机的建模和仿真.第二届中国系统建模与仿真技术高层论坛,2007