基于FPGA高速帧同步设计及性能分析

陈 燕

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

随着数据设备种类增加,精度提高,数据传输容量随之急剧增加,高速数据传输就是把各种数据组合成大容量数据组进行传输。

在数据发送端需要对数据进行帧格式化处理,在数据接收端利用帧同步捕获技术恢复原始数据。由于数据速率远高于芯片处理能力,为了保证同步时间,必须采用并行处理。对数据传输中的帧结构进行了分析,论述了帧同步关键技术,针对高速数据传输的特点,给出了基于FPGA实现的快速帧同步设计方法,并对性能进行了分析和测试。

1 帧结构分析

数据传输的速率为300 Mbps,帧结构采用CCSDS建议,帧长为1 024,其中帧定位码为4字节长1ACFFC1D,1 020字节为RS(255,239)编码交织后的传输数据,d为信息字节,c为校验字节,由于交织深度为4,每帧传输4组,共 4×255字节,帧结构图如图1所示。

图1 帧结构框图

帧结构为集中连续插入帧同步码组,设备完成4组RS编码后,每一组交替输出1字节,实现交织深度为4的交织。然后在每帧的开头加入特殊码组1ACFFC1D作为帧头定位码,定位码长32 bit,在设备接收端通过该特殊码组建立同步,确定RS码的译码分组,并最终完成译码恢复数据。

由于交织深度是4,所以采用4个RS编码块同时并行处理,原始数据分为4组,每组为239字节,分别进行RS(255,239)编码,编码完成后,每组数据前239字节为原始信息数据,后16字节为RS校验字节,输出数据流顺序为第1组的第1字节然后跟着第2组第1字,输出完后面几组的第1字节,再输出从第1组开始的第2字节,直至完成第4组第256字节的数据。

由于帧头为4字节,每组完成编码后的字节为255字节,4组共1 020字节,因此帧长为1 024字节。在帧同步码确定、帧长确定的情况下,帧同步的性能有:帧同步时间、假同步概率、同步保持时间。在接收端为了保证同步性能,需要对同步进行设计。在此主要讨论高速帧同步的实现及性能分析。

2 关键技术

在设备接收端为了正确恢复数据,必须保持帧同步,帧同步指把接收端的帧状态调整到与发送端帧状态具有正确的关系,并保持这种正确关系的过程。

设计的关键技术有搜索电路设计、校核电路设计和同步保持设计,其状态图如图2所示。

图2 帧同步过程状态机

2.1 搜索态

设备在失步期间,采用预置启动搜捕,接收设备时序发生器被置在搜索态,接收码流逐比特进入同步检测电路,一旦其中的32位信码与规定的同步字1ACFFC1D相同,就立即输出控制信号,启动状态机进入校核态。经过一个检验周期的时间,如果未检测到正确的同步码,则重复上述过程。

2.2 校核态

为了防止信号中出现虚假同步,找到第1组同步码后跳过1帧长度必须再次确认帧同步码。若连续经过M帧同步码确认均同步正确,则系统立即转入同步状态;否则存在假同步;返回搜索态。由首次搜索到帧同步码到进入同步态的M帧时间叫后方保护时间。

2.3 同步态

帧同步处于同步状态时,若连续N帧帧同步码正确则仍保持在同步状态。考虑到接收数据流的帧同步码可能受外界干扰而存在误码,在同步状态中只有连续N帧丢失同步码,才进入失步状态,并返回搜索态。其中N帧的时间叫前方保护时间。由于有前方保护时间,在接收过程中虽然出现了某一帧同步码字有误码,但系统并不会立即进入失步状态。由此可减少因误码而进入失步状态的可能性。

以上论述了帧同步的关键技术,但当数据速率高达300Mps时,码流逐比特的速率远远高于比较累加器的速率,而且芯片也无法承受300 Mbps的连续处理,因此必须采用并行处理,降低芯片的运行速度。

3 高速帧同步设计

为了实现高速数据的同步搜索,有2种方法可采用:①采用足够深的缓存,延时处理,依靠缓存的时间来实现判断。但这种方式处理起来比较耗资源,同时固定时延较长;②介绍一种在FPGA中采用实时并行同步比较的方法,在FPGA硬件资源开销中只增加 2*(N-1)*Dl个FPGA的基本单元(CLB),N为并行路数,Dl为帧码长度。

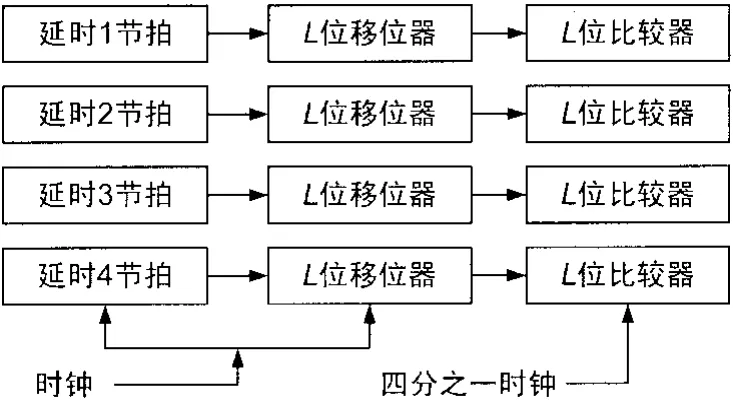

同步相关检测判决器[3]并行路数可根据速率设置,以并行路数4为例,串行数据流同时进入4个移位判决电路,每路相差一个时钟节拍,每隔4个节拍进行一次相关判决,一旦4路中有一路产生检测峰,表明已搜索到一个同步帧头,可启动进入帧同步的校核状态。这样判决速率为数据速率的四分之一,如速率更高,可增加并行路数,这样只需要增加并行判决电路即可完成。并行同步搜索实现框图如图3所示。

图3 并行同步字搜索框图

从图中可见,只有延时器及N位移位器电路工作于输入的高速时钟,由于FPGA触发器翻转速率极快,可适应较高频率,这部分通过局部布局布线实现高速工作,其他电路均可工作在比较低的速率,速率根据并行路数而定,低钟可利用FPGA内部时钟除法电路实现,降速工作使FPGA的工作稳定性得到提高。

4 性能分析与测试

考核同步性能的主要指标有,平均同步捕获时间,假同步概率,同步保持时间。

平均同步捕获时间与帧长、数据速率、校核次数有关。在帧长L=1 024 byte,数据速率v=300 Mbps,帧长时TL=L/v=27.3 μ s,校验次数α=3次时,根据平均确认同步时间公式Tw=(α-1/2)T[2]L(忽略虚漏概率),计算得平均同步时间为68.2 μ s。

除此之外,在有噪声信道上传输数据时,为了避免假同步 ,采用帧同步校验的方法,即连续在帧同步码位上核实,校验次数与出现假帧同步的概率为:

式中,为校核次数α为时假帧定位概率;α为校核次数;r为帧同步字的长度。可见,采用帧同步校核比加长帧定位更有效[2]。

帧同步电路的平均同步时间也是重要的指标,在有噪声信道传输数据时,如果不采取保护,帧定位码一旦有误就立即失步,失步概率为pl≈r×pe,它与帧频fL相乘就是每秒中平均发生失步的次数,乘积的倒数也就是2次失步之间的平均时间间隔:

若保护帧数为β,平均失步间隔为[2]:

同步字长r=32,帧长时TL=27.3 μ s(帧长/传输速率),Pe=10-3,不采取保护,Tf=853 μ s,采取保护取 β=6,Tf≈8.06小时,若Pe=10-6,不采取保护时,Tf=853 ms,采取保护 β=3,Tf≈634年,所以在实际系统中采取帧保护,即使信号误码率较大时也能使设备有较长的同步保持时间。

在实际系统中,对同步时间及同步持续时间进行了测试,采用在发送帧中插入帧记数值,发送端开始发送时把帧记数值置为0,接收端同步建立后记录数据,从接收到的第一帧数据的记数字节读取记数值,同步时间Tw=Nc×Lf×8/v,(帧长时TL=Lf×8/v),Tw为同步时间,Nc同步建立后接收到第一帧数据的帧记数值,Lf为帧长,帧长以字节为单位,每字节8 bit,v为数据速率。在Pe=10-3时,测得记数值分别为2,3,2,2,2,3,2,2,4,2,平均同步时间=((2+3+2+2+2+2+3+2+2+4+2)/10)*TL=70.99 μ s,测试是在有噪信道下测试,由于存在虚警概率,测得的数据与根据公式[2]忽略虚漏警计算得到数据相比,同步时间稍长。

在信号Pe=10-6时用误码仪测试同步保持时间,最长连续测试时间为96 h,均未出现失步。测试数据与分析计算数据相近。因此采用并行同步处理,帧同步信能不恶化。

5 结束语

在FPGA上采用并行处理的代价是资源的增加,因此在高速帧同步电路设计中采用局部并行处理,在增加资源和降低速率之间取得均衡,这样,可降低高速电路时序调整的难度,提高芯片工作稳定性,有利于FPGA综合实现。以上所用帧同步电路已应用于某项目中。

[1]苏鹏冲,李维忠.高级在轨系统(AOS)帧同步信号发送器的设计与实现[J].福建电脑,2006(4):171-172.

[2]孙 玉.数字复接技术[M].北京:人民邮电出版社,1983.

[3]胡 莉,张力伟,周希元.帧同步检测技术的研究进展[J].无线电工程,2009,39(2):12-15.

- 无线电工程的其它文章

- 局部多项式回归的图像重建改进