C8051F120代替C8051F020的应用实现*

霍彩虹,徐芳萍

(河南 新乡 760厂,河南 新乡 453009)

C8051F[1]系列单片机是由 Silicon Laboratory 公司生产的具有CIP-51内核高性能微控制器。其CIP-51与MCS-51指令集完全兼容,具有标准的8052外设部件。CIP-51采用流水线结构,与标准的8051结构相比指令执行速度有很大的提高,具有JTAG接口,可在系统编程,程序调试与下载都非常方便。另外,C8051F是一种混合信号微控制器,片上不但具有SPI、I2C等接口,还集成了ADC和DAC,使用起来更加简便。这些优越的性能使C8051F系列单片机一经推出便迅速在国内得到普及。C8051F020[2]是其中最常用的一种,已被广泛应用到通信、电子及工业监控等领域。但是随着这些电子产品的不断智能化、复杂化,程序代码长度和数据空间越来越大,而C8051F020的存储空间只有64KB。如果产品需要升级增加新功能,面临的最大问题之一,则是64KB存储空间满足不了程序使用。

对于一个正在被使用的产品来说,通过改动硬件实现升级的方式显然是不太合适的。那么能否从C8051F系列单片机中找到一款存储空间大、引脚完全兼容的器件来代替C8051F020呢?C8051F120正是解决这一难题的理想选择。

1 C8051F120与C8051F020的区别

C8051F120[3]是一款与 C8051F020 引脚完全兼容,FLASH存储空间达到128KB,片上外部RAM达到8KB的单片机,其性能比 C8051F020更优越。C8051F120与C8051F020的主要区别如下:

1)C8051F120与C8051F020虽然引脚兼容但代码却不同,CIP-51实现了 SFR分页机制,C8051F120使用5个SFR页:0、1、2、3和F。使用特殊功能寄存器页选择寄存器SFRPAGE来选择SFR页。例如要访问异步串口0(UART0)的控制寄存器SCON0,首先需对SFRPAGE进行设置,使其位于第0页,即SFRPAGE=0,然后才能对SCON0进行访问。

2)C8051F120内部有一个精确的24.5MHz的内部振荡器,同时内部还有1个锁相环PLL,通过使用这个PLL,可使C8051F120工作频率高达100MHz。

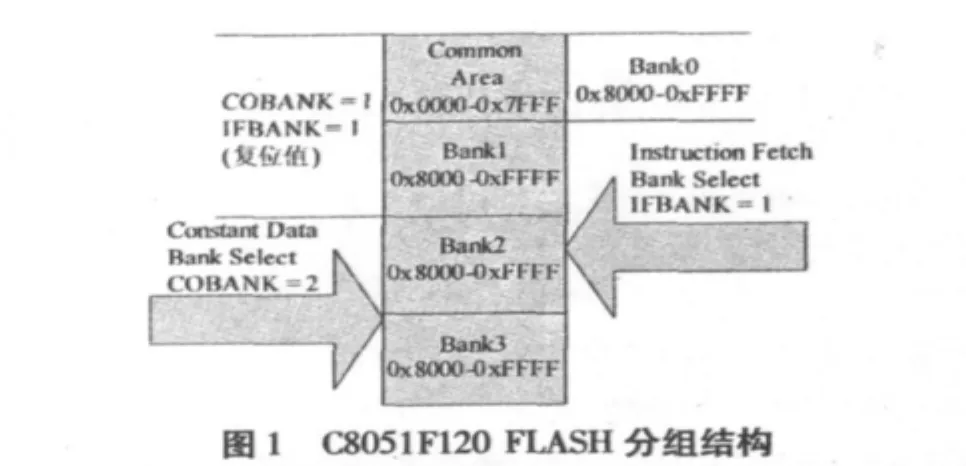

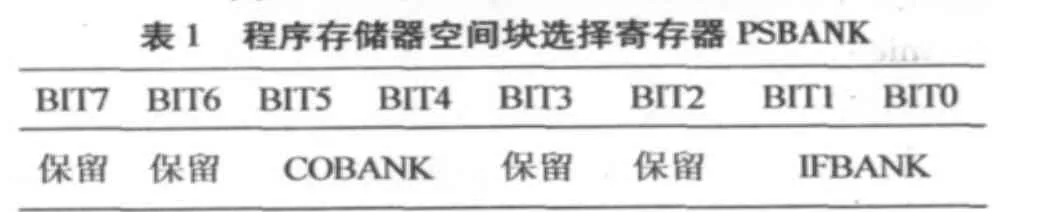

3)C8051F120的FLASH存储器采用代码分页(Code Banking),共4页,每页32KB。其FLASH分组结构如图1所示,在执行FLASH写、读、擦除操作时,PSBANK寄存器(见表1)中的COBANK位决定三个高地址FLASH块中的哪一个被映射到地址范围0x08000~0x0FFFF。

COBANK:常量操作存储块选择位,分别指向BANK 0-3;IFBANK:取指操作存储块选择位,分别指向BANK 0-3

4)C8051F120的外设在结构上与C8051F020也有部分区别,如UART0的波特率设置,通过对寄存器SSTA0的配置可选择定时器1、2、3或4作为波特率发生源,而URAT1具有增强型的波特率发生器,由定时器1作为其波特率发生源,因此在对原C8051F020的程序进行更改时应特别注意这些细节。

2 利用Keil C51工具实现大容量程序的存储

Keil C51[5]工具是目前各种51系列单片机最通用的编译工具软件,它支持代码分页,可以管理一个公共的区域和32个代码页,每个最大可达64KB,从而具备共2MB的代码切换空间。如果没有相应的代码分页设置,Keil C51将无法编辑超过64KB地址空间的程序。一般情况下,用户运行的程序都在FLASH的0X0000~0XFFFF地址空间中。Keil C5l代码分页使用的是Bank Switching技术。使用Bank Switching技术可生成代码长度和数据空间大于64 KB的目标程序,它的使用弥补了C8051F系列单片机在地址空间方面的不足,拓展了它的应用范围。

2.1 Bank Switching技术介绍

具体实现Bank Switching技术的是KeilC#5l中的分组连接定位器BL5l。Keil C5l语言源程序经过C5l编译器编译后,生成浮动地址的目标代码文件。这种浮动地址的目标代码必须经过连接定位器BL5l的连接和定位,生成具有绝对地址的目标代码,才能写入程序存储器正常运行。BL51支持分组连接定位,允许生成代码大于64 KB的目标程序,可以在具有适当硬件扩展逻辑的系统中进行代码组之间的切换,以达到正常运行的目的。目前版本的BL5l可以管理最多64个代码组,每个代码组最大为64KB。

2.2 Bank Switching技术在C8051F120中的应用

C8051F120的FLASH存储空间为128K,采用代码分页,共分为4页,每页32KB,把主程序放在公共代码区(Common Area),复位和中断向量、代码常数、C51中断函数、组切跳转表、库函数这些代码必须安排在公共代码区域。用C8051F120代替C8051F020只需对程序进行修改,C8051F120采用了代码分页,因此必须将原来的程序进行重新划分,合理安排存储空间。由于笔者所设计的程序较为复杂,不易举例说明,下面给出一个结构简单的示例作说明,利用Keil C51进行程序编译的具体操作步骤如下[4]:

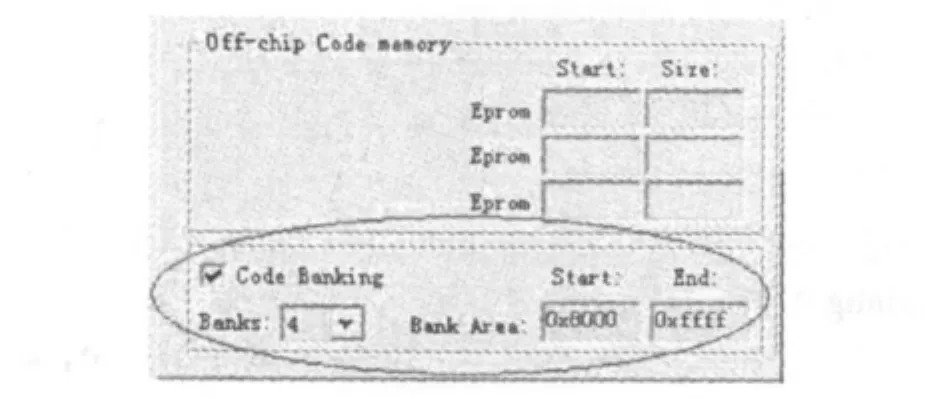

1)在菜单 Project选择中选择Option for Target“Target”选择项,按图2所示进行项目配置。

图2 Option for Target“Target”配置

由于C8051F120有4页分区,每页32KB,所以选择“Code Banking”,在 Banks中写入 4,在 Bank Area中写入地址范围为0x80000~0xffff。

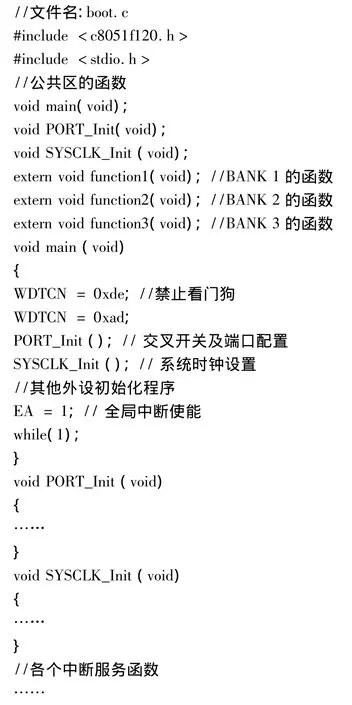

2)新建工程项目,将文件 boot.c,function1.c,function2.c和function3.c依次加入到该工程中,其中boot.c文件,作为公用代码段程序,main函数是分别调用不同分页区的程序,程序代码如下:

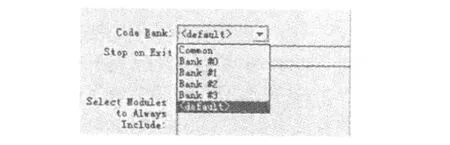

下面,我们将这些文件指定到不同分区中。用右键点击树状列表中的 boot.c,选中 option for file“boot.c”,在 properties的 code bank选项中,选择 common项,如图3所示:此项表明boot.c将被编译到代码的公用代码段中,在所有分页代码的起始部分被复制。与此类似,我们将 function1.c,function2.c和 function3.c分别指定到bank1,bank2,和bank3中。

图3 code bank配置

将keilc51libl51_bank.a51复制到项目目录下,并加入项目中,在l51_bank.a51中,主要修改以下内容[3]:

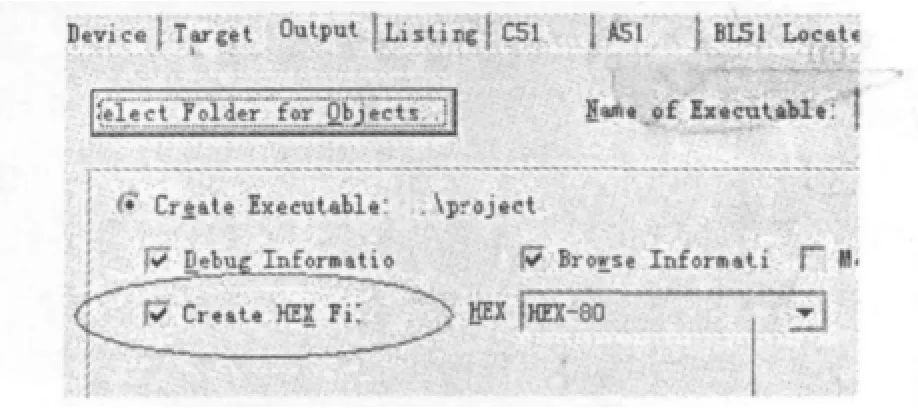

3)在菜单 Project选择中选择 Option for Target“Output”选择项,按图4所示进行项目配置。

图4 Option for Target“Output”配置图

4)编译该项目,keil c编译器将生成1个project.M51文件,检查该文件可验证各个文件的BANK分配情况。同时,编译后会产生 project.H01、project.H02和project.H03这3个hex文件,通过下载器可将此3个文件按照指定的代码空间分别下载到C8051F120的各个BANK空间段中。

3 结语

采用Keil C51的代码分页技术——Bank Switching技术,可以有效地解决大容量程序代码和数据在C8051F120中的存储问题。当C8051F020系统中的Flash存储空间不能满足需要时,可以直接利用C8051F120来替代,这种解决方案改动简单、技术可行,是C8051F020升级使用最为有效的方法之一。同时Keil C51的代码分页技术也使得C8051F系列单片机的应用领域更为广阔。

[1]潘琢金,孙德龙,夏秀峰.C8051F单片机应用解析[M].北京:北京航空航天大学出版社,2002.

[2]Silicon Laboratories.C8051F020/1/2/3 Mixed - Signal ISP FLASH MCU Family[EB/OL].http://www.xhl.com.cn/sjsc/sjsc/sjscdetail:asp?sid=21,2005,11.

[3]Silicon Laboratories.C8051F120/1/2/3 High - Speed Mixed - Signal ISP FLASH MCU[EB/OL].http://www.xhl.com.cn/sjsc/sjsc/sjscdetail:asp?sid=33,2005,11.

[4]Silicon Laboratories.CODE BANKING USING THE KEIL 8051 TOOLS[EB/OL].http://www.xhl.com.cn/xhl/downfile/e_AN30.pdf,2005.11.

[5]Keil Software.Getting Started with μVision2[EB/OL].2001.