基于FPGA的半硬回收数据采集存储系统设计

聂 飞,张 荣,黄海莹

(中国工程物理研究院 总体工程研究所,绵阳 621900)

1 引言

半硬回收系统作为多通道数据采集存储装置,主要负责记录某系统空中飞行试验全程的加速度、环境参数以及各种动作控制信号。在飞行试验完成后,将半硬回收装置内的存储器取出并连接到新的数据采集存储装置上,利用计算机将存储器内的信号回读并显示出来。由于在设计中要求半硬回收系统硬件尺寸不大于φ60 mm,同时要与3.3 V和5 V系统接口,这对硬件设计提出了较高难度的要求,在硬件上确保计算机软件的高速数据回读、高速校验,保证了科技人员在试验现场即可观测测量的结果。本文利用VHDL语言和 QuartusⅡ7.1软件作为开发环境完成了整个半硬回收系统硬件设计。

2 系统硬件组成

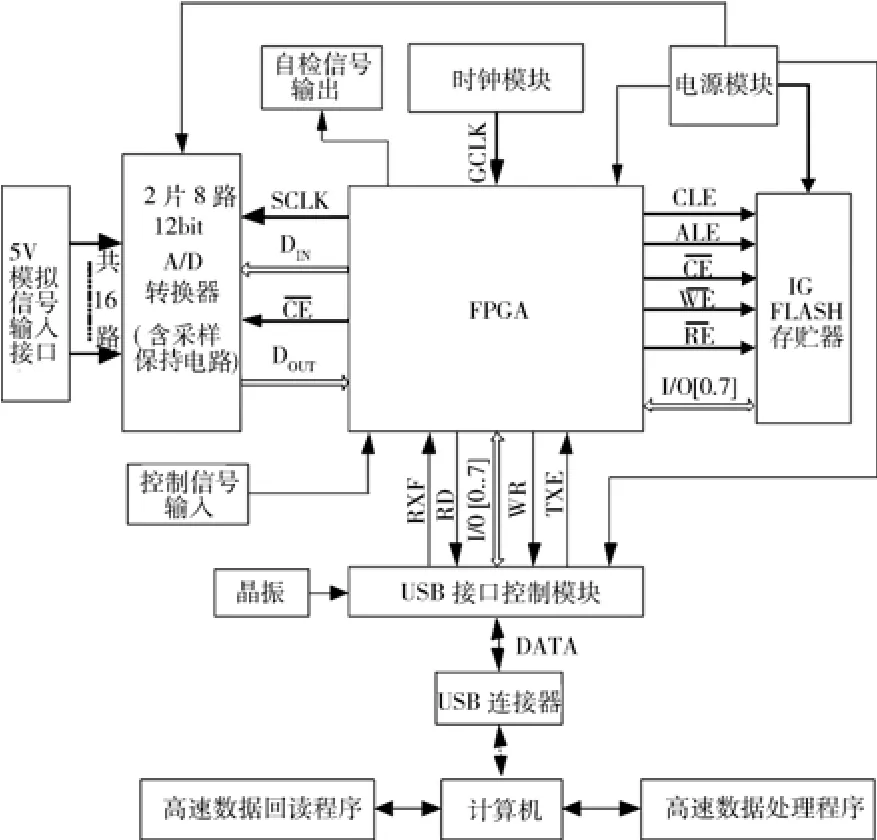

半硬回收数据采集存储系统主要由 FPGA、A/D转换器、Flash存储器、USB接口芯片以及电源模块构成,系统原理如图1所示。

数据采集、存储系统设计技术指标如下:(1) 模拟信号输入通道数16路;(2) 模拟信号输入范围0~5 V;(3) 数据分辨率12 bit;(4)3路数字信号输入,1路数字信号输出;(5) 采样频率 10 kHz(最大可升级到 20 kHz);(6) 存储器容量1 GB。

图1 半硬回收数据采集存储系统Fig.1 Schematic diagram of half-reclaimable data acquisition and storage system

3 FPGA时序设计

3.1 主控逻辑模块设计

主控逻辑模块在半硬回收数据采集系统中担任时序控制、数据缓存、Flash读写擦除、A/D转换器的启动、USB接口读写以及与程控系统通信等重要工作,是设计的重点。FPGA选用ALTERA公司的 EP1K50。设计思路采用“自上而下”[1]的模式。

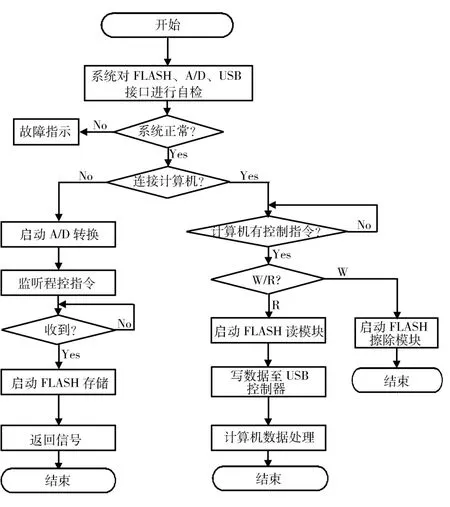

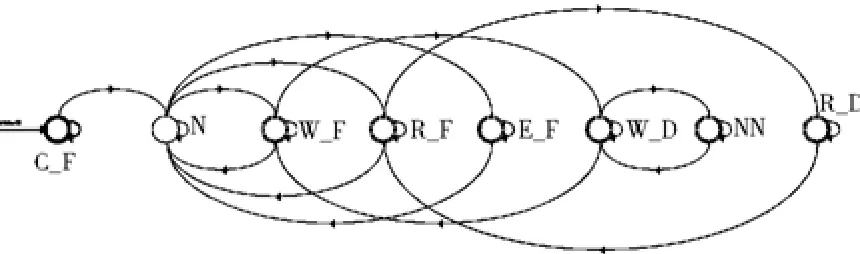

系统在通电时完成FPGA配置后,FPGA开始工作。首先要完成系统的自检,自检工作主要包括Flash的无效块检测和初始化、A/D转换器和USB接口控制模块的初始化。系统自检完后通过LED指示系统向程控输出状态信号,系统正常则启动 A/D转换器,此时数据不存储,系统处于等待命令状态,当接收到来自程控系统的存储指令后,启动Flash存储模块,并返回一个信号至程控系统。系统自检完后,若USB接口连接至计算机,计算机发出读指令后,FPGA启动读Flash模块并将数据送往计算机进行处理;数据读完后,计算机发出清空Flash指令,FPGA则启动擦除Flash模块。主控逻辑模块工作流程如图2。主控逻辑模块包含C_F、N、W_F、R_F、E_F、W_D、NN、R_D共8个状态,其状态转移如图3。

图2 主控逻辑模块工作流程Fig.2 Flow chart of main controller module

图3 主控逻辑状态转移Fig.3 Transferring of main controller logic states

3.2 A/D时序设计

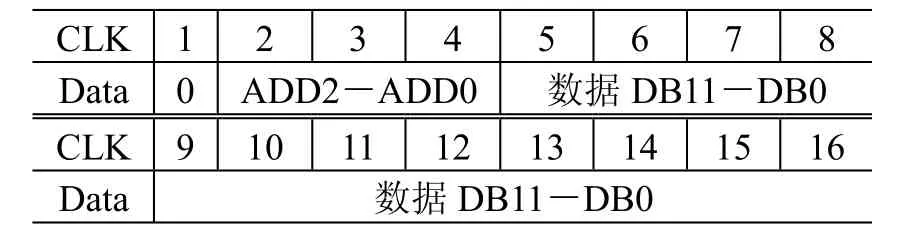

本系统中A/D芯片选用AD7928[2],该芯片为8路模拟输入,输入电压范围2.5~5 V可选,采样数据为 12 bit,单通道最高采样频率 1 Mbit/s,每次数据转换需要16个时钟周期,输出数据格式见表1。

在本系统中,使用了2片AD7928,共16个模拟输入通道,1#A/D的输入通道编号为0~7,2#A/D的输入通道编号为8~15,因此需用4位表示当前数据输出通道号,即当1#A/D输出数据时在其输出地址的基础上增加一位“0”,2#A/D输出数据时在其输出地址的基础上增加一位“1”,这样通道和数据共16位,采用2个字节表示,其数据编码格式见表 2。编码好后的数据依次存入在FPGA内开辟的2 048 B的FIFO中。

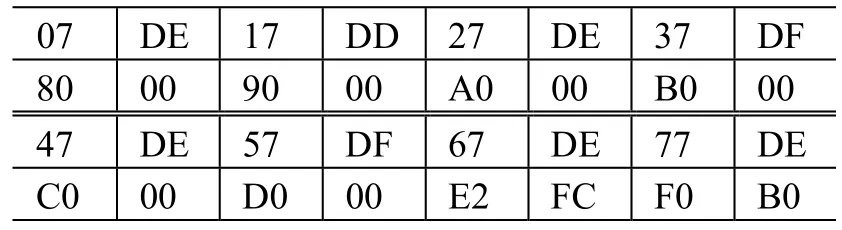

表1 AD7928数据输出格式Table 1 Data output format of AD7928

表2 16通道采样数据编码格式样表Table 2 Code format of 16 channel sample data

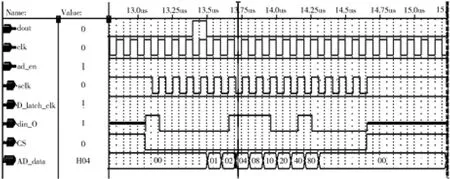

A/D在通电后,首先需对控制寄存器进行操作,AD7928的控制寄存器为12 bit只写寄存器,在控制寄存器中完成通道输入电压范围设置、A/D通道选择、输出数据编码格式设置以及电源模式设置等,本设计中控制字为“110111111001”,由于输入控制字在16个周期内完成,最后4个周期一般设置为“1”。图4为QuartusⅡ7.1下VHDL代码编写的A/D控制模块仿真结果。

图4 A/D时序仿真结果Fig.4 Simulation result of AD time sequence

3.3 Flash模块设计

系统选用了三星公司的闪存芯片K9K8G08U0A[3]作为数据存储器,该 Flash容量为8 Gbit,采用3.3 V供电,它可以在400 μs内完成一页2 112个字节的编程操作,还可以在2 ms内完成128 kB字节的擦除操作,同时数据区内的数据能以50 ns/B的速度读出。K9K8G08U0A大容量闪存芯片的 I/O口既可以作为地址的输入端,也可以作为数据的输入/输出端,同时还可以作为指令的输入端。芯片上的写控制器能自动控制所有编程和擦除操作,包括提供必要的重复脉冲、内部确认和数据空间等。

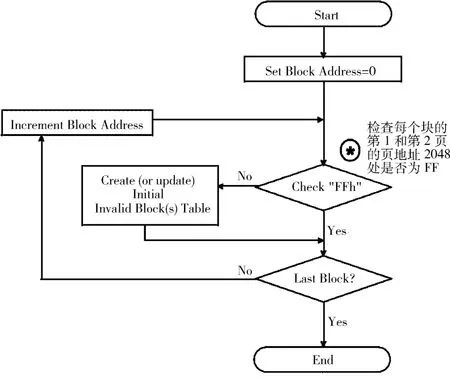

Flash芯片在出厂时可能存在坏块,在使用过程中也会产生坏块。坏块是包含一位或多位无效位的块。坏块在大多数情况下也是可擦写的,并且一旦被擦掉就不可能恢复。因此在Flash进行读、写或擦除操作前,必须检测出Flash中的坏块,并建立块的好坏状态表以备执行其他操作时进行查询。K9K8G08U0A的块检测操作流程如图5。

对于 Flash的写操作如果按页进行,在保证不丢失 A/D采样数据的情况下至少需要开辟4 096 B的缓存空间,同时对于建立块的好坏信息表需要8 192 bit的存储空间,在这种情况下就超过了所选FPGA的内部资源容量,因此Flash的读写操作均改为半页操作,即将数据缓存空间改为2 048 B,当FIFO半满时主控逻辑启动Flash的写操作。

图5 K9K8G08U0A的块检测操作流程Fig.5 Block check flow chart of K9K8G08U0A

3.4 USB接口设计

半硬回收系统所采集数据最终通过 USB接口上传到计算机,同时计算机通过USB接口下发指令到半硬回收系统,其指令包括:(1) 利用计算机向回读装置发送与结束数据预采集命令。该功能用于调试半硬回收装置硬件时使用;(2) 利用计算机向装置发送擦写 Flash存储记忆体的命令。该功能用于数据采集前清除 Flash内容。命令功能表见表3。

表3 USB命令表Table 3 Commands of USB

半硬回收装置数据回读系统硬件利用 FTDI公司生产的FT245BM芯片实现系统与计算机之间的 USB总线接口通讯。FT245BM 芯片支持USB1.1与USB2.0规范,数据最大传输速率可达1 MB/s。USB接口的VHDL设计主要包括接收数据和发送数据两个状态。

4 结论

多次利用标准信号源以及振动试验、火炮试验对半硬回收装置进行考核调试,结果表明系统能有效采集、存储数据,与计算机通信时能有效接收命令和回传数据,数据上传速率为8 Mbit/s,系统运行稳定可靠。

(References)

[1]Stefan S, Lennart L.VHDL设计电子线路[M].边计年, 薛宏熙, 译.北京: 清华大学出版社, 2008: 10

[2]Analog Device.8-channel, 1MSPS, 8-/10-/12-bit ADCs AD7908/AD7918/ AD7928[G], 2006

[3]Samsung Electronics Co., Ltd..K9XXG08UXA Flash Memory[G], 2006