嵌入式低功耗8位微控制器的设计

赵毅强,刘长龙,严新文

(天津大学电子信息工程学院,天津 300072)

嵌入式低功耗8位微控制器的设计

赵毅强,刘长龙,严新文

(天津大学电子信息工程学院,天津 300072)

设计实现了一款嵌入式低功耗8位微控制器,采用了类精减指令集计算机(RISC)指令集、哈佛双总线体系和两级四段流水线结构.重点研究了微控制器的功耗分布,并从系统级、寄存器传输级(RTL)和逻辑级进行了功耗的优化.基于Chartered 0.35,μm CMOS Logic工艺进行了后端设计并流片,测试结果表明其工作频率可达80,MHz,32,kHz下工作电流为6.75,μA.该微控制器已作为核心控制单元应用于无磁流量计量SoC芯片中,用于完成数据处理和调度工作.

低功耗;嵌入式;微控制器

无磁流量计量是当今流量计量技术的发展趋势,与之配套的专用芯片是该类仪表的关键模块.基于无磁流量计量SoC芯片的项目背景,设计了一款8位嵌入式微控制器,作为SoC芯片的CPU核,完成数据处理和调度工作.传统微控制器一般采用多阈值电压、门控功耗、流水线等方法达到低功耗效果[1],笔者在此基础上针对功耗进行了分析和优化.

1 体系结构设计与优化

设计中采用了一种类精减指令集计算机(reduced instruction set computer,RISC)的指令体系,除了具有指令简洁、 每条指令所需要的周期数(cycles per instruction,CPI)较小等优势外,还具有以下特点:①区别于Load/Store体系,采用了Register-Memory体系,运算指令可以直接访问存储器,这有效地提高了代码密度;②所有指令均等长,大大简化了解码和控制电路的设计,具有较低的功耗和结构尺寸.

由于采用了哈佛双总线结构,指令和数据空间独立编址,CPU可以同时访问程序存储器和数据存储器,并在芯片内部将数据总线和指令总线分离,有效地提高了数据的吞吐量.虽然双总线结构会引起电路规模的扩大,但是控制电路大幅度简化,与传统的冯诺伊曼结构相比,电路规模仍有所减小[2].

深度流水会带来控制冒险和数据冲突,为解决这些问题需要增加复杂的控制逻辑和直通(bypass)结构,这会大大增加芯片的面积和功耗.本次设计采用了二级四段流水线结构,由四相时钟驱动工作,每一段流水线在对应时钟相内完成功能.

(1)在时钟的第一相里,指令译码器、程序计数器等工作,从指令总线获得指令并进行译码操作,同时将程序指针指向下一条指令.

(2)在第二相里,数据寄存器从存储器中读出数据,ALU 进行低4位运算.

(3)在第三相里,ALU进行高4位的运算.

(4)在第四相里,将运算结果送至数据总线,回写到数据存储器、累加器、内部堆栈的相应寄存器内,并将下一条指令从程序存储器中取出放到指令总线上.

采用这样的流水线结构,既能够节省面积和功耗,又能有效地利用现有资源,提高处理器的运算效率[3].

2 低功耗实现技术

2.1 系统级的低功耗设计

2.1.1 休眠模式的设计

休眠模式的功耗是决定芯片整体平均功耗的重要部分.执行SLEEP指令后,处理器会进入休眠工作状态,当发生外部中断或是看门狗溢出时,会从休眠模式返回,继续执行休眠指令之后的下一条指令.

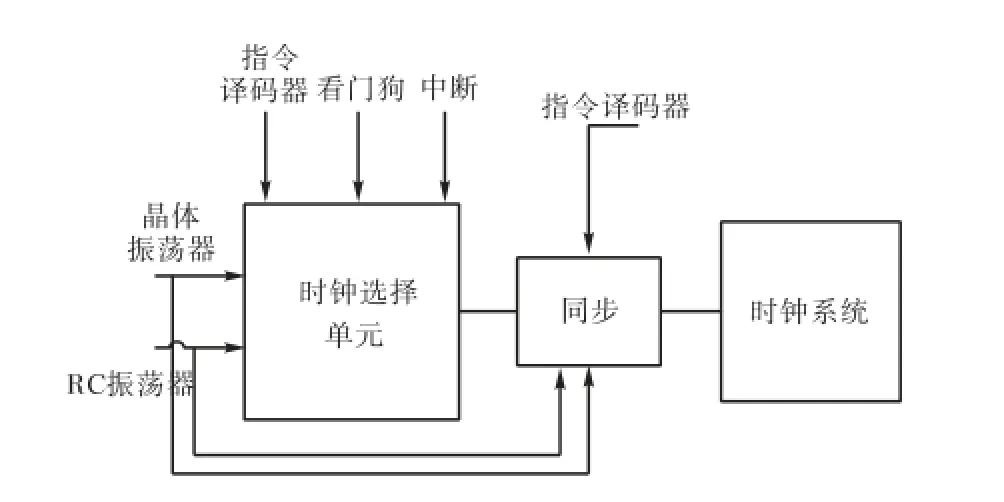

休眠模式设计存在的一个问题是,当微控制单元(micro control unit,MCU)进入休眠状态,主时钟已经关闭,当产生中断时,MCU如何从休眠状态中恢复.笔者设计了主时钟切换和同步电路,如图1所示.片内存在2种振荡电路,包括外接晶振的起振电路和极低频的RC振荡回路,分别为处理器提供主时钟频率和保持时钟频率.当处理器工作在休眠模式时,时钟网络并没有完全关闭,而是将主时钟切换成频率很低的RC振荡信号,在部分模块中仍然保留时钟,当出现中断时,能够及时将状态字置位,切换到主时钟,MCU继续取指工作.为了避免出现切换时钟时产生毛刺导致误操作,要将切换后的时钟经过自同步后再送到时钟网络.由于无磁流量计量SOC芯片一般工作在低功耗模式,故采取2种振荡器设计,在低功耗模式时,选用低时钟频率,可以大大降低系统功耗.

需要注意的是,计量芯片也存在休眠模式,MCU可通过寄存器置位使计量芯片进入休眠状态.但如果两者都停掉了,就会出现一种死锁现象:CPU等待计量芯片产生中断来唤醒,而计量芯片也在等待CPU给出对它的唤醒信号.实际中,这种情况的避免通过软件来实现,停时钟和开时钟都由用户来完成.

图1 时钟选择和同步电路Fig.1 Clock select and sync circuit

2.1.2 时钟网络的管理

时钟网络是数字系统中翻转率最高、驱动能力最大的网络,具有较大的电容和负载,数据表明,现代数字芯片有1/3的功耗是消耗在时钟网络上的.

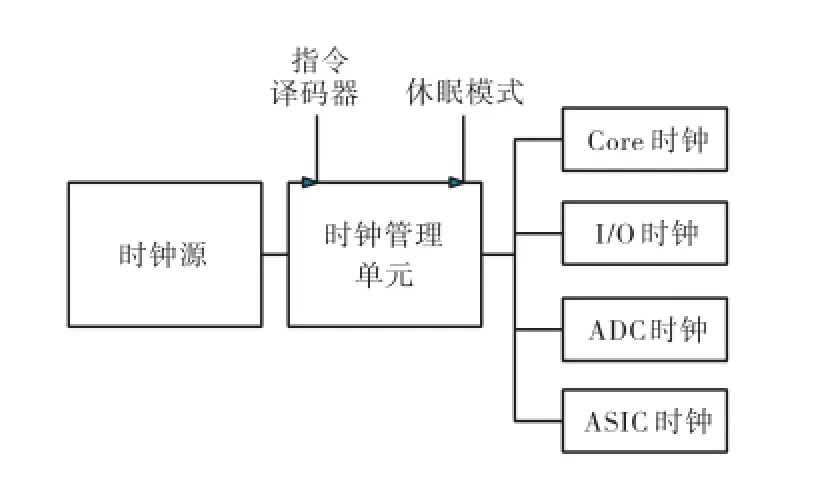

通过关闭闲置模块的时钟,可以有效降低时钟网络的功耗.如图2所示,时钟网络管理模块根据指令译码器的输出和休眠模式来决定全局的功耗策略,STATE1通过切换高低频时钟来降低功耗;STATE2将选择性地关闭闲置子模块的源时钟网络;STATE3在STATE2的基础上关闭外设模块如计量芯片和ADC的时钟.采用这样的时钟策略,MCU的平均功耗约能降低20%[4].

图2 时钟网络的管理Fig.2 Clock network manage

2.1.3 存储器的低功耗设计

现代SOC系统中一般都要集成存储器,降低存储器的功耗对整个芯片的功耗优化会起很大作用.笔者对片内SRAM采用了分页访问和块寻址技术.

分页访问类似于采用门控技术,首先根据地址将存储器分成容量相等的页面,用最高位地址线作为片选使能信号(CS),这样当访问的单元不在某个分区中时,该分区可以停止工作.2块128K的SRAM的功耗本身已远小于1块256K的RAM的功耗,而且同时只会有一页存储器在工作,这大大降低了存储器的静态功耗.

对于每页SRAM,为避免产生较大的译码电路,将存储器单元分割成较小的块,使用块译码电路,再使用地址线的低位选择需要的数据,这样可以有效地降低访问存储单元的动态功耗[5-6].

2.2 RTL级的低功耗设计

在系统级的优化中,主要从系统时序和模块的工作状态入手.而在寄存器传输级设计中,低功耗设计的主要手段是降低模块内部的组合电路和寄存器单元的规模和翻转频率.

算术逻辑单元是MCU的核心模块,其内部结构如图3所示.由于运算电路复杂,且内部节点的翻转率比较高,常常成为芯片功耗的瓶颈.

图3 ALU结构示意Fig.3 Structure of ALU unit

加法器是ALU中耗费门数最多的部分,且每增加1位,所用总门数都会有较大增加.因此如何改进加法器的电路结构,降低电路规模,是对ALU进行功耗优化的工作重点.在加法器的设计中,采用了用速度换功耗的思路,利用分时复用结构,降低运算体的位数,将本来在1个时钟相位的8位运算,用1个4位的加法器在2个相位分别完成高4位和低4位运算.表1是2种加法器经DC综合后得到的参数,可以看到,与原先的结构相比,加法器的等效门数减少了40.5%,单位面积下降了35.9%,工作频率虽略有下降,但是满足了芯片工作环境的要求.

表1 2种结构的参数对比Tab.1 Comparison of two structures

ALU内部主要是组合逻辑电路,当输入信号的改变引起输出信号的改变时,绝大多数节点会发生翻转.降低组合电路模块输入信号的无效翻转可以最终降低这部分电路的功耗.

存储器会根据解码电路输出的控制信号 ENR来决定是否更新自身保存的值,当ENR 信号为低时,ALU的计算结果是无效的.

当执行运算指令时,逻辑单元的运算是无效的,反之亦然;以上这些都造成了内部逻辑的无效翻转,从而造成功耗上的浪费.

解决办法可以由指令译码器产生加法器和逻辑运算单元的使能信号,通过降低组合逻辑输入级的变化率,来减少其内部的无效反转.这种操作数分离的本质就是在组合逻辑模块中间加入Latch,当Latch的使能无效时,隔断组合路径的传递.这样ALU的每一次操作都是有效操作,并且只有相应的运算单元进入工作状态,极大地降低了其功耗[7].

2.3 逻辑综合的低功耗设计

2.3.1 门控时钟的插入

在几个指令周期之间或者一个指令周期内的几个时钟周期之间,某些模块内部的寄存器会消耗不必要的功耗,针对这种情况,可以运用门控来分配各个功能块内的寄存器工作.在高效能的处理器设计中,门控时钟更多的是应用于控制一个指令周期内的功耗.然而,这种门控时钟是不能随便应用的,原因是:①应用门控时钟的寄存器可能在需要工作的时候不能被及时地唤醒, 造成流水线的停顿;②门控单元产生的毛刺可能会导致寄存器误触发,导致逻辑错误.基于以上2点,在一些关键路径的寄存器上,如指令译码器和程序计数器,没有采用门控时钟,保证了处理器的稳定工作;其他模块中,使用Design Compiler来自动插入基于Latch结构的门控时钟,由于将寄存器数据输入端的多路选择器替换成了时钟端的与门,不仅功耗大大降低,同时设计面积也相应减小.

2.3.2 DC功耗的优化

采用Design Compiler进行电路综合时,默认采用的是无向量(Vector-Free)的方法进行功耗分析,但是由于DC的默认节点翻转率较高,而实际上某些特殊信号在电路工作时处于静态值,如Reset信号,这往往会对内部节点的翻转率造成误分析,因此一般采用由动态仿真产生的saif文件进行反标注,并对特殊的输入信号设置常量传播或者设定开关活动率值,然后再进行功耗优化.具体命令为

Set_case_analysis 1 reset [get_ports reset]

Read_saif-input rtl.saif-inst test.top

Set_max_dynamic_power 0

这样DC 会根据节点的实际情况,对单元的驱动能力和负载进行调整,对高活动性的节点进行优化,降低电路的动态功耗[8].

3 测试结果

采用Chartered 0.35,μm Logic工艺完成了MCU芯片(EEPROM除外)的逻辑综合与后端布局布线,单元总面积7,487.310,059,μm2,芯片总面积11,522.109,375,μm2,并参加了MPW流片,目前芯片已经完成了封装和测试,图4为MCU芯片在显微镜下的照片,其中在白框内的为MCU,其余部分为SOC芯片项目的其他单元电路.

功能测试的结果表明,MCU可正确完成指令集的全部35条指令,包括运算类指令和控制类指令,图5为逻辑分析仪对MCU执行运算指令的采样截图.

经测试,内部定时器和中断电路可正确完成相应的功能.图6是采得的休眠、唤醒以及时钟切换的过程.

图4 MCU芯片照片Fig.4 Photo of MCU chip

图5 MCU执行运算指令Fig.5 MCU executing operating instruction

图6 休眠及恢复示意Fig.6 Sleep and awake

测试结果表明,该MCU的工作频率为4,kHz~80,MHz,工作电压范围2.7~5.5,V,32,kHz(3.3,V)下工作电流为6.75,μA.在32,kHz和5,V条件下,比较测试了几款常用的8位MCU,结果见表2.

表2 功耗评估Tab.2 Power evaluation

4 结 语

在研究分析低功耗设计技术的基础上,设计了一款以无磁流量计量技术为应用背景的专用嵌入式8位微控制器,它将集成在包含计量电路、SAR ADC和通讯电路模块等在内的计量SOC芯片中,作为核心控制模块,调度整个系统的工作.同时该MCU可作为一款独立IP,集成于其他控制系统中.

[1] Kang Sung-Mo,Leblebici Yusuf. CMOS Digital Integrated Circuits[M]. Beijing:Tsinghua University Press,2004.

[2] Piguet C. Low power design of 8-bit embedded cool-RISC microcontroller cores[J]. IEEE Journal of Solid-State Circuits,1997,32(7):1067-1077.

[3] Masgonty J M,Arm C,Durand S,et al.Low-power design of an embedded microprocessor core[C]// Solid-State Circuits Conference. Neuchatel,Switzerland,1996:272-275.

[4] Zheng Xinjian,Liu Zexiang,Peng Bo. Design and implementation of an ultra low power RSA coprocessor [C]// Wireless Communications,Networking and Mobile Computing. Dalian,China,2008:1-5.

[5] 应继宏,张盛兵. 八位高性能低功耗微控制器的设计与实现[J]. 科学技术与工程,2007,7(6):984-988. Ying Jihong,Zhang Shengbing. The design and implementation of high-performance low-power 8-bit microcontroller[J]. Science Technology and Engineering,2007,7(6):984-988(in Chinese).

[6] 罗 旻,杨 波,高德远,等. 寄存器传输级低功耗设计方法[J]. 小型微型计算机系统,2004,27(7):1207-1211. Luo Min,Yang Bo,Gao Deyuan,et al. Low-power design method of register transfer level[J]. Journal of Chinese Computer Systems,2004,27(7):1207-1211(in Chinese).

[7] 夏树荣,陈 进,唐 亮. 嵌入式MCU的SOC设计中的低功耗设计[J]. 计算机工程,2004,30(增12):452-453,466. Xia Shurong,Chen Jin,Tang Liang. Low power design in SOC design of embedded MCU[J]. Computer Engineering,2004,30(Suppl 12):452-453,466(in Chinese).

[8] Ajit Pal,Santanu Chattopadhyay. Synthesis and testing for low power [C]// 2009 22nd International Conference on VLSI Design. New Delhi,India,2009:37-38.

Design of an Embedded Low-Power 8-bit Microcontroller

ZHAO Yi-qiang,LIU Chang-long,YAN Xin-wen

(School of Electronic Information Engineering,Tianjin University,Tianjin 300072,China)

A low-power 8-bit embedded microcontroller was proposed,which consisted of reduced instruction set computer (RISC)-like instruction set architecture,Harvard separation-bus architecture and a two-stage four-phase pipeline. Power distribution was emphasized in this research with power consumption optimized at system,register transfer level(RTL) and logic level. An experimental chip was fabricated using Chartered 0.35 μm CMOS Logic process. The measurement results indicate that the microcontroller can function well at a frequency of 80 MHz and the power consumption is approximately 6.75 μA under 32 kHz. As controlling core,the microcontroller is used in nonmagnetic measurement SoC chip to achieve data processing and dispatching.

low-power;embedded;microcontroller

TN492

A

0493-2137(2010)12-1098-05

2009-04-07;

2009-09-21.

天津市科技支撑计划资助项目(08ZCKFGX00200).

赵毅强(1964— ),男,博士,教授.

赵毅强,yq_zhao@tju.edu.cn.