太阳追踪系统控制器的设计与应用*

余 涛, 马立新, 陈国平, 刘和勇

(上海理工大学电气工程系,上海 200093)

0 引言

太阳追踪系统是通过两组光电传感器(东西、南北各一组)传回的电压差信号经过微处理器的分析和计算,再利用微处理器输出的信号来对电机进行控制,从而使电机作相应调整,使太阳能电池板能够做接近于半球面的旋转来对太阳进行追踪,使太阳能电池板能够更多地接收太阳光辐射,实现对太阳能更加充分地吸收利用。

当太阳垂直射到太阳能电池板上时,电池板吸收的光照强度最大。但是,传统的太阳能发电装置是将太阳能电池板固定在预先制作好的支架上,太阳能电池板只能面向一个方向,使太阳能的利用率大大降低。有鉴于此,研究设计了追日性能良好的太阳追踪发电系统,所设计出的装置,除了必须能承载太阳电池面板,也要能让面板在空间中做接近半球面的立体转动,如此才能完全追踪白天太阳在天空中的位置,从而可以使总体发电量得到提高。此系统可以提高照射能量密度,取得光照的最大量,以及在相同的发电量下使用较少的太阳电池以降低发电成本,因此极具研究发展前景。

1 追踪系统的框架及步进电机的控制原理

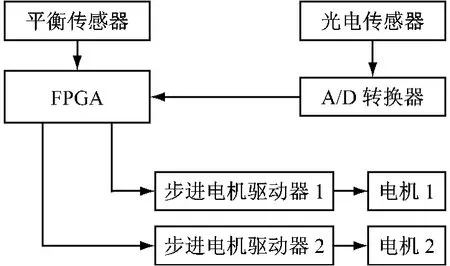

该系统所设计出的系统架构,使用两台步进电机作为驱动源来设计出追日性能良好的太阳追踪装置,此机构为能做接近半球面立体转动的太阳能发电系统。系统框图如图1所示。

图1 太阳追踪系统整体框图

系统中,欲实现大阳能最高效率的利用,关键是对步进电机的精确控制,从而达到对太阳的准确追踪。由于太阳能追踪系统要作接近半球的立体转动,因此步进电机在不同的时候需要作正转或反转运动;另外由于很难做到对太阳的实时追踪,这里采用的是间歇式追踪,当光电传感器传回的电压差值达到一定值时电机才进行姿态调整,使电机作定位运行。因此,作为太阳能追踪系统的重要组成部分,本文主要分析三相步进电机的控制系统。

在目前的应用中,步进电机的控制和驱动大多采用单片机加上1块驱动芯片来实现。但是由于单片机本身资源的限制,一片单片机能够控制的电机数目有限,另外考虑到未来太阳能发电场的规模,为了尽可能地降低发电成本,有必要用一块芯片同时对多台电机进行控制[7],因此选用FPGA来实现对电机的控制。

系统中,涉及到两台步进电机,考虑到两台电机的控制机理是相同的,先设计一台电机的控制系统,另一台电机的控制系统可以直接在FPGA中映射实现。

2 步进电机控制系统设计与仿真分析

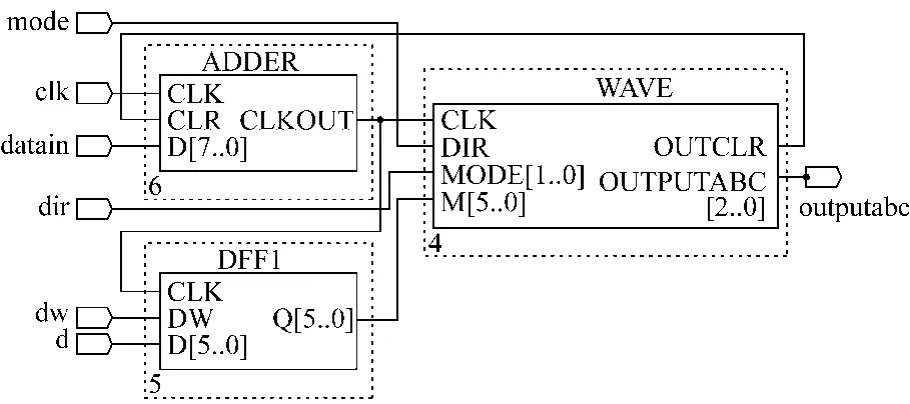

系统设计中,在FPGA中使用VHDL[6]语言编程实现步进电机的加减速、保持控制、正反转控制,以及对步进电机的精确定位,来实现系统对太阳的准确追踪。电机控制系统的顶层电路见图2。

图2 控制器顶层电路图

图2中,clk为时钟信号,此信号由FPGA内部时钟信号分频获得;datain为频率控制字,改变datain的大小能够改变步进电机的速率;dir为步进电机转向控制信号;mode为步进电机运行模式选择信号,这里步进电机可作三相单三拍、三相双三拍、三相六拍转动;dw为定位起动信号;d为定位的步数;outputabc为三相波形输出。

2.1 速度控制单元设计

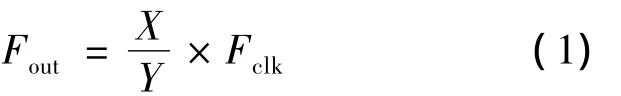

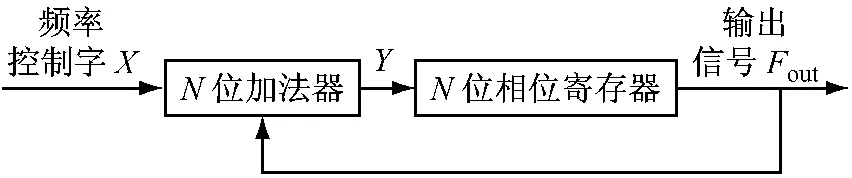

本研究中,对步进电机的速度控制采用的是直接数字式频率合成器(Direct Digital Synthesizer,DDS)技术。DDS是20世纪60年代末出现的第三代频率合成技术,以Nyquist时域采样定理为基础,在时域中进行频率合成,其原理图如图3所示。每来一个时钟脉冲,N位加法器将频率控制字X与相位寄存器输出的相位数据Fout相加,把相加后的结果Y送至累加寄存器的输入端。相位累加器在基准时钟Fclk的作用下,进行线性相位累加。当相位加法器满时会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS的一个输出信号周期。DDS输出信号的频率由式(1)给定:

图3 DDS原理图

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

此处选取基准频率为Fclk,累加器为10位,即1 024=210,假定 X=256,则 Fout=0.25Fclk。这里通过改变输入的datain大小来改变输出频率的大小。

clkout也会发生改变,仿真结果如图4所示。其中clkout为输出频率,clk为参考频率,随着da-tain的改变而改变。

图4 速度调节

从仿真结果可以看出,当datain改变时,输出的时钟频率也相应的发生变化。datain越大,累加器溢出的速率越快,clkout越密,输出频率越高,反之亦然。因此,可以通过控制输入datain值来实现对输出频率的连续可调,从而对电机的速度作出准确控制。同时可知,累加器的位数越多,对输出频率控制的精度也越高。

2.2 转向调节单元设计

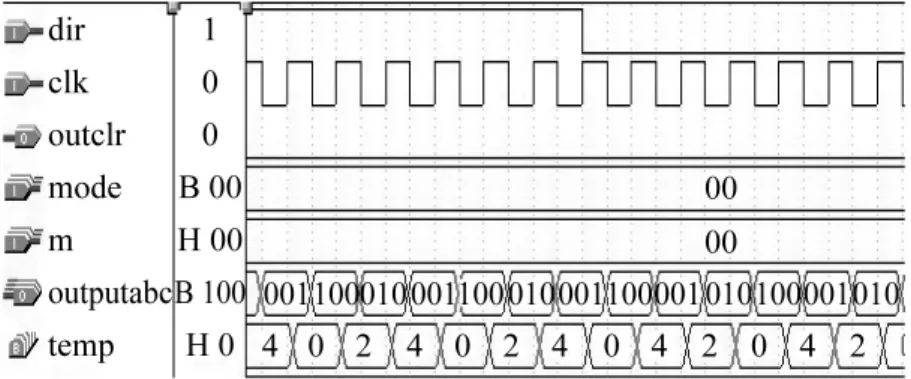

对步进电机转向的调节,采用加减计数器来实现。当电机作正转时,计数器作加计数,通过计数器输出值的不同,系统输出相应的脉冲波形;当电机作反转时,计数器作减计数,系统根据计数器输出的值来输出与之对应的波形。三相单三拍正反转综合的波形仿真图如图5所示。

图5 三相单三拍正反转综合仿真图

由图5可以看出,当dir=‘1’时,temp作加计数,电机三相abc依次为:100-010-001-100,电机正转;当dir=‘0’时,temp作减计数,电机三相abc依次为:001-010-100-001,电机反转。

2.3 精确定位单元的设计

对步进电机的精确定位,只需要控制步进电机的脉冲个数即可,当脉冲个数达到定位要求时,通过异步清零的方式来终止时钟脉冲的输入,使步进电机停止转动。

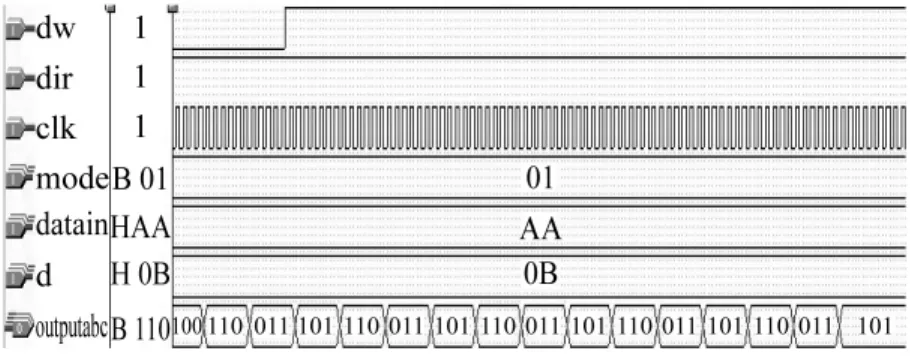

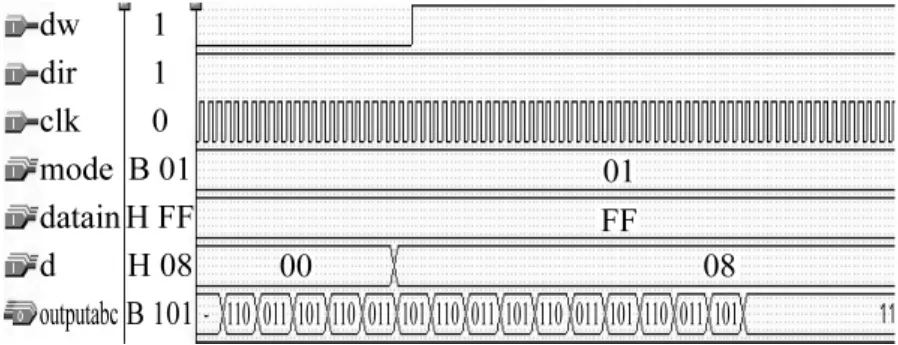

当d=‘0’时,步进电机正常运行,不作定位用;当d≠‘0’时,且定位键dw使能时,步进电机作定位运行。当outclr=‘1’时,步进电机控制脉冲被终止,电机停止转动。步进电机的定位仿真图如图6、7 所示。

图6 三相双三拍定位12步

图7 三相双三拍定位9步

从图6、7可看到,当电机运行达到指定的步数后电机就停止转动,实现了精确定位的目的。

3 电机工作综合仿真分析与电机稳定运行

一般情况下,由于对控制精度和控制效率的要求不同,需要电机在不同的工作模式下实现速度与转向的调节,以达到电机应用过程中的稳定运行。

3.1 电机工作综合仿真分析

下面对步进电机作调速、转向调节、运行模式选择进行综合仿真和分析,综合分析仿真图如图8所示。

图8 综合仿真图

从仿真结果可知,当输入频率控制字datain的大小由66变为D0后,三相abc输出的脉冲宽度发生了明显变化,表明输出的频率发生了改变。通过改变datain的大小,步进电机的速度能够在一定范围内进行连续调整;dir信号由1变到0时,电机由三相双三拍正转变成反转;mode依次为“00”、“01”、“11”时,步进电机分别作三相单三拍、三相双三拍、三相六拍转动;当设定电机的定位数值时,就可以对电机在各种转动模式下进行精确定位。

本文采用FPGA+VHDL对步进电机控制器进行设计。采用VHDL的设计方法有不依赖器件、移植容易、能加快设计的特点。并且,VHDL在现场就能进行修改,与FPGA器件相结合,能大大提高设计的灵活性和效率,缩短产品的开发周期,缩短产品上市应用的时间。VHDL+FPGA的设计方法是数字系统设计的一个创新,也是未来的一种发展方向。

3.2 步进电机稳定运行方案与分析

步进电机驱动执行机构从一个位置向另一个位置移动时,要经历升速、恒速和减速过程。步进电机的失步和过冲直接影响到系统的精度,在步进电机和驱动方式选用合理的情况下,步进电机的失步和过冲往往发生在起动、停止等控制脉冲突变的情况下。因此,对步进电机的加、减速有严格要求,要使步进电机快速地达到所要求的速度又不失步或过冲,其关键在于使加速过程中加速度所要求的转矩既能充分利用各个运行频率下步进电机所提供的转矩,但又不能超过这个转矩。所以对步进电机在起动及停止时的速度进行控制非常有必要,即要求对其进行升降速控制[2]。

通常情况下,步进电机的升速一般有三种选择,一种是直线规律升速,一种是S型曲线规律升速,另外一种按照抛物线规律升速[2]。直线升速比较简单;而按S型曲线规律升速比较接近步进电机的输出转矩随转速变化的规律;抛物线升速规律融合了直线升速规律和S型曲线升速规律的优点,充分利用步进电机低速时的有效转矩,使升速的时间大大缩短,同时又具有较强的跟踪能力。在确定了升速规律后,就可以将曲线离散化,把每步频率的频率系数储存在RAM中,当电机转动到相应的步数,取出对应的分频系数来进行分频以获得所需频率[3]。

4 结 语

太阳能追踪系统对太阳的准确追踪、电机的控制起着至关重要的作用。该文采用FPGA对步进电机进行控制,一方面考虑到FPGA集成度高、可靠性强,增强了整个系统的稳定性;另一方面,考虑到太阳能发电的可观前景,今后太阳能追踪装置肯定将逐渐取代传统的、固定的太阳能发电设备,而FPGA具有资源丰富、I/O管脚多的优点,一片FPGA芯片就可以控制多台电机,这样就能较大幅度地降低太阳能发电场建设的投入,进而降低太阳能发电的成本。本文分析的系统很好地完成了三相步进电机在各种工作模式下的加减速、转向调节和定位的仿真控制。随着近年FPGA芯片不断向高密度、高速度、低价格的趋势快速发展,可以预见FPGA在电机控制领域将有很大的发展空间,FPGA的广泛应用将在能源领域及控制技术方面为我国的节能减排提供重要的技术支撑。

[1]T Kenjo,A Sugawara.Stepping motors and their microprocessor controls,2nd edition[M].Oxford:Oxford University Press,2003.

[2]Tzung-Cheng Chen,Yung-Chun Su.High performance algorithm realization on FPGA for stepper motor controller[C]∥SICE Annual Conference 2008,The University Electro-Communications,2008(1):1390-1395.

[3]Astarloa,A Bidarte,U Zuloaga A,et al.Reconfigurable microstepping control of stepper motors using FPGA embedded RAM[C]∥IECON 2003,The 29th Annual Conference of the IEEE,Industrial Electronics Society,2003(3):2221-2226.

[4]Ngoc Quy Le,Jae Wook Jeon.An open-loop stepper motor driver based on FPGA[C]∥International Conference on Control,Automation and Systems,2007(1):1322-1326.

[5]Vankka,J Waltari,M Kosunen M,et al.A direct digital synthesizer with an on-chip D/A-converter[C]∥Solid-State Circuits Conference,ESSCIRC’1997,Proceedings of the 23rd European,1997(1):216-219.

[6]S Brown,Z Vranesic.Fundamentals of digital logic with VHDL design second edition[M].McGraw-Hill Science Engineering Math,2004.

[7]刘小威,翟超,颜芳.基于FPGA的LAMOS多电机控制驱动系统[J].机械与电子,2008(6):17-19.