无抖动开关的研究与设计

黄秋萍,王汉祥,李富华

(苏州大学,江苏 苏州 215021)

1 引言

数据常常通过人工操作开关的方式进入数字系统。这些开关有很多形式,从计算机键盘的单个按键下的弹簧触点到数控机床上的按钮开关。所有这些机械开关的通用特性是当动作时它们的弹簧触点有抖动的趋势,从而引起持续几毫秒的短时间的接触和断开。

在给定系统中,如果闭合的电气开关代表逻辑1,而断开的触点代表逻辑0,接触抖动会产生严重的问题。因为当想要一个单独的1时可能会产生多个1和0,所以必须在开关输入端设计防抖动电路以防止问题的发生。

2 简单防抖动电路

可将锁存器作为图1所示的非常方便的防抖动电路。

当图1所示的开关打在上边的位置时,电压V(相当于逻辑1)被加到S的输入上,没有电流流进下面的电阻,输入R将对应于逻辑0的接地电位,相当于S=1,R=0;同理打在下边的位置时,相当于S=0,R=1;在拨动过程中相当于S=0,R=0;具体仿真波形见图2。

图2中S高电平前后的小毛刺模拟“抖动”,由图可见Q信号上已无抖动。但这是一种理想情况,当S抖动时R保持为低电平,如果开关从S打向R时,S和R同时发生抖动,其结果见图3。

由图3可见,抖动并未被完全消除。

3 RC防抖动电路

利用RC积分电路来达成杂波的滤除与波形修整的电路,如图4所示。在S1按下的瞬间由于接触弹跳的关系,会使A点电压呈现高速的断续现象,在S1断开时亦然,如图5所示。然而由于电容两端电压需由电压经电阻慢慢充电才会上升,使得B点电位缓步上升;S1断开时,电容电压经R 放电,使B 点电压缓缓下降。此变化经史密特反相修整后,可得到标准负脉冲波输出。

该电路确实消除了抖动现象,但必须用到电阻、电容和史密特触发器,若用在模拟电路中,能与模拟电路的工艺兼容;但在数字电路中就不便于集成,即使能集成,所占的版图面积也较大,下面要介绍的是适合于FPGA实现的防抖电路。

4 用触发器实现的防抖电路

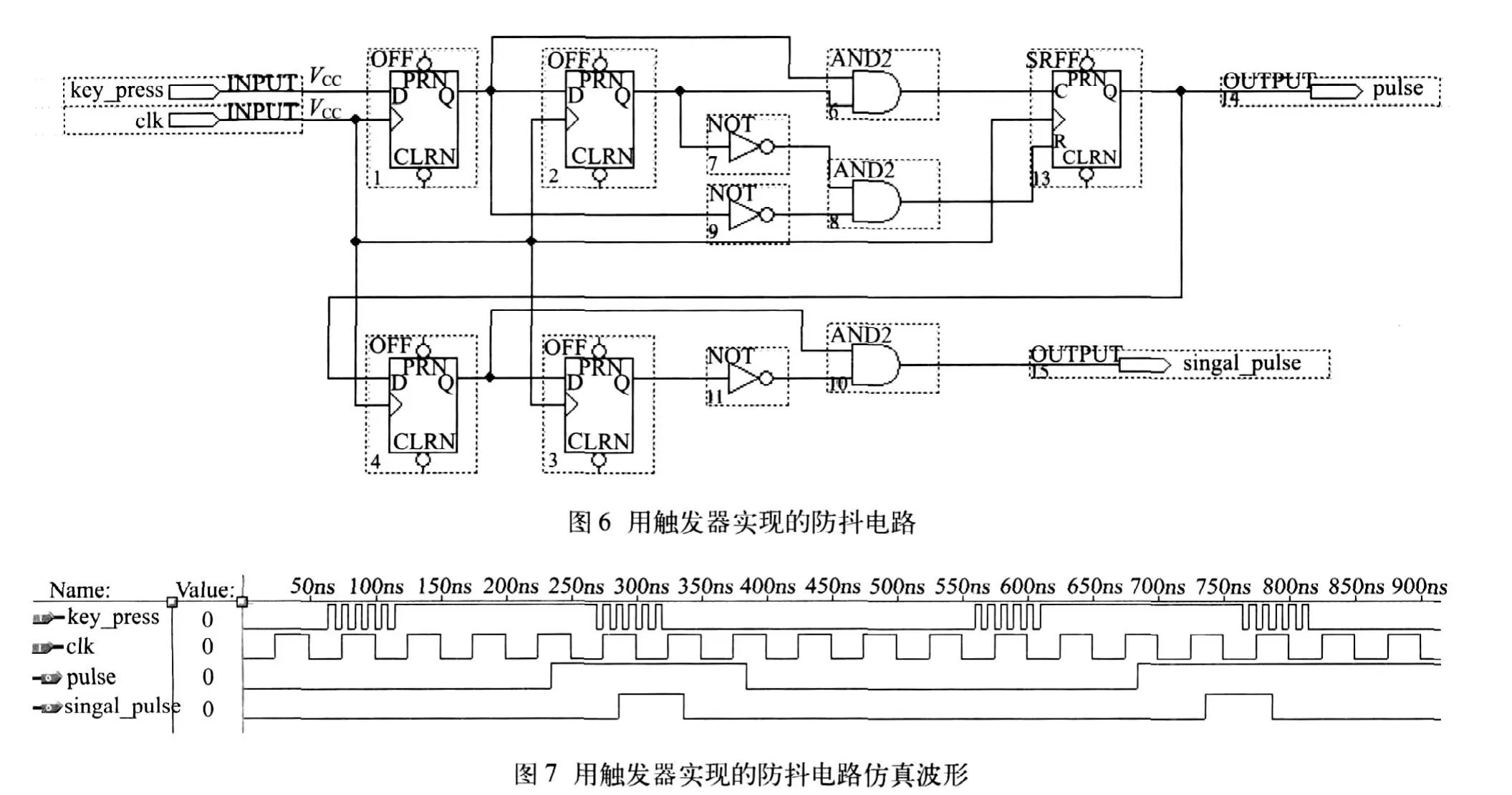

由于FPGA内富含触发器,所以该电路用了四个D型触发器和一个RS触发器,电路上半部分为消抖电路,下半部分为微分电路。

4.1 消抖电路

Key_press信号经过两级D触发器延时处理后(第一级D触发器的同步功效大于延时,所以为了使延时时间准确,延时电路必须有两级),再用RS触发器进行处理。

假设一般人的按键速度是10次/s,亦即按键时间是100ms,所以按下的时间可估算为50ms,如果取样信号clk_div频率为10ms(100Hz),则可取样5次。对于不稳定的噪声在5ms以下,则至多可取样一次。RS触发器前接上与门后,则RS的组态为:(1)S=0,R=0,pulse不变;(2)S=1,R=0,pulse=1;(3)S=0,R=1,pulse=0,即必须抽样到两次1(认为是稳定地按下按键)才会输出1,两次0(认为是稳定地放掉按键)才会输出0,该部分电路已可完成消抖的功能。

4.2 微分电路

为了避免因信号长度不同而使计数器产生错误,再接一级微分电路,然后才接至计数器电路,电路的仿真波形如图7所示。从pulse波形可以发现,由外部输入类似按键的Key_press信号的前后噪声都被消除掉了;而且再经过一次微分后,输出信号single_pulse高电平的宽度只有一个时钟脉冲周期。

该电路适用于FPGA实现的芯片设计,因FPGA内富含触发器,若是ASIC则要制版流片,成本太高且占用了太多的芯片面积,下面要介绍的是适用于ASIC的节省面积的消抖电路。

5 由RS锁存器构建的防抖电路

此电路结构与图1、图4的防抖动电路有部分相似,在这两个电路基础上做了改进,详见图8,对此电路做一简单仿真,似乎并不能起消抖的作用,仿真波形见图9。

对图8在CSMC 0.8μm工艺模型下做瞬态分析可以得到如图10的波形图。

从图10可知,当高低电平变化间隔时间小于6ns时,输出将一直保持高电平,这便意味着该电路能消除6ns以下的抖动,大于6ns的抖动将不能被消除。

另外,靠近S端的两个反相器的宽长比的设置要特别注意,N管的宽长比要大于P管的,通过调节宽长比可以微调防抖动时间。

6 结论

文章对四种防抖动开关电路进行了分析和仿真,这四种电路各有其优缺点,可以根据设计需要分别选用。

[1]James Palmer,David Perlman.Schaum’s Outlines Introduction to Digital Systems[M]. American,McGraw Hill companies,Inc.1993.148.

[2]周润景,图雅,张丽敏.基于QuartusⅡ的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社, 2007.380-381.

[3] 唐光明.基于中断技术的开关软件消抖算法[J].现代机械,2006(3):107-108.

[4]邢远秀,陈姚节.键盘消抖电路的研究与分析[J].中国科技信息,2008(1):67-68.

[5]曾旎,奚大顺,李向阳.按键开关的抖动与消除方法[J].电子世界,2005(9):55-56.