ZVS条件下死区时间控制技术的FPGA实现

郭元振 ,张 彬,马 孜

(1.四川大学 电子信息学院,四川 成都 610065;2.西南技术物理研究所,四川 成都 610041)

将D类功率放大器应用于真空镀膜机中磁偏转电子束扫描电子枪,然而要实现高质量、复杂膜系的镀制,对输出电流的线性度要求比较高,因此,D类功率放大器的线性度成为亟待解决的问题。

D类功率放大器采用开关模式输出,具有很高的效率,但同一桥臂上的两个开关器件不能同时处于导通状态,否则,会在电源和地之间形成一条低阻通路,产生很大的“穿刺”电流,不仅增大了放大器的功耗,而且容易损坏功率器件。为此,必须引入死区时间,死区时间是指从一个开关器件的关断信号发出到同桥臂另一个开关器件加上开通信号之间的时间延迟[1]。然而,死区时间设置过大,将使得输出电流纹波变大,输出电压有效值改变[2],同时,也产生了不必要的损耗。

传统的死区控制电路是由芯片外接电阻电容构成微分电路,进而产生死区时间,但这样占用面积大、不易集成;而由专用芯片实现的死区控制电路,结构简单、抗干扰能力强,但成本高、不易采购,并且不能对死区时间自动调整。本文利用FPGA实现的零电压开关(ZVS)条件下死区时间控制电路,将功率管输出电压信号反馈到功率管的驱动端,进而实现了对死区时间的自动控制和调整,最大程度地减小了死区的影响[3]。

1 死区时间对输出电压的影响及其仿真分析

半桥式功放电路功率级拓扑结构如图1所示,其中CZ是Z点对地的寄生电容,Dn和DP分别是 N管和 P管的体二极管。

图1 半桥式功放电路功率级拓扑结构

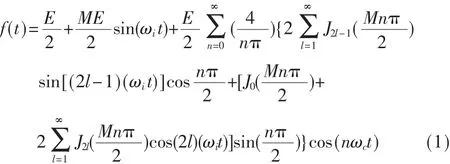

当驱动功率管的PWM波未加入死区时间时,设调制波为正弦波,采用平均对称规则采样方法所得到的PWM波的傅里叶级数为[4]:

其中,E为 PWM波幅度,M为调制系数,ωi为调制波角频率,ωc为载波角频率。由上式可知PWM波中不含低次谐波,仅含 ωc、2ωc、3ωc及其附近的谐波,因此很容易滤除。

设死区时间为td,Q1从导通到关断、Q2从关断到导通,如没设置死区时间,Z点电压应由+U下降到0,在死区时间内由于自感作用,下桥臂二极管续流,Z点的电压钳位到-Ud,相当于增加了一个宽度为td、幅度为Ud的电压脉冲;Q1从关断到导通、Q2从导通到关断时,如没设置死区时间,Z点电压应由0上升到+U,但是由于死区时间的设置,Z点电压被下桥臂二极管钳位到-Ud,这相当于损失了一个宽度为td、幅度为U,同时增加了一个宽度为td、幅度为Ud的电压脉冲。

从总体上看,死区时间的影响可产生一系列的偏差电压。如果忽略高次谐波,这一系列的偏差电压可以等效为矩形波的偏差电压 uer,设其幅值为 ΔU,则有 ΔU=(U-2Ud)Nfitd。忽略PWM调制波固有的谐波含量,而只考虑死区时间对输出电压的影响,将偏差电压uer用傅里叶级数展开为:

其中,U为A点电压幅度,Ud为续流二极管阈值电压,N为调制波周期内矩形波的个数,fi为调制波频率。

由式(1)、(2)得出输出电压波形的谐波畸变率[5]:

其中,A为功放的放大倍数,Un为第n次谐波电压,U1为基波电压。

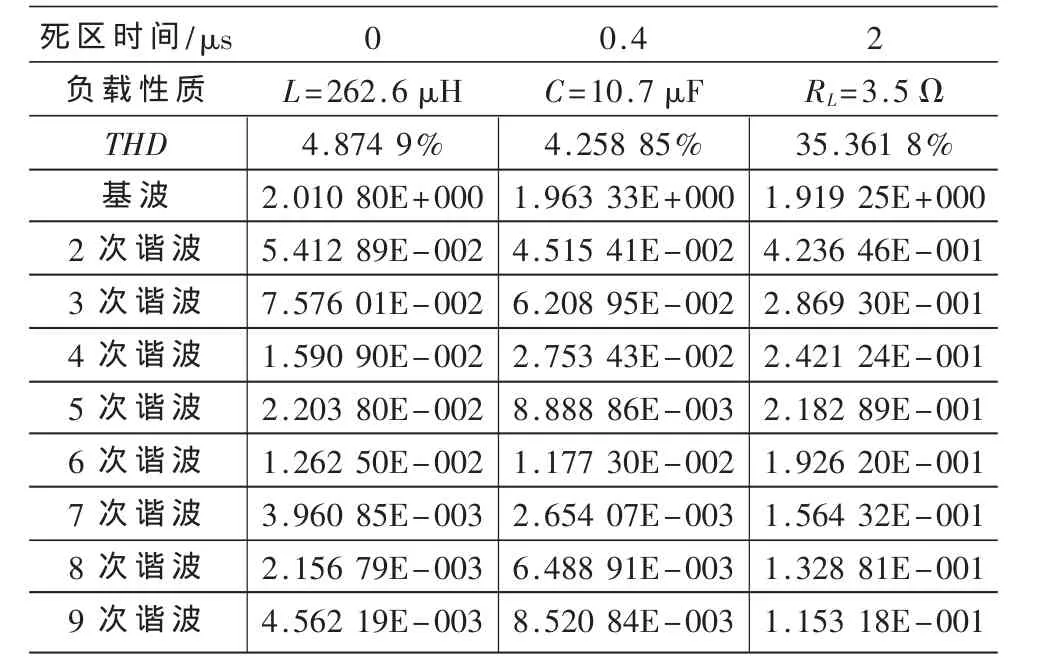

表1所示,电源电压为12 V、调制波频率为500 Hz,载波频率为50 kHz时,负载电流谐波畸变率及各次谐波电流的仿真数据。

通过分析和仿真结果,引入死区时间造成的影响如下:

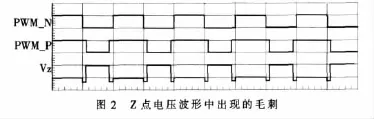

(1)在输出波形中产生毛刺,使输出电压增加了附加的直流分量、基波、2n+1(n=1,2,3…)次谐波分量。毛刺受到死区时间和负载电流的影响[6],死区时间越长,体二极管导通的时间就越长,毛刺的宽度也就越宽,Z点的电压如图2所示。由于在本设计中滤波器截止频率较低,L值较大,因此电感电流一直为正(称为重载)。故实际输出谐波电压的含量主要取决于死区时间引起的谐波。从式(3)中可看出,引起开关功率放大器THD增加的原因是死区时间的设置和开关频率的选取。死区时间和开关频率越大,THD也就越大。

表1 仿真结果

(2)造成功率损耗,输出波形中出现的毛刺包含一定的能量,这部分能量消耗在体二极管中,如果把这些毛刺看成方波信号,则体二极管消耗的能量[7]为:

能量是以热量的形式散发出去的,会对芯片的散热造成很大的问题。从式(4)可以看出,要减小这部分能量,必须要减小死区时间和采样频率。

2 电路设计

2.1 自适应死区时间控制电路原理

由以上分析可知,在死区时间内,由于功率管中的体二极管的续流作用,在Z电位上升或下降时,都会钳位到-Ud,这样可以检测Z点和上下功率管栅极电位,以此减小或消除毛刺。即当Q2栅极电位为低且Z点电位小于 0时,开通 Q1,死区时间结束,此时,毛刺消失;当Q1栅极电位为高且Z点电位小于0时,开通 Q2,死区时间结束,毛刺消失。这种方法称为ZVS控制,将ZVS与PWM结合称为ZVS-PWM控制技术[3]。

本文采用FPGA实现,其优点是抗干扰能力强、采购容易、设计灵活方便、开发过程投资小、内部资源丰富,并可实现系统编程。

2.2 ZVS条件下死区时间控制电路的FPGA实现

FPGA是在CPLD基础上发展起来的新型高性能可编程的逻辑器件,因技术成熟,种类繁多,内部资源丰富已得到了广泛应用。本设计采用Altera公司推出的EDA编程软件Quartus II,该软件可采用原理图设计、硬件描述语言、IP Core等输入方法,支持 VHDL、Verilog HDL和AHDL等硬件描述语言,本文采用Verilog HDL语言对ZVS条件下死区时间控制电路进行描述,所设计死区时间控制电路由信号调整、死区时间控制、过流保护、逻辑综合处理等环节组成,其相互关系如图3所示。

图3 死区控制电路原理框图

信号调整:PWM控制信号在传输过程中由于路径延迟以及电磁干扰等,使信号上升、下降沿变缓,并引起振荡,因此前端加信号调整环节以改善上升、下降沿质量,并去除振荡。

死区时间控制:进行ZVS检测,避免同一桥臂上的功率器件在开关过程中同时导通,并将检测信号反馈到输入端进而抑制毛刺的产生。

过流保护:当上下功率管出现过流或短路时,能够调整输出正确的信号。

逻辑综合处理环节:以上各环节产生的控制信号以及经过整形的控制信号同时进入逻辑综合环节,按特定控制规律产生的控制信号分两路输出,经驱动环节后分配给上、下两个功率器件。

为了实现以上各环节功能,采用Verilog HDL硬件语言,利用modelsim和Classic Timing Analyzer软件分别进行功能仿真和静态时序分析,利用Synplify Pro综合生成电路。部分源代码及分析如下所示:

3 死区控制电路仿真

本设计选用Altera公司Cyclone系列的EP1C3T100C6器件,电路功能仿真结果如图4所示。

静态时序分析报告中指出时钟最大工作频率可达100 MHz,最差路径延迟远小于10 ns,完全能够正确采集到最小的PWM脉冲。

死区时间在D类功率放大器中起着关键性的作用,对死区时间的有效控制不仅可以减小器件的损坏率,而且能够降低功率管的损耗,提高放大器的线性度。本文基于FPGA设计的电路,可以良好地控制死区时间,保证了电路的正常运行。

[1]杨德刚,赵良炳,刘润生.死区时间的三个要素及无死区控制[J].电力电子技术,1999,6(3)∶14-17.

[2]章建峰.逆变器死区时间对输出电压的影响分析[J].电力 电 子 技 术,2007(8)∶11-13.

[3]陈敏,吴金.采用ZVS条件控制的 DC-DC同步整流技术[J].电子器件,2004,27(3)∶428-431.

[4]陈国呈,周娟.PWM变频调速技术,北京∶机械工业出版社,1998.

[5]朱高峰,吴黎明,王桂棠,等.D类音频功率放大器的关键技术声学技术[J].2006,25(5)∶453-456.

[6]来新泉,韩艳丽,叶强,等.驱动死区时间控制及其对 D类音频功率放大器稳定性的影响[J].中国集成电路,2008(1)∶30-35.

[7]应建华,付增功,周欢欢.D类音频功率放大器中的死区控制电路设计[J].华中科技大学学报(自然科学版),2008(10)∶98-101.