一种用于D/A转换器的带隙基准电压源设计

王金斗

(石家庄职业技术学院 电气与电子工程系,石家庄 050081)

0 引言

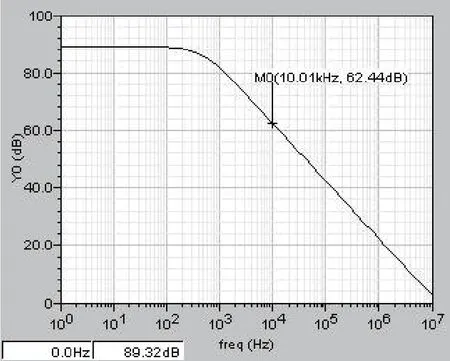

带隙基准源是集成电路中的一个单元模块,也是D/A转换器中的一个重要模块,基准源输出的基准信号稳定,具有与电源电压、工艺、温度变化几乎无关的突出优点。为了更好地适应数模混合集成电路的发展,基准电压源的设计性能要求进一步提高,输出低电压,且具有高电源抑制的电压基准源已经成为模拟设计的目标。基准电压源在DAC电路中占有举足轻重的地位,其设计的好坏直接影响DAC的精度,本文采用SMIC 0.18μm 1P6M工艺设计了一种低温度系数高电源抑制比的CMOS带隙基准电压源,该电路PSRR在低频时为89dB,在10 kHz 时仍能达到62.4dB,温度系数为4.1ppm/℃,能够很好的应用于各种DAC系统中。

1 带隙基准电压源的基本原理

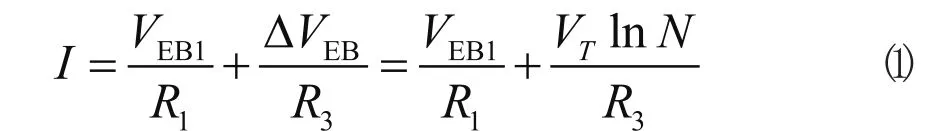

带隙基准电压源的核心电路如图1所示,两个PNP管分别并联两个串联的电阻,适当调节它们的阻值比率进行分压,运算放大器使P和N点电压相同,取R1a=R2a,R1b=R2b,这样节点1和2的电压也相同。晶体管Mb1、Mb2、Mb3使用相同的尺寸,使得三个支路的电流大小相同。每个支路的电流是

其中R1=R1a+R1b=R2a+R2b,VT是热电压,Q2发射结面积是Q1发射结面积的N倍,那么参考点输出电压是

VEB1具有负的温度系数,VT具有正的温度系数,通过调节R1与R3的比值,得到一个与温度无关的,具有高电源抑制比的基准电压。VBE的温度系数约为-1.8mV/K,VT的温度系数约为0.086mV/K,通过选择适当的R1、R3和N的取值,可以使得正负温度系数相抵消,基准电压源的输出与温度变化几乎无关。在本设计中,三极管Q2发射结面积设计为Q1的8倍(N=8),R3≈0.1R1。

图1 带隙基准电压源核心电路

2 带隙基准电压源的电路实现

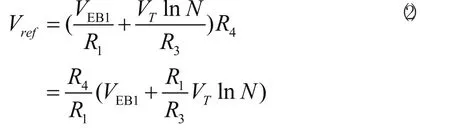

本文设计的带隙基准电压源的完整电路如图 2所示。图中I部分为运算放大器电路,II部分为启动电路,III部分为带隙基准电压源的核心电路。

M1~M11构成一个简单的两级运算放大器电路,M1~M4构成有源负载的差分放大器,M5为差分放大器提供工作电流。M6、M7构成共源放大器,作为运放的输出级。CC为米勒补偿电容,对电路进行频率补偿。电阻RC消除电路的零点。该运算放大器使用PMOS管作为差分输入对,相比NMOS管具有较小的输入噪声,并采用电阻分压的方法来减少差分对管的共模输入电压。

M8,M9,M10,M11构成的电流镜为运算放大器的输入级提供偏置电流,电路采用自偏置的方式即电流源M11的偏置电压由运放的输出端提供,这样电路就形成了一个自反馈回路,M6的漏极输出通过电流镜M11偏置电流源M5和M7。只要基准源的输出电压Vref保持不变,这种结构就能使运算放大器工作在稳定的状态。

电路中“简并”偏置点的问题由MS1~MS4组成的启动电路来解决。启动电路同时为Q1和运算放大器提供启动电流。MS1和MS2构成一个反相器,当电路工作在零状态时,Mb1~Mb3和MS1的栅极电压接近电源电压VDD,经过反相,MS1和MS2的漏极电压会变得很低,促使MS3和MS4导通,进而MS3向运算放大器注入电流,MS4向带隙核心注入电流,使电路正常工作。电路正常工作后,Mb1~ Mb3的栅极电压降低,Mb1的漏极电压拉高。当MS1的栅极电压降低时,MS1和MS2的漏极电压被拉高,从而关断MS3和MS4。MS1和 Mb1~ Mb3的尺寸相同,增加电路的匹配性能。MS2的宽长比应远远小于1,保证电路正常工作时,MS3和MS4管彻底关断,为了防止工艺偏差等因素,选取MS2的宽长比是仿真结果的2倍。另外,在保证运算放大器稳定性的前提下,可以通过提高放大器的开环增益提高电源抑制,从而改善基准电压源电源抑制性能[4]。

图2 带隙基准电压源完整电路

3 电路版图设计

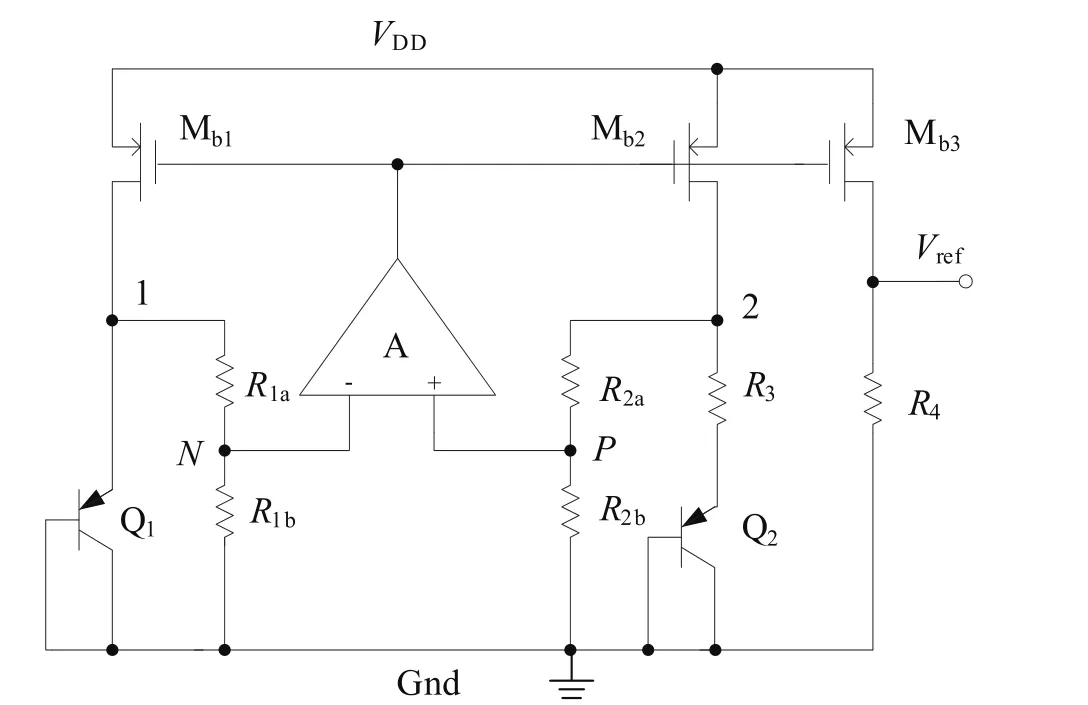

在本电路版图设计中,充分考虑了器件的匹配性和布局布线的问题。在版图中为了保证Q2、Q1的比值 N=8,采用3×3阵列,将Q2分成8个与Q1相同尺寸的管子并联,Q2围绕在Q1的周围,增加匹配性,减少引起的失调。在集成电路制造中,电阻值的绝对误差比较大,但各个电阻的阻值之间的相对误差要小很多,所以R3≈0.1R1的精度容易保证。在版图设计中,考虑到电阻R1和R3的相对误差对温度补偿特性具有很大影响,为了进一步减小相对误差,对R3和R1电阻进行对称排列,并在电阻的四周加上dummy电阻,减小边界环境的影响,提高电阻的匹配性。 在本电路中,运放的失调电压是影响带隙性能的主要因素之一,所以M1和M2的版图采用交叉耦合的结构,增加匹配性,减小运放的失调电压。图3所示为D/A转换器带隙基准电压源的版图。

图3 带隙基准电压源电路版图

4 仿真与结论

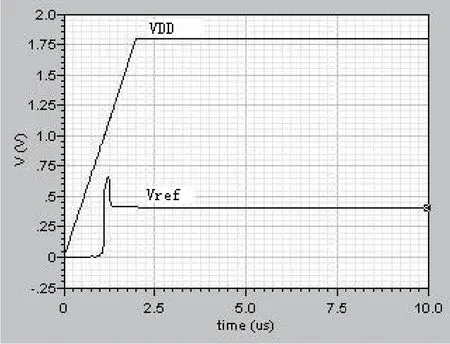

本文的带隙基准电压源电路采用S M I C 0.18μm CMOS工艺设计。基于Cadence Spectre工具的后仿真,结果表明,该电路可以在1.5~2.4V电压、在不同的工艺角下均能正常工作。在1.8V电源电压下,27℃时基准输出为406.6mV,功耗为0.23mW。电路在温度-40~125℃范围内,基准电压输出与温度的关系如图4所示,基准输出电压变化0.278mV,温度系数为4.1ppm/℃。从频率响应曲线图5可以看出,电路具有较高的电源抑制比,在低频时89dB。在10kHz时PSRR仍能达到62.4dB,启动电路的仿真结果如图6,电路能快速响应。本文设计的电路结构简单,可以为高速DAC提供稳定的电压,也可以广泛应用于其他系统中,具有较高的实用价值。

图4 基准电压源的温度特性

图5 电源抑制比

图6 启动电路

[1] 周玮,吴贵能,李儒章.一种二阶补偿的CMOS带隙基准电压源[J]. 重庆邮电大学学报(自然科学版),2009,(01).

[2] 李亮,陈珍海.一种共源共栅自偏置带隙基准源设计[J].电子与封装,2010,(01) .

[3] 吴宗桂,邓爱枝,秦水介,杨发顺.一种具有高电源抑制比的带隙基准电压源[J].微电子学,2009,(04).

[4] 张正旭,李少青,马卓,肖海鹏.多路V/I输出的高性能CMOS带隙基准源[J].微电子学,2009,(04).

[5] 周晏,蒋林,曾泽沧.一种结构简单的CMOS带隙基准电压源设计[J].微计算机信息,2009,(19).

[6] 徐静萍.低电压、高PSRR的带隙电压基准源[J].西安邮电学院学报,2009,(01).

[7] H.S Kuok.An improved bandgap reference with high power supply rejection.ISCAS,2002,5:V833-V836.