基于ARM Cortex-M3的过采样技术

晏英俊,张自强

(上海师范大学通信工程系,江苏上海 200234)

文中在通过对过采样技术的分析,将此技术应用在 TI公司 LM3S8962片内 ADC上,在不使用昂贵片外 ADC的情况下同样获得较高的分辨率。既节约了成本,又节省电路板空间,同时也提高了系统整体可靠性。

1 过采样技术分析

1.1 过采样原理

过采样是对待测数据进行多次采样,获取样本数据,累计求和这些样本数据,并对它们均值滤波,减小噪声后最终获得采样结果。过采样在一定条件下能够提高信噪比(SNR),同时使噪声减弱,从而提升测量分辨率。过采样技术将采样频率提高到被采样频率的 4倍,能过滤掉高于 3 fb的分量,用数字滤波器过滤 fb~3fb的分量,最终有用分量被完全保存下来。若采取足够多次采样,则能重现原始信号。式(1)是过采样的频率要求

式(1)中,Fo为过采样频率;n为希望增加的分辨率位数;fb为初始采样频率要求。

1.2 过采样与噪声、分辨率的关系

在提出过采样与噪声的对应关系之前,对量化噪声作一简单描述。量化误差是由相邻 ADC码的间距所决定,因此相邻 ADC码之间的距离为

式(2)中,N为 ADC码的位数;Vr为基准电压。式(3)为量化误差 ed的关系式。

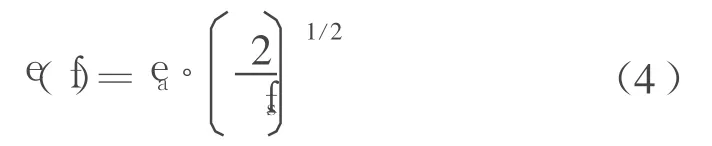

奈奎斯特定理指出,如果被测信号的频带宽度小于采样频率的 1/2,那么可以重建此信号。现用白噪声近似描绘实际信号中的噪声,在信号频带中的噪声能量谱密度为

式(4)中,e(f)为带内能量谱密度;ea为平均噪声功率;fs为采样频率。

ADC量化噪声的功率关系如式(5)所示。由于量化噪声会引发固定噪声功率,因此针对增加的有效位数能够计算过采样比

式(6)中 P为过采样比;fs为采样频率;fm为输入信号最高频率。低通滤波器输出端的带内噪声功率见式(7),其中 n2是滤波器输出的噪声功率

由此可见,过采样能减少噪声功率却又对信号功率不产生影响,在减小量化误差的同时,能够获得与高分辨率 ADC相同的信噪比,从而增加被测数据的有效位数。通过提高采样频率或过采样比可提高ADC有效分辨率。

2 过采样满足条件及操作步骤

对于过采样,理论上需要信号有一定噪声,并且必须近似白噪声,幅度足够大。若噪声信号不能满足前面讲述的理论要求,就需要引入噪声激励。因此,选用周期性噪声作为激励信号。同时对激励噪声有一定要求:激励噪声幅度≥1 LSB;噪声均值在添加激励噪声时必须是 0[4]。

在理解过采样理论及需要满足的条件后,出于对具体应用的考虑,设计了过采样的操作步骤,概括如下:

(1)判断被采样信号是否有噪声,如果没有噪声,则叠加周期性激励噪声。

(2)对信号进行 4n次过采样(n为希望增加的分辨率位数)。如果使用片内 10位 ADC,希望得到 14位的 ADC精度,则需要 44即 256次 10位的过采样。

(3)抽取数字序列,对各个采样值进行累加。

(4)对累加后的采样数据,若提高 n位精度则右移 n位,最终得到过采样值。

3 LM 3S8962实现 ADC过采样

3.1 Cortex-M3内核特点介绍

在 ADC过采样设计中,选用 TI公司 ARM Cortex-M3芯片,主要原因是其功能强大、高性价比的Cortex-M3内核,使过采样的效率与精度得到进一步提升。该内核具有如下特性[1]:

(1)采用 ARMv7M架构,在 ARMv4T架构基础上扩展了 36条指令。

(2)基于哈佛结构,数据与指令可同时从存储器读取,并行执行多个操作,加快程序执行速度。与ARM7TDMI-S相比,比 ARM指令每兆赫效率提高了 35%,比 Thumb指令效率提高了 70%。

(3)带有多种睡眠和唤醒模式,实现产品的低功耗。

(4)单周期乘法、乘 -加、硬件除法指令,实现快速运算。

(5)低延迟中断处理:支持 8层硬件中断嵌套,末尾连锁功能,高优先级中断迟来处理。

3.2 过采样的软件实现

(1)外设初始化。

在软件实现过采样之前,必然要对各个模块进行初始化和配置。初始化定时器、ADC、UART等模块,定时器模块用来提供系统时钟周期,配置 ADC的触发模式和采样速率,利用 UART将测量值传递给PC,方便查验是否正确。

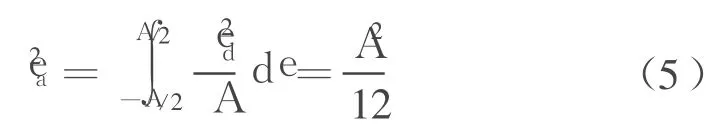

(2)产生 PWM信号,作为噪声。

为了保证过采样原理应用的可靠性,引入噪声激励信号。而为了避免激励噪声出现的误差,使用内部的 PWM信号发生器产生周期性和对称性很好的 PWM波,作为激励噪声。产生噪声步骤如图 1所示。

图1 产生PWM信号

(3)数据的采集、滤波及抽取。

在过采样中所做的数字平均滤波仅提高了平滑度,精度却并没有增加,抽取过程才是真正意义上的提高精度。额外的 K次采样,按照常规平均那样进行累加,但并不是直接将结果除以 M,而是右移 N位(N是期待所增加的额外精度),得到更精确的采样结果。

过采样算法如图 2所示。对 TI的 LM 3S8962芯片,将 10位 AD值的精度提高到 12位的方法,直接调用寄存器读取函数 HWREG访问 FIFO缓存区,经过两次循环,将从 FIFO中收集到的 16个 10位转换值相加,产生一个 14位结果,右移 2位后就得到所希望的 12位 AD值。

图2 12位过采样算法

4 应用分析

转换速率、稳定度和分辨率是模数转换器的衡量标准。为了能够清楚地看到利用过采样技术后对 AD值改善的效果,采用 LM3S8962芯片进行了 12位ADC过采样实验。根据显示的实验数据和测量情况,给出并分析了指标的改善情况。

对于转换速率,使用片内定时器进行测量,在CPU为 50 MHz时钟频率状态,ADC的采样速度为100 kHz时,采样连续触发模式进行 1次 12位过采样时间是 52μs,由于在数据转换的同时还要访问数据缓存区,因此再加上 64μs才是它的实际速度。

对数次采样后获得的值进行数字滤波,滑动平均后,得到较为稳定的数据值,通过串口传送过采样后的数据结果如图 3所示。1组数据有 6 bit,其中前3 bit是原来的 10位采样值,后 3 bit是 12位过采样值。从图 3中能够得知,12位过采样分辨率的值比10位采样值的分辨率值更稳定。

图3 10位采样值与 12位过采样值比较图

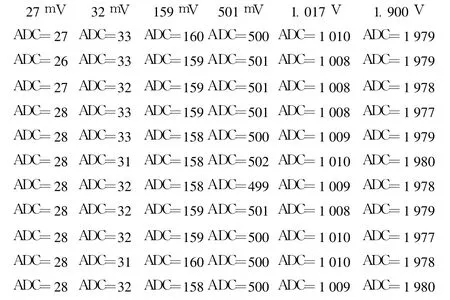

为了验证位数越高,采样精度越高,做了一个13位的过采样实验。采样过程中,循环 8次,获得64组 AD值,并利用分段折线法校正非线性误差,将采样值转换为标准电压值。从图 4中可以看出,过采样后的电压值波动很小,效果尤为明显。

图4 高精度13位过采样值

5 结束语

文中从过采样的频谱特性出发,分析了过采样技术的基本原理。随后采用TI公司高性价比的 Cortex-M3内核 ARM,利用过采样技术提高了测量值的分辨率。实验结果表明,利用过采样技术既能降低成本,又能使外围电路得到简化,它与 Cortex-M 3内核相结合后,更能提高系统的运行速率、可靠性与稳定性。这种结合方式对于检测、监控等领域起着积极作用,具有一定的推广和实用价值。

[1]周立功.Cortex-M3开发指南——基于LM 3S8000[Z].广州:广州致远电子有限公司,2007.

[2]胡广书.数字信号处理理论、算法与实现[M].北京:清华大学出版社,2003.

[3]刘青兰,方志刚.利用过采样技术提高 ADC测量分辨率[J].现代电子技术,2007(12):74-76,79.

[4]牛睿,刘飞.基于AVR单片机的过采样原理的实现方法[J].自动化与仪器仪表,2008(3):72-74.

[5]王辉,李奇,倪超.基于DSP的过采样技术[J].电子工程师,2003,29(4):44-46.