一款新颖的带隙基准电压源设计

贺 炜

(西安邮电学院电子工程学院,陕西西安 710121)

电压基准是芯片设计中一个至关重要的组成单元,它直接影响着整个电子产品的性能。高精度是当今集成电路发展的特点之一,随着集成电路以摩尔定律的发展,人们对电路指标的要求也日趋提高。因此,高精度、高性能的基准源对于集成电路芯片是必不可少的。本文设计了一款高性能的基准电路,具有较小的温度系数,同时在 2.3~6.5 V的电源电压范围内具有较低的功耗和较高的电源电压抑制特性,适用于各类对精度要求较高且功耗低的集成电路芯片。

1 基准工作的基本原理

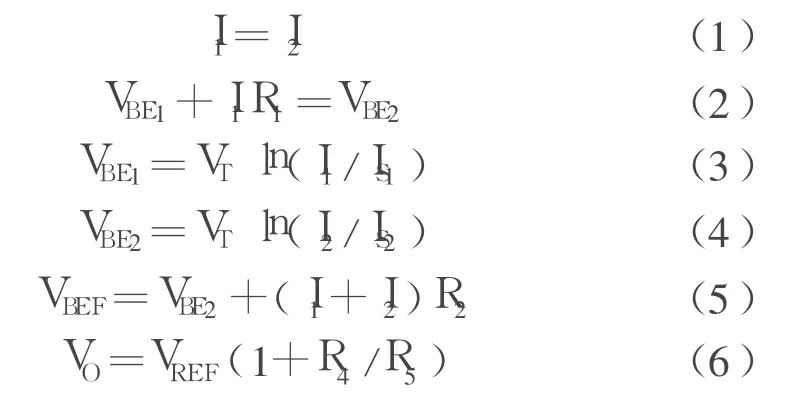

图1为典型的与温度无关的带隙基准电路架构图[3]。它的原理就是利用三极管基极—发射极电压ΔVBE的负温度系数和两个三极管基极—发射极电压差值 ΔVBE的正温度系数相抵消来产生零温度系数的基准电压。如图 1所示,图中 MP1、MP2为 LDMOS管[1],VDD的大部分压降均落在 MP1、MP2上,因此该电路可以承受较高的电源电压。若忽略三极管的基极电流,则有

图1 传统高电源电压基准

由式(1)~式(6)式可以得到

其中,N=IS1/IS2为 QN1和 QN2的发射极面积之比。VBE2的温度系数[2]为 -1.5 mV/℃,VT的温度系数为+0.086mV/℃,所以选择适当的 N值和 R2/R1的比值,就可以得到零温度系数的输出电压。另外,调节R4和 R5的比值,可以得到期望的基准电压,且不会改变已调整好的零温度系数特性。

2 新颖的带隙基准电路

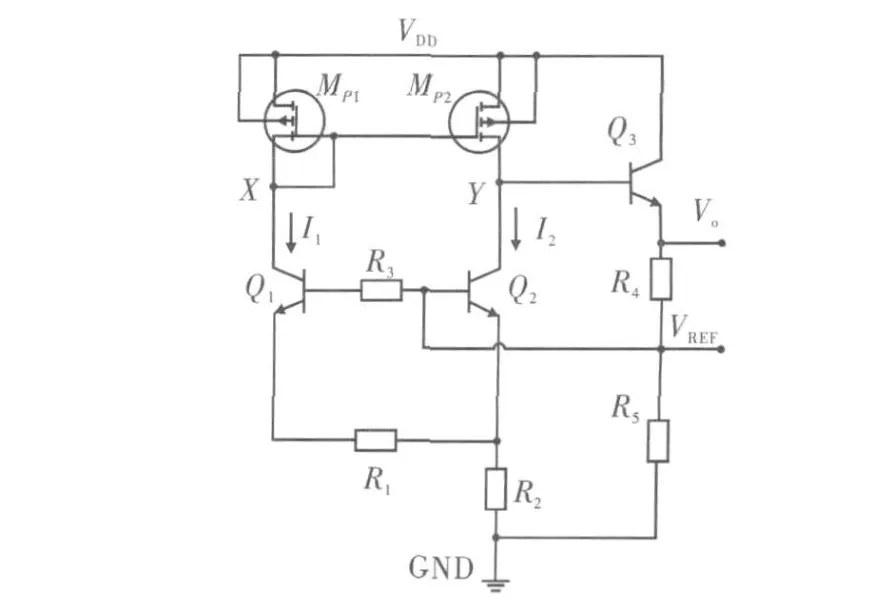

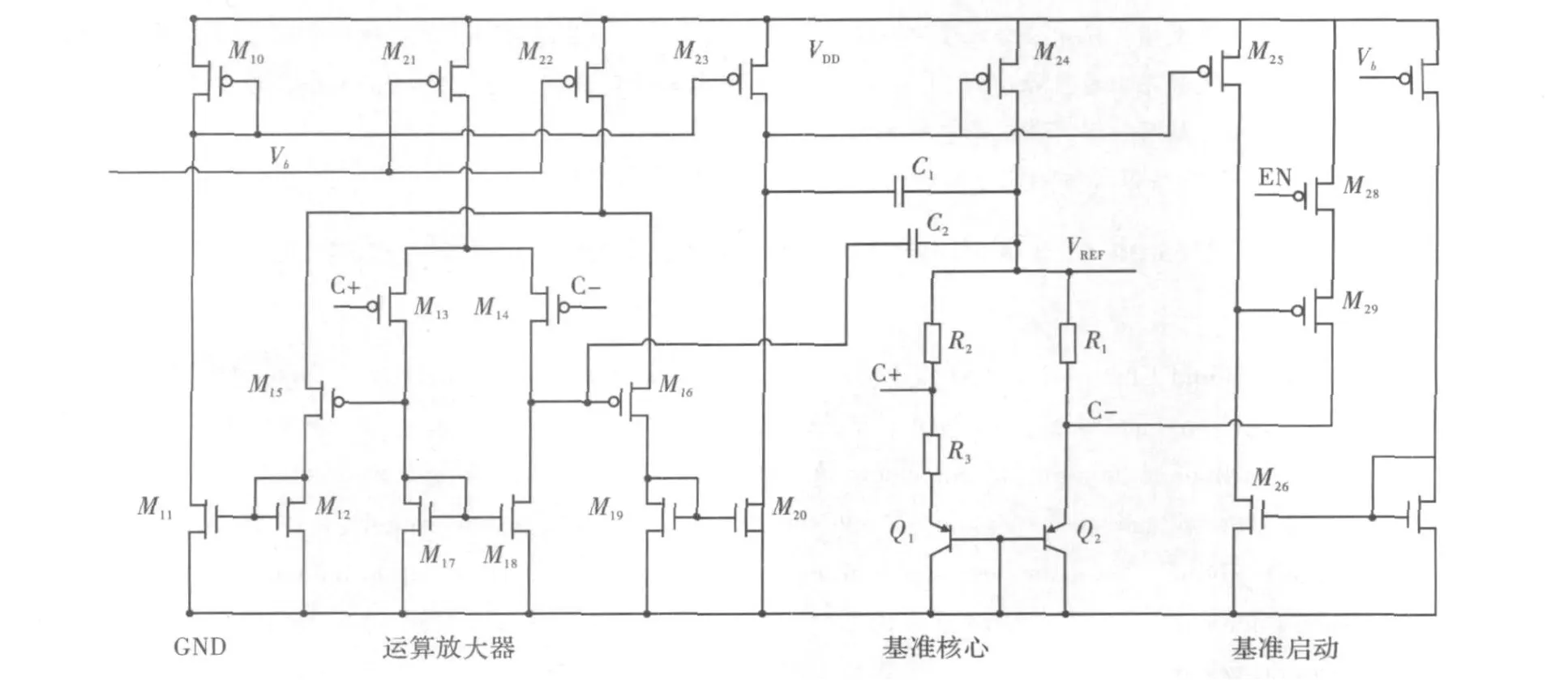

如图 2即为所提出的基准电压电路。该电路由偏置、运算放大器、基准核心和基准启动 4个部分构成。核心电路的原理如前文所述,下面对运放、启动作具体阐述。

图2 带隙基准电路具体线路图

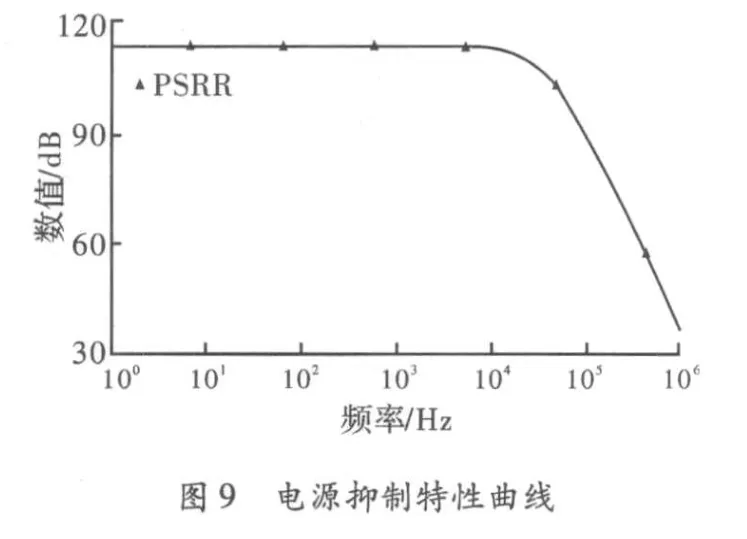

该电路的运放如图 2所示,运放的主要作用是保证 ΔVBE的精准性。然而运放的失调是一个主要的误差源。假设输入端的失调电压为VOS,经过计算可以得到

这里的关键问题是失调电压被放大了(1+R2/R3)倍,在 VREF中引入了误差。更重要的是 VOS本身随温度变化,更增大了输出电压的温度系数。因此要尽量减少失调电压。而引起失调的因素有很多,如电阻间的不匹配,晶体管的不匹配,运放输入级晶体管阈值电压的不匹配,以及运放的有限增益等。这里主要通过提高运放的增益和精确的版图设计来改进。如图 2所示,基准中采用了多级差分结构的运放来提高其增益,增大负反馈的深度,减小失调。然而,运放级数的增多会增加电路的功耗,因此设计运放的偏置电流为与电源无关的较小量,使其工作在饱和区边缘,这也使得电路具有较宽的电源电压范围。

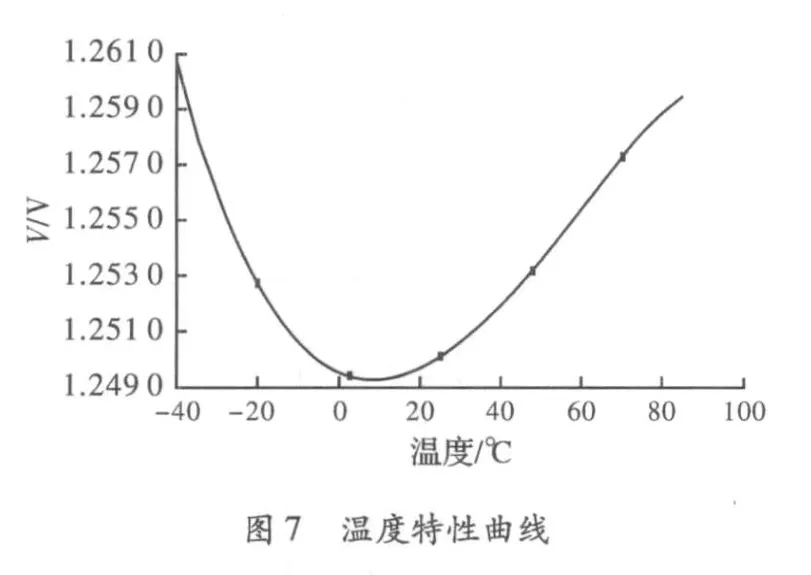

PSR是表征电源抑制能力的交流小信号参数,它的定义为输入电压的变化与输出基准电压的变化之比。在低频情况下,基准的 PSR和运放的增益呈成正比,因此运放的环路增益越大,输出 VREF对电源VDD变化的抑制性就越强[1]。

而该电路的启动部分由 M25,M26,M27,M28,M29和 M30组成,Vb由偏置部分产生,EN为使能信号,正常工作时为低电平。当 EN为低时,且 Vb达到一定电平时,M30导通,M30,M27支路产生电流,使 M26和 M27的栅电位升高,M26便将 M29的栅电位拉低,M28,M29支路产生电流,使基准部分开始工作。设计 M25的宽长比远大于 M26的宽长比,使得基准正常工作后 M28的栅电位为高,关断 M28,M29支路,启动部分与基准脱离。

3 仿真结果

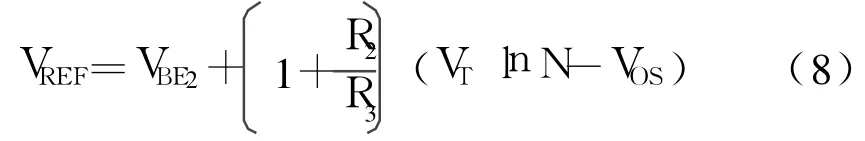

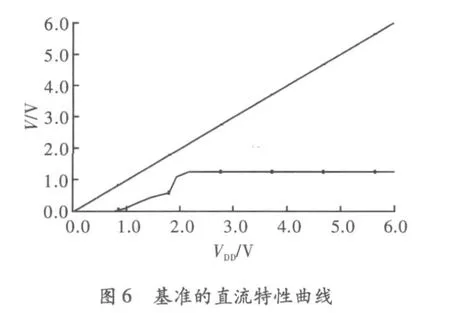

对设计的带隙基准电路进行了性能指标的仿真。使用 HSPICE工具,基于Hynix 0.5μm CMOS工艺,仿真条件为 25℃下全典型模型。从图 6中基准的直流特性可见,电源电压在 1.5~6 V之间变化时,基准输出仍保持良好的稳定性;图 7为基准的温度特性曲线,当温度从 -40~100℃变化时,基准电压的变化仅为 2.2 mV,温度系数为 13.7×10-6/℃,显示了低温漂的特性;图 8是基准环路稳定性的仿真曲线,基准的环路增益为 110 dB,相位裕度为 67°;图 9是基准的电源抑制特性的仿真波形,低频时 PSR为-117 dB。仿真结果都满足性能指标。

4 结束语

本文设计了一种采用 CMOS工艺的高精度低功耗带隙基准电路,电源电压的工作范围为 2.3~6.5 V。当温度从 -40~100℃变化时,基准电压的温度系数为 13.2×10-6/℃,低频时的电源抑制能力为-117 dB。电源电压为 3.3 V时的工作电流仅为3μA。仿真结果显示该电路具有良好的特性。

[1]方邵华,何杞鑫,姚云龙.一种适用于高压集成电路的新型 LDMOS器件[J].微电子学,2003,33(2):105-108.

[2]Razavi B.模拟CMOS集成电路设计[M].陈贵灿,译.西安:西安交通大学出版社,2005.

[3]Brokaw A P.A Simple Three-Term inal ICBandgap Reference[J].IEEE J.Solid-State Circuits,1974, 9(6):388-393.

[4]Jacob Baker R,Harry W Li,David EBoyce.CMOS电路设计◦布局与仿真[M].陈中建,译.北京:机械工业出版社,2006.

[5]张家川,刘伯安.新型低电压能隙基准电压源[J].半导体技术,2006,31(8):591-593.

[6]Khong Meng Tham,Krishnaswamy Nagaraj.A Low Supply Voltage High PSRR Voltage Reference in CMOS Process[J].IEEE Journal of Solid-state Circuits, 1995, 30(5):586-590.

[7]Peng Xiaohong,Sansen Willy.Transconductance with Capacitances Feedback Compensation for Mu ltistage Amplifiers[J].IEEE Journal of Solid-state Circuits, 2005, 40(7):1514-1520.