基于TMS320C6416芯片的多板卡声纳信号协同处理技术

陈虹舟,朱思奇,霍家道

(1.中国船舶重工集团公司江苏自动化研究所,江苏 连云港 222006;2.上海交通大学,上海 200030)

声纳是利用声波对水下目标进行探测、定位、跟踪、识别的水声设备,是军事上和国民经济中一种重要的信息获取手段。数字信号处理器(Digital Signal Processor,DSP)是一种特别适合于进行数字信号处理的微处理器,广泛应用于各类声纳信号处理设备中。近年来,随着技术的发展和应用需求的提高,声纳信号处理系统的数据吞吐量和运算量显著增加,单个DSP的处理能力已不能满足系统的计算处理要求,迫切需要多个 DSP进行协同处理,以增强整体数据处理能力。TI公司高性能的数字信号处理器TMS320C6416是一种32位高速定点数字处理芯片,其工作时钟频率最高可达到1GHz,接口丰富,能够方便快速地与外围设备进行数据交换。本文提出了基于TMS320C6416芯片的多板卡声纳信号协同处理技术,它采用EDMA技术通过PCI接口实现多DSP板卡的数据交换,以实现对多路声纳信号的协同处理。

1 系统概述

声纳信号处理主要完成声纳模拟信号从采集、量化、滤波、计算处理、数据筛选到输出的全过程。不入路数可能大不相同。根据板卡取处理能力,当纳信号输入路数较少时,可采用单块板卡进行处理;当声纳信号输入路数较多时,占用的存储空间和数据处理的运算量都很大,则需要采用两块或多块板卡对声纳信号进行协同并行处理,以确保系统的处理性能。

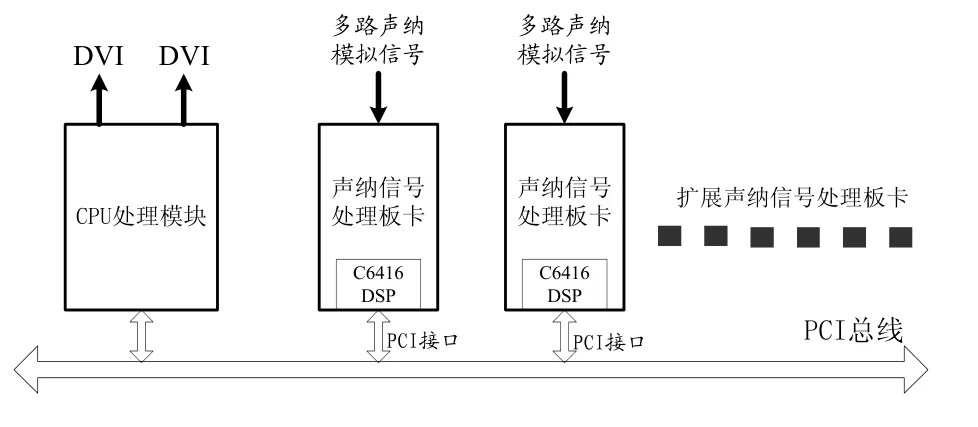

系统由计算机主处理器控制,并实现人机交互,信号处理由DSP完成。主处理器和各DSP分布在不同的板卡上,其互连方式如图1所示。计算机CPU处理模块和多块声纳信号处理板卡通过PCI总线实现互连,各处理板卡中的信号处理以及相邻两块处理板卡之间的信号相关处理采用软件控制,通过中断方式由PCI总线在相邻两块处理板卡之间传送相关数据。各声纳信号处理板卡分别处理各自接收的声纳回波信号,采集量化后进行处理,处理结果通过PCI总线传送给计算机CPU处理模块,组合后显示输出。

图1 多板卡的互连方式

2 多板卡协同处理技术

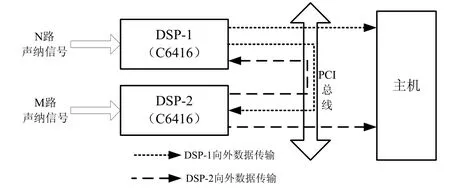

对于同时输入的多路声纳信号,要实现多板卡协同处理,首先要实现DSP与DSP之间、DSP与主机之间的数据传输,其次要保证多板卡之间的协调和同步。图2给出了两块声纳信号处理板卡协同处理多路声纳信号的示例,其中 DSP-1处理 N路声纳信号,DSP-2处理M路声纳信号。对于N+M路声纳信号而言,虽然在两个DSP上分别处理,但仍为一个整体,如同在单个DSP上处理一样。由于相邻声纳信号之间的相关性较强,在N路信号与M路信号之间有相关处理,因此DSP-1需要将部分声纳信号传输至DSP-2,反过来,DSP-2也需要将部分声纳信号传输至DSP-1。然后各DSP分别进行计算处理,并将处理后的数据传输至主机。主机在对两块DSP送来的数据进行同步处理后,显示输出。

图2 多DSP数据传输示意图

2.1 DSP与主机的数据传输

TMS320C6416芯片自带一个32bit/33MHz 3.3V主/从模式PCI接口,支持PCI接口规范2.2版本,通过PCI总线能够实现DSP与PCI主机的互连。该PCI接口支持下列四种类型的数据交换:

◆ 从模式写,外部PCI主设备通过PCI接口写数据到DSP从设备;

◆ 从模式读,外部PCI主设备通过PCI接口从DSP从设备中读数据;

◆ 主模式写,DSP主设备通过PCI接口写数据到外部PCI从设备;

◆ 主模式读,DSP主设备通过PCI接口从外部PCI从设备读数据。

DSP对声纳信号处理完后,需将处理后的数据传输至主机加以显示。此时可采用从模式读和主模式写两种方式完成DSP到主机的数据传输。由于对同样大小的一批数据,主模式写的速度比从模式读的速度快,且前者有利于数据的实时传输。因此采用DSP的主模式写方式来实现DSP与主机的数据传输,即DSP作为PCI主设备向主机的指定地址写入数据,并在写完数据后向主机发中断,提示主机读取数据。

在主模式写方式下,相关的控制器包括DSP主地址寄存器(DSPMA)、PCI主地址寄存器(PCIMA)以及PCI主模式控制寄存器(PCIMC)。其中,DSPMA中写入传输的源地址(即DSP地址),PCIMA中写入目的地址(即PCI主机地址)。启动主模式写后,由EDMA负责从源地址向DSP内部的写FIFO搬移所要求的数据,数据传输持续到 FIFO满或请求的数据长度传输完为止。一旦FIFO得到有效数据,PCI接口模块会向外发出PCI总线请求,并将FIFO中的数据向PCI从设备传输。当DSP源地址中所有的数据都送入主模式写FIFO后,DSP内部的数据传输结束。通过向RSTSRC寄存器中的INTREQ位和INTRST位写1即向PCI主机发出中断,完成一次数据传输。

2.2 DSP与DSP的数据传输

DSP与 DSP之间的数据传输是多板卡声纳信号协同处理的关键和难点,只有实现了DSP之间的数据传输,多板卡协同处理才成为可能。DSP之间的数据传输类似于DSP与主机之间的传输,不同之处在于传输的目的地址为DSP中的某地址。要实现DSP之间的数据传输(以图2中DSP-1向DSP-2传输数据为例),有以下两个难点:

1)DSP-1在主模式写方式下,PCIMA寄存器中只能写入PCI主机地址,不能直接写入目的DSP-2地址。因此要先将DSP-2的目的地址映射到主机上,转为PCI主机地址后方可写入PCIMA中。

2)PCI主机可访问的 DSP内存被映射在有限空间中,该有限空间远小于DSP的寻址空间,因此需通过 DSP页寄存器(DSPP)来确定映射的有限空间在DSP存储空间中的位置。在DSP-1向DSP-2传输数据时,DSP-1先根据目的地址求出页面值和该页面下的偏移地址,然后通过主模式写方式将页面值写入DSP-2的页寄存器中;最后通过主模式写方式将待传输的数据写入DSP-2在该页面下的偏移地址中。这样就完成了DSP-1到DSP-2的数据传输。

2.3 多板卡的同步处理

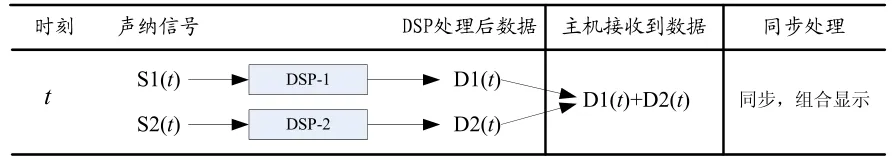

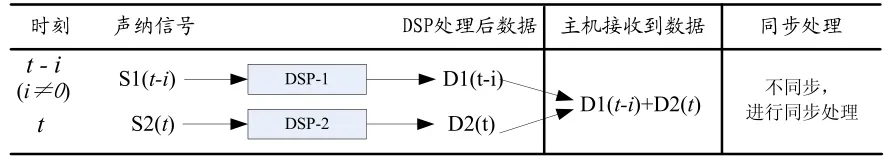

当同一信号源在某一时刻输出声纳信号后,多个DSP并行采集和处理。主机在收到多个DSP的数据中断后,需先判断收到的数据是否是同一时刻,即判断多个DSP处理是否同步。如表1所示,当主机收到两个DSP的同步数据,则直接进行组合显示;而表2所示,当主机接收到的数据不是同一时刻的声纳数据,则不同步,此时主机需要通过一些同步机制来处理,以保证后续处理的同步。

表1 多个DSP处理同步情况

表2 多个DSP处理不同步情况

3 实现与验证

3.1 系统实现

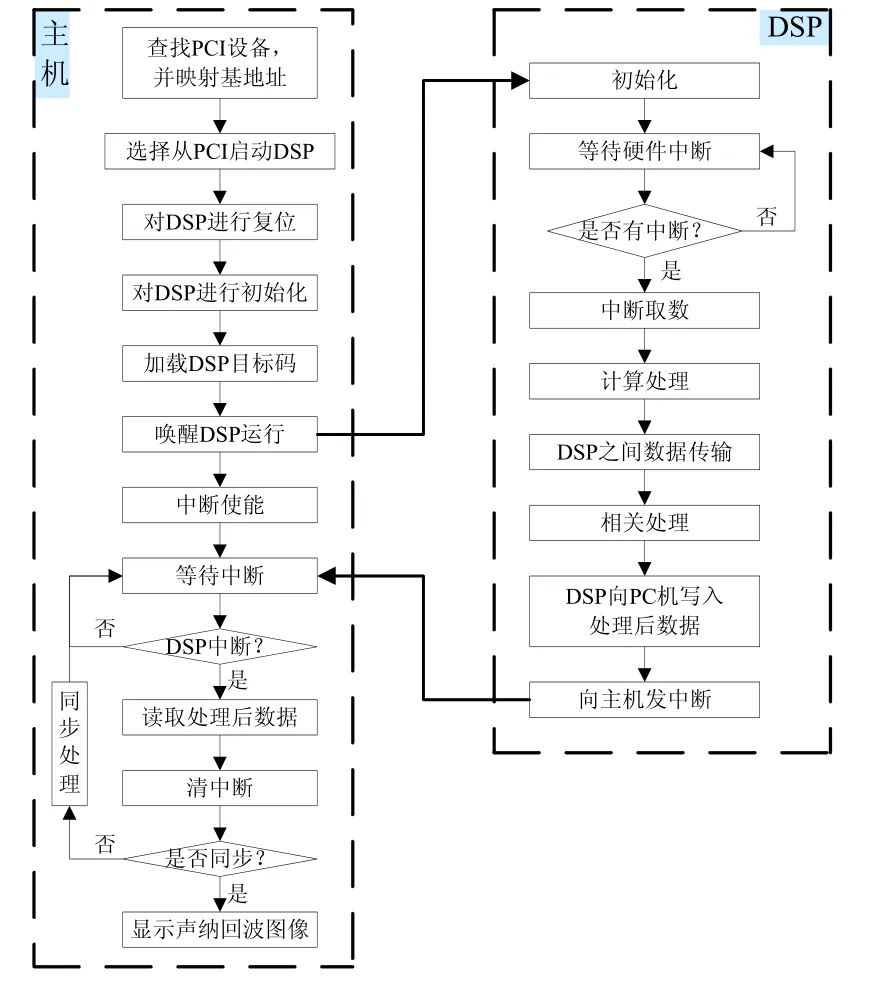

基于上述硬件结构以及协同处理思想,我们设计了基于TMS320C6416 DSP处理器的声纳信号处理板卡,其单板的声纳信号处理能力为20路,当待处理声纳信号超过20路时,可以对系统进行扩展,组成多板卡声纳信号协同处理系统。多板卡声纳信号协同处理系统的软件实现划分为两部分:声纳信号处理程序和计算机主控程序。

声纳信号处理程序运行于 TMS320C6416,采用CCStudio3.0集成开发环境,基于DSP/BIOS开发。为了便于系统扩展,在多板卡声纳信号协同处理过程中,每块板卡运行相同的程序,通过板卡在系统中的位置来确定其所处理的对应通道声纳信号及其与相邻板卡之间的数据交换内容。该程序的关键技术在于实现各处理板卡DSP之间的数据传输、DSP向主机的数据传输。

为了提高系统的实时性,计算机主控程序选用VxWorks操作系统,运行于计算机主处理器,在Tornado2.2环境下开发。主要实现DSP程序的加载、运行控制、DSP中断处理、同步处理及声纳回波图像的显示。

软件实现的程序流程如表3所示。

图3 软件程序流程

3.2 验证结果

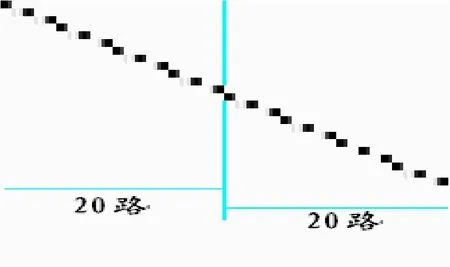

实验中,我们采用模拟的声纳信号源对所设计的多板卡声纳信号处理系统进行了验证。信号源能够提供40路信号,系统中采用2块声纳信号处理板卡,其中左20路在第一块板卡中处理,右20路在第二块板卡中处理。两板卡协同处理后,形成声纳视频图像,送CPU模块显示效果如表4所示。由显示效果看出,40路信号虽然分开在两块声纳信号处理板卡上处理,但协同处理后,实现了40路声纳信号的实时处理和无缝组合显示,达到了预期效果。

图4 多板卡协同处理技术的实现效果图

4 结束语

本文主要介绍了基于 TMS320C6416的多板卡声纳信号协同处理技术,重点介绍了多板卡之间的数据传输原理及实现方式。该技术在提高系统处理能力的同时,能有效提高系统设计的灵活性和可扩展性。DSP之间以及DSP与主机之间的数据传输方法,为多板卡信号处理系统提供了软件实现的借鉴方法,有利于开展多板卡协同处理工作。

[1]Texas Instruments.TMS320C6000 Peripherals Reference Guide.2001.

[2]汪安民,等.TMS320C6000 DSP实用技术与开发案例[M].北京:人民邮电出版社,2008.

[3]何慧颖,胡越明,蒋嫣枫.基于DSP的PCI总线数据传输的实现[J].计算机工程,2004,30(增刊):497-498.

[4]赵贵海,张宝峰,季秀远.基于DM642的PCI总线接口技术的高速数据传输研究[J].天津理工大学学报,2008,24(2):76-79.