扩频通信芯片STEL-2000A的FPGA实现

谭 强,万 毅

(兰州大学 信息科学与工程学院,甘肃 兰州 730000)

扩频通信因其很好的保密性、隐蔽性、抗干扰性以及抗多径效应等优势得到了快速发展和广泛应用。因此,许多公司推出了各种型号的扩频集成电路,典型的有STEL-2000A,该芯片因外围电路简单而得到了广泛应用[1]。

然而,由于该芯片是基于专用集成电路(ASIC)技术,其内部电路和大部分功能已经固化,对不同的场合缺乏灵活性,对以后系统升级也造成很大困难。而现场可编程门阵列(FPGA)内部资源丰富,功能强大,并且可重复编程,现场可修改设计,加之其相应的EDA软件功能完善,仿真能力好,有丰富的IP核资源,在成本和灵活性等方面都有很大优势,使得利用FPGA进行复杂数字系统的设计已成为主流[2]。

近几年来国内外有许多学者利用FPGA对扩频通信系统中的某一个模块进行设计,如:数控振荡器[3]、PN码发生器[4]、匹配滤波器[5]。也有学者尝试对整个系统进行设计[6],但这些努力大多仅限于软件上的功能仿真,并且对一些关键模块缺乏清晰的描述。

本文对扩频芯片关键模块的实现方法进行了阐述,并推导出详细参数,基于ISE 10.1实现了整个系统,最后下载到FPGA芯片中调试成功。

1 STEL-2000A系统的整体框架

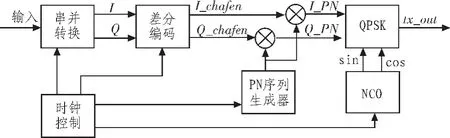

1.1 发射子系统

在发射子系统中,如图1所示,输入的串行二进制数据序列首先进行串并转换,分成两路(I路和Q路)速率减半的序列,由于采用QPSK调制方式,为了避免相位模糊问题,在串并转换后进行差分编码,然后将差分编码器的输出序列与PN码生成器输出的伪随机序列进行异或运算,完成信号的频谱扩展,再将扩频输出的两路数据分别与数控振荡器(Numerically Controlled Oscillator,NCO)的两路正交载波输出各自相乘,最后将相乘后的结果相加,这样就实现了DQPSK调制,输出的是数字化的已调信号[7]。

图1 发射子系统图Fig.1 Structure diagram of transmitting subsystem

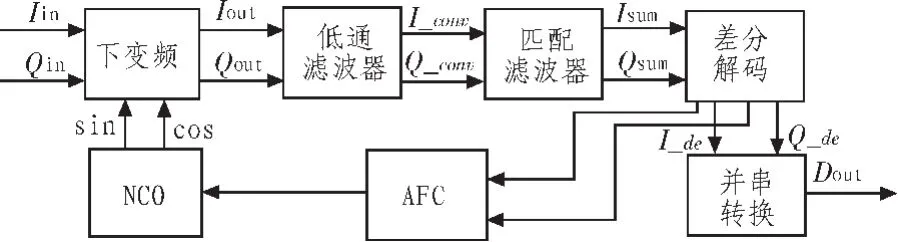

1.2 接收子系统

接收系统要完成数字中频信号到基带信号的转换、信号的捕获、同步、解扩、差分解调以及并串转换等功能,如图2所示。进入接收系统的是经正交采样(Quadrature Samping)后的数字中频信号,经下变频器生成基带信号,再将其输出送入匹配滤波器。在匹配滤波器中,主要实现信号的同步与解扩。解扩后的数据进行差分解调,差分解调过程中的中间结果送入自动频率控制 (Automatic Frequency Control,AFC)模块以生成校正信号来自动调整NCO的输出频率,最后将解调输出数据经并串转换便得到原始数据序列[7]。

图2 接收子系统图Fig.2 Structure diagram of receiving subsystem

2 关键模块分析与实现

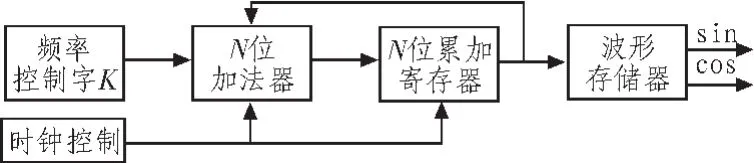

2.1 NCO模块

NCO采用Xilinx公司提供的直接数字式频率合成器(Direct Digital Synthesizer,DDS)IP 核,DDS 的工作原理如图3所示,在参考时钟的驱动下,N位加法器对频率控制字K和N位累加寄存器中的值进行相加,相加后的结果存入累加寄存器中,以累加寄存器中的值为地址将波形存储器里相应地址的数据读出,即输出正弦或余弦信号的幅度值[8]。

图3 NCO原理结构图Fig.3 Principle diagram of NCO

累加寄存器长度为N,则波形存储器2N用个样点来表示正弦波的一个周期,地址每次累加K相当于每隔K个点输出一次,输出一个完整的正弦波需要时间则DDS的输出频率fout满足关系式[8]:fout=KfCLK/2N。当K取1时输出频率为最大频率分辨率Δf=fclk/2N。参数设置主时钟为100 MHz,Δf=1.0 Hz,可得N=27,由于要求的输出频率为 2 MHz,可得:K=2684355。据此对DDS IP核进行元件例化程序如下:component dds

port(

DATA:IN std_logic_VECTOR(26 downto 0);

WE:IN std_logic;

A:IN std_logic_VECTOR(4 downto 0);

CLK:IN std_logic;

SINE:OUT std_logic_VECTOR(6 downto 0);

COSINE:OUT std_logic_VECTOR(6 downto 0));end component;

2.2 下变频模块

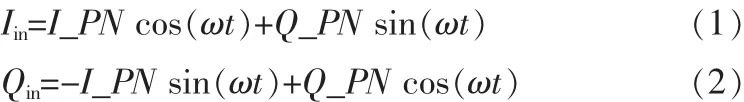

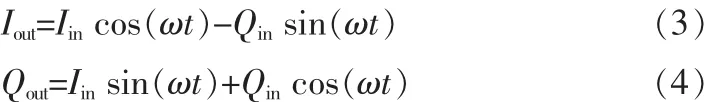

下变频模块主要是将输入的数字中频信号进行数字式下变频,从而产生基带信号,即待解扩的信号。设输入信号是经正交采样后的数字中频信号:

式中,I_PN和Q_PN为扩频后的信号,ω为本地NCO产生的正弦和余弦信号的角频率。

让输入信号与本地NCO产生的正弦与余弦信号进行相乘,即:

这里需要4个乘法器和2个加法器,由于对乘法器的速度要求较高,本系统调用了Virtex-II Pro开发板上FPGA芯片XC2VP30的硬核乘法器[9]。将Iout和Qout进行低通滤波就得到基带信号。

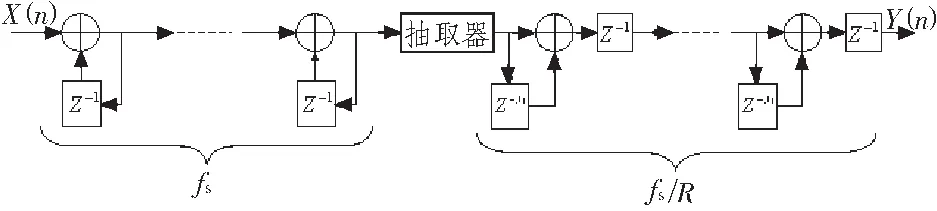

对于低通滤波器的实现,STEL-2000A使用了积分清洗滤波器(Integrate and Dump Filter,I&D)。本系统采用比较成熟且实现方便的级联积分梳状(CIC)滤波器[10]来实现低通滤波的功能。该滤波器由加法器、反相器和延时器构成,不需要乘法器,这比一般的FIR和IIR节省很多FPGA资源。实现框图如图4所示,fS为采样频率。

图4 CIC滤波器的实现框图Fig.4 Implementation diagram of CIC filter

系统中CIC滤波器参数的设置为:M=1,N=4,R=20。为了保证运算不发生溢出,可以根据公式:BMAX=Nlog2RM+B-1[10],计算出内部需要的最大信号线宽度。在本系统中输入信号线宽度B=3,则取BMAX=20。为减少后端匹配滤波器的运算量,取CIC滤波器输出的高三位近似。

CIC滤波器部分设计程序如下:

sxtx〈=sxt(x,20);--位扩展。

integrater:process(clk)

begin

if(clk'event and clk='1')then

x〈=x_in;

i0〈=i0+conv_integer(sxtx);

i1〈=i1+i0;

i2〈=i2+i1;

i3〈=i3+i2;--第4级积分器输出

end if;

end process integrater;

comb_clk:process(clk) --实现 20 分频

end process comb_clk;

comber:process(clk_comb)is

begin

if(clk_comb'event and clk_comb='1')then

i3_delay〈=i3;

C0〈=i3-i3_delay;

......

C3〈=C2-C2_delay;--第4级梳状滤波输出

end if;

end process comber;

C_out〈=conv_std_logic_vector(C3,20);

y_out〈=C_out(19 downto 17);--取高 3 位作为最后结果

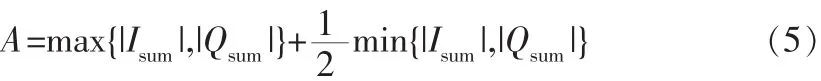

2.3 匹配滤波器模块

匹配滤波器实现信号的同步与解扩,CIC滤波器的输出I_conv、Q_conv分别经过两组延时器,然后与本地PN码序列相乘,将所有相乘的结果相加。理论上讲下变频送来的基带扩频信号经匹配滤波器后在给定的观测时刻相关峰值[6]为:Isum=AcosφK(t),Qsum=AsinφK(t),φK(t)为在给定观测 t时刻第 k个符号的载波相位。

得到相关峰幅值后,与一个预设好的门限值进行比较,当峰值大于门限值时,表示发送的序列与PN码寄存器里的伪随机序列对齐,此时输出一个定位脉冲sybmol,其实现框图如图5所示。

图5 匹配滤波器的实现框图Fig.5 Implementation diagram of matched filter

匹配滤波器部分设计程序如下:

process(clk_chip,I,Q,)is

begin

if(clk_chip'event and clk_chip='1')then ext_I(63)〈=Iin;

ext_Q(63)〈=Qin;

for i in 0 to 62 loop

ext_I(i)〈=ext_I(i+1);

ext_Q(i)〈=ext_Q(i+1);

end loop;

for j in 0 to 63 loop

Idat(j)〈=pn(j)*conv_integer(ext_I(j));

Qdat(j)〈=pn(j)*conv_integer(ext_Q(j));

end loop;

Isum〈=Idat(0)+Idat(1)+...+Idat(63);

Qsum〈=Qdat(0)+Qdat(1)+...+Qdat(63);

end if;

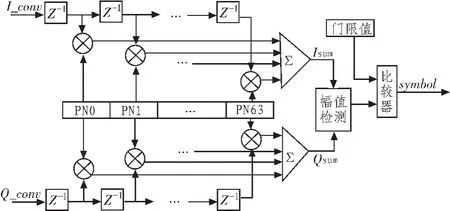

2.4 差分解调模块

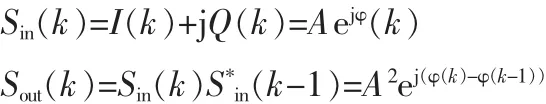

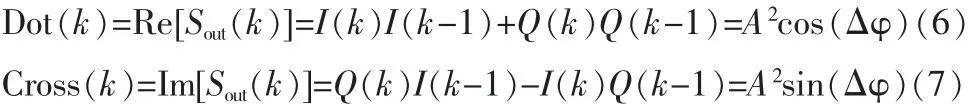

当检测到定位脉冲时(即检测到相关峰最大幅值),将此时Isum和Qsum的值送入寄存器以供差分解调使用。对于DQPSK的解调,关键是判断第k位和第k-1位符号之间的相位差Δφ,STEL-2000A中引入点积Dot和叉积Cross来判断Δφ。

信号经匹配滤波器后,基带信号可为:I(k)=Acosφ(k),Q(k)=Asinφ(k)。 φ(k)为第 k 个符号的载波相位。

令:

定义[7]:

由于本系统采用DQPSK调制方式,所以Δφ的取值有0,π/2,π 和 3π/2 四种,sin(Δφ)和 cos(Δφ)的取值有 0,+1,-1 三种,在进行最佳判决接收时相对较难实现。本系统引入了π/4的固定相移。给出简单的推导如下:

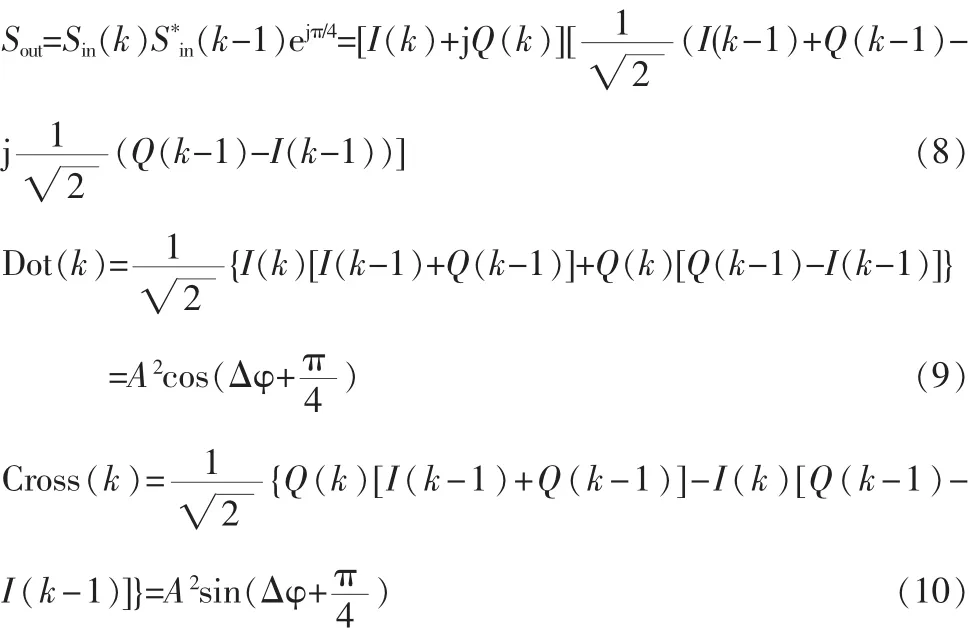

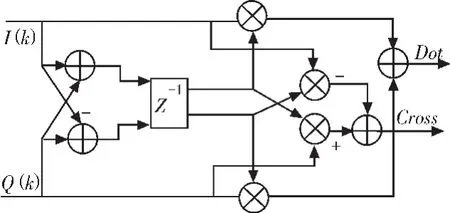

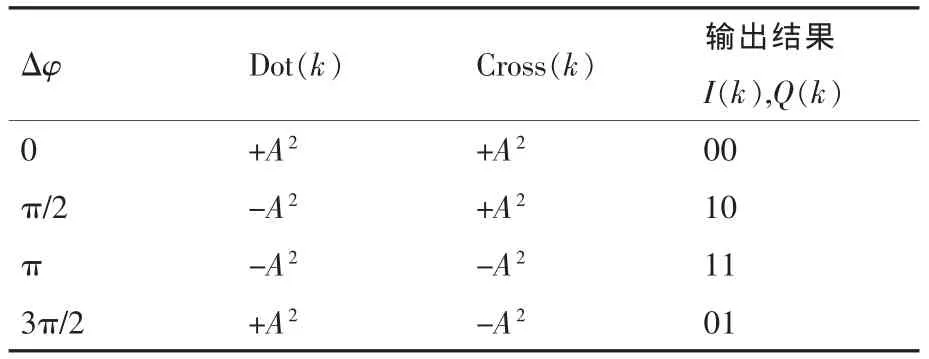

从式(9)、式(10)可以发现只需要在延时之前对两路信号进行简单的算术组合即可得到π/4的固定相移,差分解调器实现框图如图 6所示。输出的 Dot(k)和 Cross(k)值查表 1,即可得到最后的差分解调结果。

图6 差分解调实现框图Fig.6 Implementation diagram of differential demodulation

表1 输出结果判决表Tab.1 Decision table of output

3 测试结果

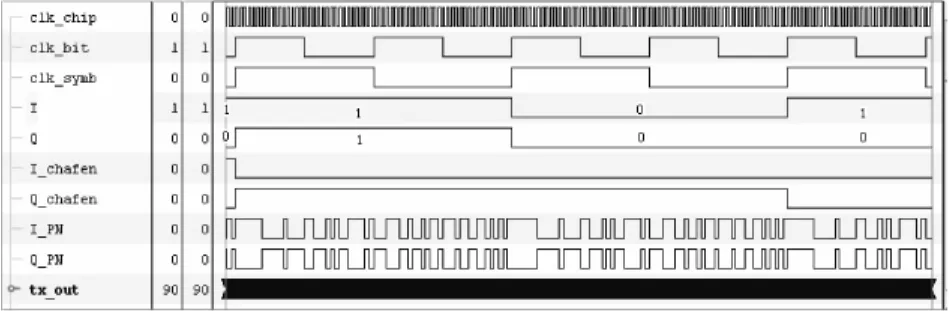

测试系统为FPGA产生输入信号“01011001”的周期循环序列,输入信号经过发射模块后的数字信号输出直接进入接收模块,输入信号产生模块、发射模块和接收模块都在同一块FPGA芯片内。系统的参数设置为:主时钟为100 MHz,数据最大速率为31.25 Kb/s,工作时钟为31.25 kHz,PN码长为64位,速率为1 Mchip/s,NCO的工作时钟为100 MHz,输出的数字正弦和余弦信号频率为2 MHz。

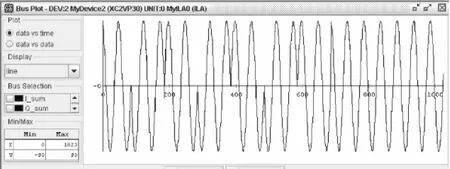

通过在线分析仪ChipScope Pro[2],可以看到经QPSK调制后待输出的信号(图 7,8),其中图 7的 I和 Q是串并转换后的信号,此时的输入信号为 “10110010”,I_chafen和Q_chafen是差分编码后的信号,I_PN和Q_PN信号是经过扩频后的信号,tx_out是最后的已调信号。将已调信号绘制成曲线如图8所示。

图7 扩频后的信号Fig.7 Spread spectrum signal

图8 待发送的QPSK已调信号Fig.8 QPSK modulated signal to be sent

在接收部分,利用ChipScope Pro可以观察到下变频器的输出信号I_conv和Q_conv,匹配滤波器的输出信号Isum、和Qsum定位脉冲symbol(图9),I_de和Q_de为差分解调后的信号,图中显示此时的解调结果为“00101011”,相对于输入信号而言只是有一段时延,从而验证该系统实现了STEL-2000A的核心功能。

图9 接收系统中的部分信号Fig.9 Part af signal in receive system

4 结 论

通过对扩频芯片STEL-2000A的功能研究,详细分析了其关键模块的基本原理。在此基础上,利用FPGA实现了整个系统的功能,并对其进行了测试。测试结果表明该系统功能的正确性。另外,由于FPGA的灵活性,系统可以根据不同场合改变其中的参数,比如改变PN码的长度、改变CIC滤波器的级数和抽取系数、调整匹配滤波器的门限值等以适应其在不同应用场合的需要。

[1] 韦惠民.扩频通信技术及应用[M].西安:西安电子科技大学出版社,2007.

[2] 田耘,徐文波,胡彬.Xilinx ISE Design Suite 10.X FPGA 开发指南:逻辑设计篇[M].北京:人民邮电出版社,2008.

[3] Mran H,Sharaf K,Ibrahim M.An all-digital direct digital synthesizer fully implemented on FPGA[J].Design and Test Workshop (IDT),20094th International,2009:1-6.

[4] ZHANG Wei,LI Yong-qian,SONG Wen-miao,et al.FPGA implementation of PN code acquisition Based on software radio[C]//WiCOM'08.4th International Conference on Wireless Communications,Networking and Mobile Computing,2008:1-4.

[5] WANG Yu-xi,SHEN Ye-bing.Optimized FPGA realization of digital matched filter in spread spectrum communication systems[C]//IEEE 8th International Conference on Computer and Information Technology Workshops,2008:173-176.

[6] 陆涛.基于FPGA实现的扩频通信系统[D].成都:西南交通大学,2003.

[7] Intel Integrated Products.STEL-2000A Data Sheet[EB/OL].(1999-11-15)[2010-04-29].http://www.semiconductorsdevices.com/news/search.php?tWord=STEL-2000A.

[8] Xilinx Inc.DDS V5.0 data sheet[EB/OL].(2005-04-29)[2010-04-29].http://xilinx.com/support.

[9] Xilinx Inc.Multip V10.0 data sheet[EB/OL]. (2007-04-02)[2010-04-29].http://xilinx.com/support.

[10] 盖鹏翱,赵笛.CIC滤波器的原理及FPGA实现[J].无线通信技术,2005,14(4):52-55.GAI Peng-ao,ZHAO Di.The realization of cascaded integrator comb filter with FPGA[J].Wireless Communication Technology,2005,14 (4):52-55.