DDS的触发抖动引起IQ相位突跳的研究

(海军装备部驻上海地区军事代表局,上海 200083)

0 引言

随着雷达技术的发展,线性调频信号已经广泛应用于高分辨率雷达领域。直接数字频率合成(Direct Digital Synthesizer,DDS)是现代雷达特别是合成孔径雷达(Synthetic Aperture Radar,SAR)获得线性调频信号的主要方法[1-2]。DDS技术的优点在于相对带宽宽、转换时间短、频率分辨率高、输出相位可连续等方面。而随着DDS系统时钟的不断提高,DDS 触发信号的微小抖动都会导致发射信号的相位突跳,它破坏了相参雷达的相参性,相当于对发射信号添加了一种随机的二相调制,导致接收的IQ 解调信号相位突跳,影响雷达动目标的检测和SAR成像[3-4]。本文将对此问题作深入的分析,并给出相应的解决方法。

1 DDS技术和雷达基带信号产生的基本原理

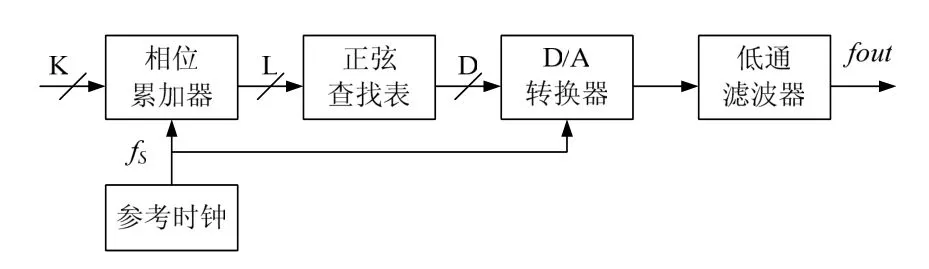

直接数字频率合成(DDS)的基本原理是利用采样定理,通过查表法产生波形。DDS 主要由相位累加器、正弦查询表、D/A转换器、低通滤波器和参考时钟5个部分组成,如图1所示。

图1 DDS 原理框图

相位累加器在每一个时钟沿与频率控制字K 累加一次,当累加器大于2N时,相位累加器相当于做一次求模取余运算。正弦查找表ROM 在每一个时钟周期内,根据送给ROM的地址取出ROM 中已存储的相对应的正弦幅值(二进制码);然后将该数值送给D/A转换器变换为模拟量;最后经过低通滤波器滤去高频分量,得到较纯净的正弦波。目前,DDS的实现方法有两种:一种利用专用的DDS 芯片来实现,典型的DDS 集成芯片如美国AD 公司生产的AD985x系列产品,参考时钟从几十MHz 到1 GHz;一种利用通用的FPGA 器件进行专门设计[5]。在雷达设备中通常采用第一种方法。

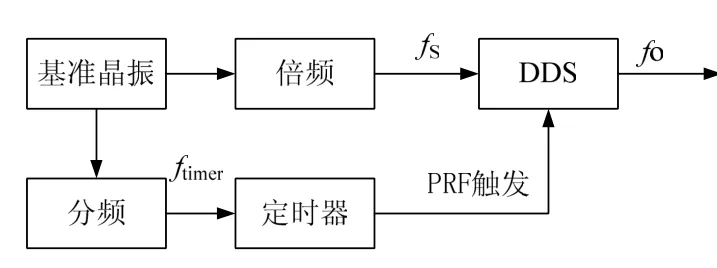

应用DDS技术来产生雷达基带信号的原理如图2所示。

图2 雷达基带信号产生原理

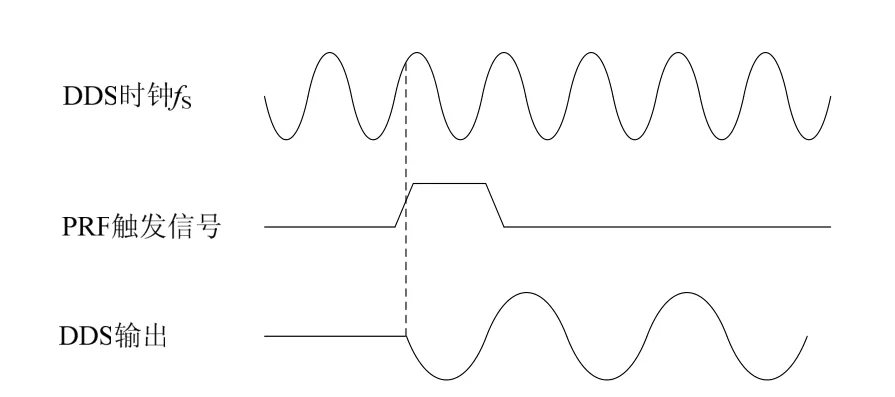

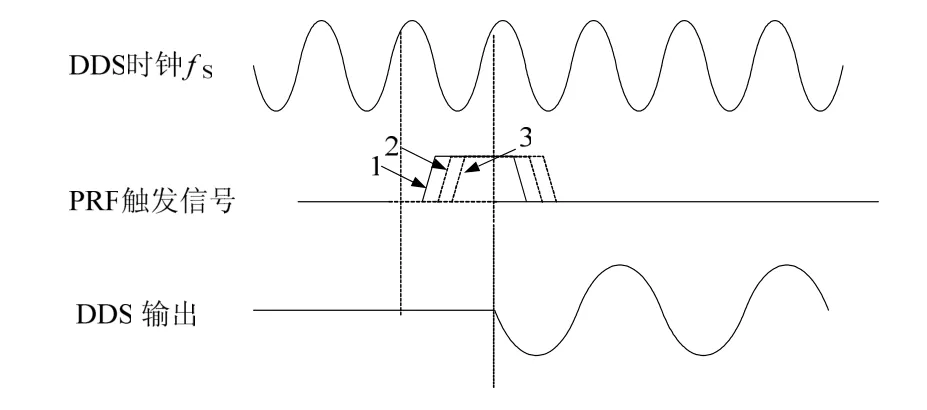

由图2可以看出,雷达的相参基准源是一高稳定度的晶振,它的一路输出倍频后作DDS的系统时钟fS;一路输出分频后送定时器作基准时钟ftimer,由定时器输出PRF 触发信号去触发DDS 电路产生相应的雷达波形。DDS 工作的时序如图3所示,图3中,在触发之后可以立即输出波形。实际上,大多数DDS 器件在触发信号和输出之间存在一定的延迟[5-6]。但是这个延迟时间是固定的,因此这里不予考虑。

图3 DDS 工作时序图

如果DDS的系统时钟fS和定时器的基准时钟ftimer是整数倍的关系,则因为是来自同一个基准源,所以fS的上升沿和PRF 触发脉冲的前沿通常是对齐的。

2 PRF 触发信号抖动引起DDS 输出的相位突跳

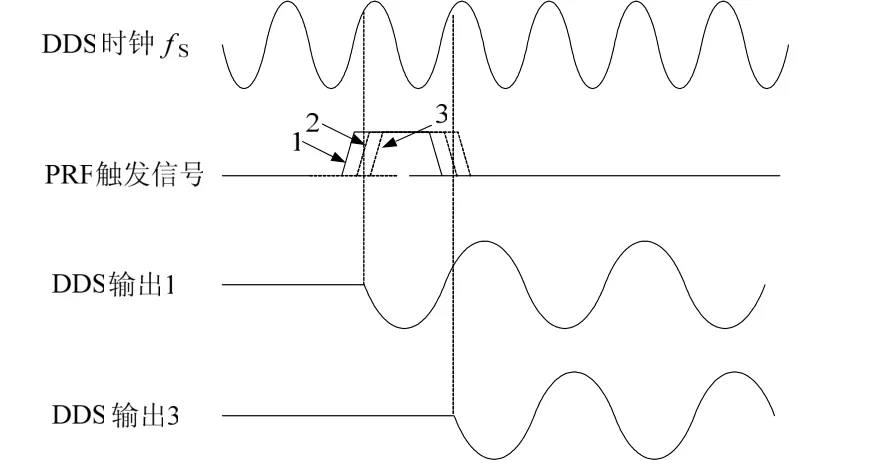

在实际电路中,PRF 触发信号在分频整形和长线传输后前沿的抖动是难以避免的,即使这种抖动较小,但只要满足特定条件,也会引起DDS 输出信号的相位突跳,如图4所示。

图4 PRF 触发信号抖动引起两个DDS 输出

DDS 芯片在每个系统时钟读取触发信号的状态,当判断触发信号出现上升沿后,在DDS系统时钟的下一个上升沿开始按照新装订的参数产生输出信号。如图4所示,当PRF 触发信号的上升沿超前DDS系统时钟fS的上升沿一定时间时,输出波形为DDS 输出1,当PRF 触发信号的上升沿落后DDS系统时钟fS的上升沿一定时间时,输出波形为DDS输出3。由于抖动的影响,PRF信号的上升沿在1和3 之间随机变化,因而DDS的输出波形也在随机跳变。

对于DDS 输出为点频的情况,DDS 输出1 和DDS 输出3 之间的相位突跳∆θ可以由公式求出:

∆θ=2πfO/fS。

根据奈奎斯特定理,DDS的输出频率不会超过1/2系统时钟,故DDS的触发抖动造成的相位突跳小于180°。

随着DDS的系统时钟频率不断提高,触发脉冲抖动的影响越来越大。目前集成的DDS 芯片的工作时钟已经到了1 GHz 以上,这种现象出现的几率大大增加。

在雷达系统中,DDS 输出的基带信号,经过上变频、倍频等中间过程后,变换到发射信号,再经发射机放大后通过天线辐射出去,基带信号的相位突跳必然带来发射信号的相位突跳;回波信号送到接收机,因为发射和接收为同一个基准参考源,所以接收是相参的,回波信号经过下变频和IQ 解调后的视频信号的相位也是突跳的。

这种现象对发射信号添加了一种随机的二相调制,这样就破坏了相参雷达严格的相参性要求,并且会对雷达的相参积累和目标检测产生影响[4]。不仅如此,这种现象还使得来自同一个目标的雷达回波相对于PRF的延迟时间出现抖动,从而会影响对目标距离的精确测量。雷达的距离分辨率和测量精度越高,这种抖动的影响越大。因此,对于距离分辨率很高的SAR 而言,解决好抖动问题,关系重大。

3 相位突跳的实验研究

通过上面的讨论,基本清楚了DDS的触发信号的抖动是如何导致基带信号的相位突跳,并最终引起接收的IQ 检波信号的相位突跳的。然而实际工作中,IQ信号出现相位突跳呈现无规律性。为了进一步证实就是DDS 触发信号的抖动造成的IQ相位突跳,必须结合上述理论分析进行实验验证。

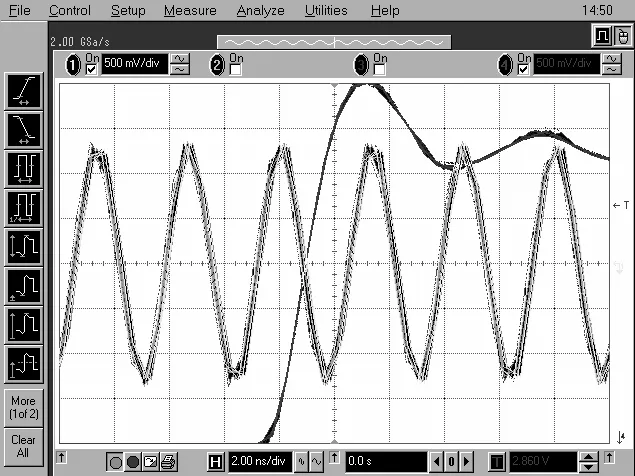

在实验中,用示波器监测触发脉冲、DDS时钟、IQ 输出,通过调整触发脉冲的输出延时,使得脉冲前沿的抖动处于或者不处于DDS时钟信号的上升沿,如图5和图6所示。正如前面所分析的那样,IQ 输出相位突跳有时频繁出现,有时完全消失。

图5 有IQ相位突跳时

通过上述实验基本肯定了:IQ相位的突跳正是由于DDS 触发脉冲的抖动与DDS时钟时序引起的。

上述实验也提供了解决问题的线索。由图5和图6显然可以看出,DDS 触发脉冲的前沿抖动相对于DDS时钟周期是很小的,只要将DDS 触发脉冲和DDS时钟的相对延时作合适的调整就可以了,延时哪一个信号都是可行的。为此选择将定时器送来的DDS 触发脉冲在进入DDS 芯片之前作适当的延时。

但是,实际操作中存在以下问题:即实际的DDS 触发脉冲和DDS时钟的相对延时关系和用电缆、探头测试时在示波器上显示的并不一致,尤其在DDS时钟频率很高的时候会相对偏差更大。从上面所做实验中保存下来的两幅图就很明显的看出,示波器显示的似乎和理论分析的情况刚好相反。这当然只是一种巧合,因此要避开这个问题。

继续上面的实验:通过调整脉冲延时,找到相位抖动最严重的时序图后,以它为参考,在同样的条件下(即使用同样的电缆和探头,监测同样的测试点),触发脉冲更换为定时器提供,将其前沿调整到时序图中的相对位置再延时1/2个DDS时钟周期。(要注意的是:示波器上显示的时序关系可能和实际的刚好相反,如图5和图6所示,这也是找参考时序图的原因)。

经过调整DDS 触发脉冲的延时后,分机在多次实验都未出现IQ相位突跳的问题。

4 实验结果分析

实验结果表明,如果PRF 触发信号与DDS时钟的时序关系不合适,则会引起发射的LFM信号和接收机输出的IQ信号的相位突跳。而通过调整PRF 触发信号相对于DDS系统时钟的延迟,完全可以避免此现象的出现。

理论上,使PRF 触发脉冲的上升沿处于DDS系统时钟两个相邻上升沿的中间位置(相位相差180°),允许的PRF 抖动范围最大,如图7所示。在这种情况下,只要PRF 抖动小于1/2个DDS系统时钟,就完全可避免相位突跳的产生,得到稳定的输出信号。这也意味着,在电路设计上,必须避免PRF 脉冲由于阻抗匹配不好而失真过大,并且尽量减少叠加在PRF 和DDS时钟信号上的随机噪声。

图7 PRF 触发信号与DDS时钟的最佳相位关系

首先,这种正确的时序关系需要依靠DDS 控制电路的设计来解决;其次,在DDS时钟频率高达GHz级下,PCB 走线的长度影响很大,因此对PCB设计也提出越来越高的要求;另外,系统装配、连线的离散性、芯片延迟时间的不确定性、噪声和工作温度都可能影响触发信号上升沿的波形和延迟时间,从而对时序关系产生影响。这些不确定性因素不能仅依靠设计解决,而必须通过试验来精确测量。

进行试验测量时,线缆的长度、测量点位置的选择都会引起信号的延迟。因此,示波器上显示的信号相位关系可能与DDS 芯片内部的信号相位关系不同有关。首先,找到相位跳变最严重时的延迟时间T0,这相当于图4中的相位关系;然后,调整PRF 脉冲的延迟时间与T0相差1/2个DDS系统时钟周期,超前或落后均可,得到相当于图7的相位关系,从而有效地避免PRF 脉冲前沿抖动的影响。

5 结论

随着DDS系统时钟频率的不断提高,如果DDS触发信号的抖动超出了DDS 工作时钟的上升沿,就可能出现发射信号在脉冲之间存在相位突跳,最终导致接收的IQ相位突跳。解决的办法是将DDS系统时钟信号或者触发脉冲做适当的延时,使得触发脉冲信号的前沿落在DDS系统时钟的两个上升沿中间,只要保证触发脉冲前沿的抖动不超过DDS系统时钟的一个周期,就可以避免突跳。因为DDS触发脉冲和DDS时钟的传输延时受到多种因素的影响,无法准确预测,所以在具体的电路设计中,可以在这两个信号的通路上预先加入延时电路,以便在生产阶段将时序调整到最稳定的状态;另外,在满足设计要求的情况下应该尽量降低DDS时钟的工作频率。

[1]MERRILL I SKOLNIK.雷达系统导论[M].3 版.北京:电子工业出版社,2006:549-562.

[2]WU Y,LI J.The design of digital radar receives[J].Proc.IEEE National Radar Conf.1997,34(2):207-210.

[3]DAVIDSON W,WONG F H,CUMMING I G.The effect of pulse phase errors on the chirp scaling SAR processing algorithm[J].IEEE Trans.on Geosciences and Remote Sensing,1996,34(2):471-478.

[4]周健.雷达频率源中DDS的触发抖动对目标检测的影响[J].电子工程师,2004,30(4):4-6.

[5]张冬梅,杨建宇,熊金涛.基于FPGA 实现DDS技术的雷达波形产生器的设计[J].现代电子技术,2005,195(4):103-105.