PM-OLED屏视频显示系统设计*

蔡 俊 ,冉 峰 ,陈章进

(1.安徽理工大学 电气与信息工程系,安徽 淮南 232001;2.上海大学 微电子研究与开发中心,上海 200072)

1 引言

有机发光二极管(OLED)显示器自1987年被首次报道以来,因其具有薄而轻、高对比度、快速响应、宽视角、高亮度、全彩色、坚固等优点,在光电子技术的重要领域,受到了显示产业界的重视,也是近几年来新材料及显示技术领域研究开发的一大热点。作为新一代显示器件,OLED在手机、个人电子助理、数码相机、车载显示、笔记本电脑、壁挂电视以及军事领域都具有广阔的应用前景[1-4]。

OLED器件根据其驱动方式的不同分为无源驱动(PM-OLED)和有源驱动(AM-OLED)两种。PM-OLED 器件已经进入实用化阶段。AM-OLED显示屏在每个像素的衬底上集成了多个薄膜晶体管(TFT),所以也叫TFTOLED[5-7]。

针对小尺寸OLED屏中的视频应用,笔者介绍了一种视频显示系统的设计。系统基于现场可编程逻辑器件(FPGA),使用硬件描述语言设计了显示控制电路。它从DVI接口获取动态视频图像,经过图像尺寸的变换,输出驱动OLED显示模块完成视频显示。在设计中,采用了列缩放与行缩放分开处理的结构,使用双口RAM作为两次缩放间的数据缓冲区,占用较少的硬件资源[4-5]。

2 系统结构

所设计的小尺寸OLED屏的视频显示系统结构如图1所示,由以下模块构成:DVI信号解码模块,OLED驱动显示模块,FPGA视频处理模块和数据存储模块。其中数据接收模块由DVI接口、SiI1161 DVI数据接收芯片、E2PROM和MCU组成,主要完成图像缩放前的准备工作。系统的视频输入信号经过DVI接收器芯片SiI1161的解码,将其转换成三通道24位RGB数字视频信号和行、场同步信号。

DVI接口输入的图像分辨力为640×480,帧速为60 f/s(帧/秒),其时钟频率为25.175 MHz。为了在小尺寸OLED屏上显示完整的内容,必须把640×480的图像转换为OLED所需的160×128像素点的图像。在设计中,使用二次缩放的结构对输入视频图像的行列信息分别进行显示尺寸的变换。

显示系统的核心控制部分由FPGA及SRAM构成,完成图像数据的接收,并且对数据进行实时存储、缩小、格式转换等处理。系统采用了低成本、高集成度的Cyclone系列现场可编程逻辑器件,完成视频数据处理的多种任务,提高了系统的集成度和灵活性。

3 模块电路设计

3.1 图像缩放处理

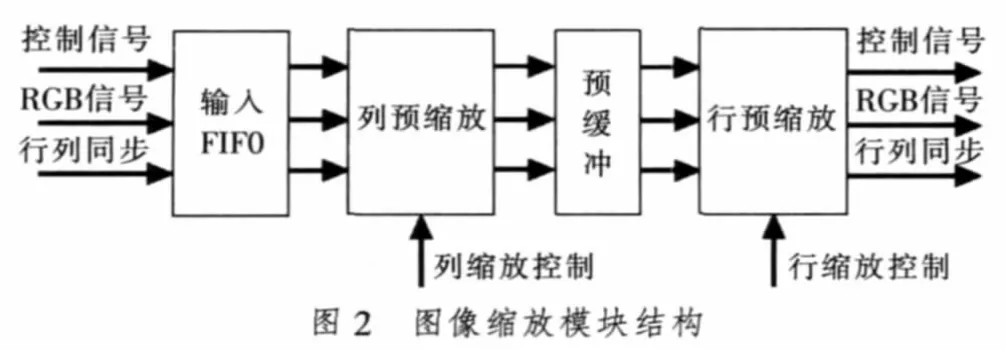

本设计选用二次缩放的结构进行缩放内核的设计(见图2),即“输入缓冲-列预缩放-预缓存-行缩放”的结构。列预缩放模块对输入的像素数据做水平方向的缩放。输入图像信号经过该模块后,垂直有效区域不变,水平有效区域变为所要求显示的宽度。

列缩放模块从先入先出缓存器(FIFO)模块中串行接收24位RGB信号,并将其存放于计算缓冲区中;列预缩放模块调用计算公式和缩放参数对图像信号进行缩放,并将结果写入预缓存模块;预缓存模块通过串并转换将串行RGB信号转换成为并行的RGB信号,输出送到行缩放模块。行缩放模块对输入的图像数据做垂直方向的缩放。图像经过该模块后,水平有效区域不变,垂直有效区域变为需要显示的高度。行缩放的结果被送入显示输出控制模块。

3.2 FIFO缓冲存储器设计

缓冲存储器用来存储缩放前后的图像数据信息,在设计中使用了一个异步FIFO和两个双端口RAM作为缓冲存储。其中,异步FIFO作为图像信息输入缓冲模块,两个RAM分别用于列预缩放缓冲模块和输出缓冲模块。

输入FIFO缓冲模块接收来自DVI接收模块的图像数据信号。电路工作时,一方面将RGB信号与行列位置等信息写入FIFO,另一方面则预先读出FIFO中早先存储的数据,送到图像缩放模块进行处理。

由于FIFO缓冲模块的读写时钟不同,因此设计了一个异步双口FIFO作为数据缓冲器,它的宽度为52 bit,深度为512 word(字)。为了保证异步FIFO不出现上溢或下溢现象,必须控制图像缩放模块读取有效像素的速度。因此,在本设计中设置了一个FIFO读命令rdreqEna,当列预缩放模块处于列循环阶段时,rdreqEna置1,若FIFO不为空,此时列预缩放模块从FIFO中读取图像数据信号。

异步双口FIFO缓冲模块由Verilog硬件描述语言设计实现,当数据有效信号为有效时,列预缩放模块才会读取FIFO中的数据,scaler缩放计算所使用的数据为一帧视频图像信号中的有效像素数据。

3.3 预缓存模块设计

列预缩放模块的输出是一行行水平方向上的有效像素数据,而根据缩放比例的不同,时域上行与行间可能存在间断。而垂直缩放需要相邻行中同列的数据作为输入来进行插值运算。为了进行垂直方向上的缩放运算,列预缩放模块的输出必须进行暂存。预缓冲存储器就是用来缓存列预缩放模块的输出,供行缩放模块进行垂直方向上的缩放处理。图3为预缓存模块的仿真波形。

3.4 行列缩放实现方案

各种插值算法中,最近邻域法锯齿现象严重,Bezier曲线更适合于外形轮廓设计,样条曲线、分形算法和双三次插值效果很好,但是计算量都很大,速度难以满足实时视频要求,硬件电路规模过大。因此作为数据前道可行性实验实现方案而言,采用双线性插值法,对于缩放比例较小(缩小0.5倍以上或放大3.0倍以下)的情况是完全可以接受的。

用寄存器传输级(RTL)结构实现双线性插值算法时,可采用两种方法,即像素移交(向前映射)法和像素填充(逆向映射)法,如图4所示。

像素移交是将输入图像的像素灰度值逐个转移到输出图像中,但是输出像素坐标不是整数,并且缩小变换时,输出像素将由4个以上输入像素决定,放大变换会漏掉部分输出像素。因此,对于双线性插值算法,考虑使用像素填充法,逐像素、逐行地输出图像,每个像素值最多由4个输入像素值决定。实际处理时,先进行垂直线性插值,将结果存入FIFO,然后再进行水平线性插值。

尺度变换包括4个功能子模块,分别为尺度预处理变换、FIFO、垂直尺度变换和水平尺度变换。尺度预处理根据像素填充法,计算出输出像素点所对应的坐标,坐标的整数部分就是视频数据的像素点,坐标的小数部分就是要进行插值计算的点。先将整数部分的点存入列FIFO,然后将小数部分进行垂直尺度变换,将所得的整列结果存入行FIFO。每当存储完两行,则进行水平尺度变换,得到的数据即为视频输出。图5为尺度变换模块的一种实现框图。图6是尺度变换模块的仿真波形图。

3.5 OLED显示模块

本设计采用型号为DD-160128FC-2A的160×128点阵彩色PM-OLED显示模块,由2.8 V和14 V两组电源供电。该模块使用单片OLED显示驱动控制器SEPS525F0A,完成行驱动、列驱动和显示控制功能。驱动控制器内嵌160×128×18 bit的动态随机存储器(DDRAM),帧速在75~150 f/s内可调,能够显示262k色,具有微处理器接口、RGB接口和丰富的软件功能。值得注意的是,当使用RGB模式时,D[17:12],ENABLE,DOTCLK,HSYNC和VSYNC引脚需要按照6 bit RGB接口指令来操作。否则,后4个引脚要送低电平,同时VSYNCO引脚要悬空[4]。

4 小结

本系统主控芯片采用了低成本、高集成度的Cyclone系列现场可编程逻辑器件,使用Verilog硬件描述语言由顶向下设计,可移植性好,通用性好。在Quartus-II软件中,对所设计的160×128点阵OLED屏的控制电路进行了仿真。试验结果表明,基于FPGA设计的视频驱动器,能够获得理想的控制信号时序,实现对OLED屏的显示控制。

[1]赵东,耿卫东,吴春亚,等.用FPGA实现OLED灰度级显示[J].光电子·激光,2002,13(6):554-558.

[2]李雄杰.OLED电视产业化的技术问题探讨[J].电视技术,2007,31(12):40-42.

[3]MINUG,INH J, KWONOK.A real time video dataadjustingmethod for activematrix organic light emitting diode displayswith high image quality[J].IEEE Transactions on Consumer Electronics,2009,55(4):2372-2376.

[4]STEWARTM,HOWELLRS,PIRESL,etal.Polysilicon TFT technology for active matrix OLED displays[J].IEEE Transactions on Electron Devices,2001,48(5):845-851.

[5]Silicon Image,Inc.SiI1161 panelLink receiver data sheet[EB/OL].[2010-06-10].http://www.siliconimage.com/docs/SiI-DS-0096.pdf.

[6]KIM C,SEONG SM,LEE J A,et al.Winscale: an image scaling algorithm using an area pixelmodel[J].IEEE Transaction on Circuits and Systems for Video Technology,2003,13(6):549-553.

[7]李震梅,董传岱.无源有机电致发光显示驱动电路的研究[J].电视技术,2005,29(2):39-43.