多标准视频解码器顶层重用机制的设计与实现*

董志文 ,张 远 ,史 萍

(1.中国传媒大学 信息工程学院,北京 100024;2.联合信源数字音视频技术(北京)有限公司,北京 100085)

1 引言

视频编码标准的制定和推广极大地推动了多媒体应用技术的发展。目前主流的视频编码标准和技术主要包括MPEG活动图像专家组开发的MPEG-2及MPEG-4标准、ITU-T的VCEG(视频编码专家组)和ISO的MPEG(活动图像专家组)组成的联合视频组(JVT)开发的H.264/MPEG-4 AVC标准[1]、国内的AVS标准[2]以及微软公司开发的VC-1(Video Codec 1)视频编码压缩技术[3]。多样化的视频编码标准使得不同格式的数字视频编解码技术及相关产品将长期共存。如何使一台终端能够兼容多个标准的视频码流成为亟待解决的问题。为解决这一问题,可以采用转码方案,即将多个不同标准的视频码流利用转码技术生成终端可识别的视频码流,但这样通常会使视频质量下降。第二种方案是在解码终端设备中,配置各种视频标准的解码器,以实现终端设备对各种视频信号的兼容,但是这样会随着兼容视频标准数目的增加而提高设计成本。第三种方案是以通用处理器为基础设计支持多标准视频格式的解码器芯片,将多个视频标准的运算单元与存储单元复合在一起,从而在一个解码器芯片上实现多标准视频解码的任务。采用这种方案可克服第一种方案中转码带来的视频质量下降问题,也可大大的降低设计成本[4]。

各视频标准码流在数据格式上以及算法结构上存在着一定程度的相似性,这为支持多标准视频解码的芯片设计提供了可能性。例如在数据格式上,各视频标准均符合序列层、图像层、片层、块数据层这样一个数据组织形式,因此可将传统的解码流程设计成系统层、图像层、宏块层、子块层这样一个通用的解码流程;在算法结构上,基本上都采用了离散余弦变换(DCT)算法去除空间冗余、采用帧间预测及运动补偿算法去除时间冗余、采用熵编码等算法进一步进行视频流数据的压缩等,因此,在解码器的设计中,可将这些算法单元复合在一起使用,实现各标准之间的算法重用。

本文主要讨论多标准视频解码器顶层部分,也就是在解码流程中处于宏块层以上部分的重用机制,并在文献[4]和文献[5]中介绍的重用机制的基础上分析并设计了一种适用于 MPEG-2,MPEG-4,H.264,AVS 以及 VC-1 等标准的顶层模块重用机制。

2 多标准解码器重用机制的可行性分析

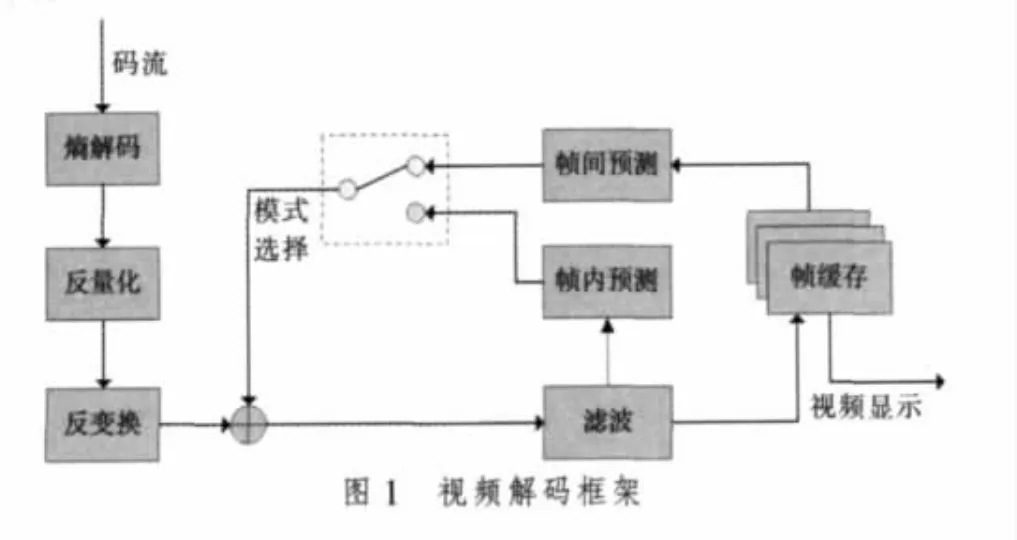

目前主流的视频编码标准采用的都是基于变换、运动补偿预测和熵编码的混合编码结构框架[6-7]。变换采用DCT变换,量化采用标量量化方式,运动补偿采用基于块匹配的运动估计方法,熵编码采用变长编码。因此,解码端的主要处理流程和处理技术基本相似,如图1所示。在处理流程上,这些标准基本都符合熵解码、反量化、反变换、帧间预测、运动补偿的解码顺序,且基本都符合序列层、图像层、宏块层、块层的语法结构层次。这些特点为运算和控制单元可重用的多标准解码器设计提供了理论基础。同时,视频解码器芯片的设计普遍采用宏块级的数据流驱动控制策略,所以缓冲区和参考帧存储区也可以被重用。

3 多标准解码器顶层重用方案设计

3.1 解码器顶层结构重用

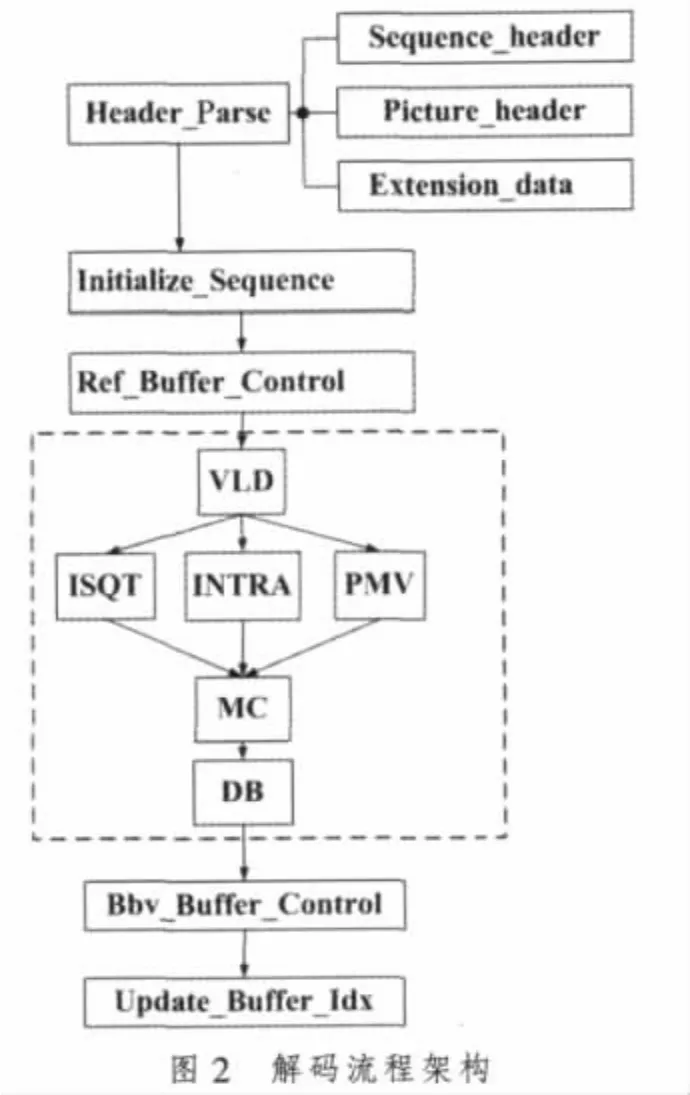

在视频标准中,顶层模块是指在语法结构层次中处于宏块级以上的解码部分,其他处于语法结构层次中宏块级及其以下的解码部分称为底层模块。在MPEG-2,MPEG-4,H.264,AVS标准和VC-1中,码流结构基本都由序列头、图像头、片头及像素编码数据组成,但在细节方面存在差异。以图像头信息为例,在H.264码流中并非所有的图像帧都有图像头。AVS规定一帧中的两场至少有一个图像头。MPEG-2及MPEG-4标准规定所有的图像数据前都有图像头。在MPEG-4中并没有片头的概念,只有宏块组的概念。在VC-1中并非所有的图像前都有图像头,且VC-1的简单档次中没有起始码前缀标志(0x000001),这与其他标准不同。尽管存在这些差异,这几个视频标准采用了相似的顶层解码流程结构。在多标准解码器的设计中可使用图2中的结构,从而实现顶层结构的重用。图2中虚线内部分表示底层模块,虚线外部分表示顶层模块。顶层模块主要包括Head_Parse,Initialize_Sequence,Ref_Buffer_Control,Bbv_Buffer_Ctrl,和Update_Buffer_Idx等。Head_Parse模块解析顶层的部分头信息,包括序列参数、图像参数和一些扩展信息等;Initialize_Sequence模块初始化解码当前序列所需要的一些参数;Ref_Buffer_Control模块负责参考帧管理的操作;Bbv_Buffer_Ctrl模块中进行刷新码流缓存区的操作;Update_Buffer_Idx模块进行刷新参考帧帧存索引以及帧存显示的操作。

3.2 顶层语法元素

解析重用

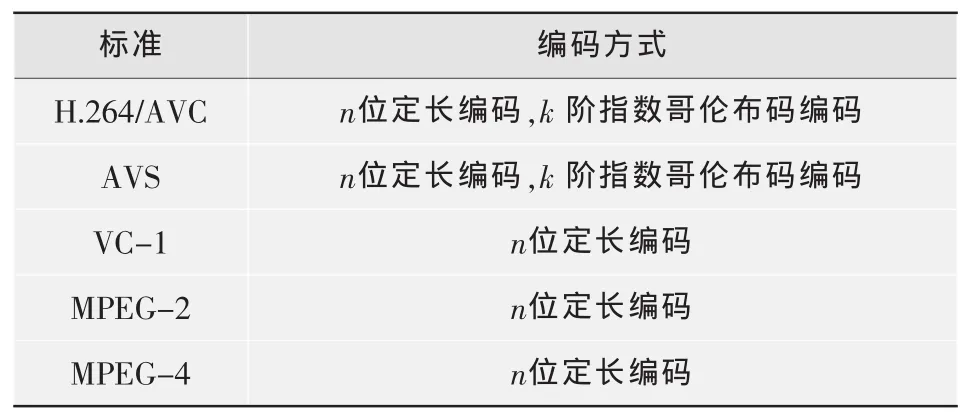

顶层语法元素是指视频码流中处于宏块级以上的语法元素,主要包含解码所必需的参数,如序列参数和图像参数等。在不同的标准中,一般使用不同的编码方法表示这些顶层的语法元素,如无符号定长编码和哥伦布编码。通过对各标准的分析与归纳,顶层使用的语法元素编码方式如表1所示。

表1 各标准顶层语法元素的编码方式

从表1可看出,n位定长编码是几种标准都使用的编码方法,k阶指数哥伦布编码用于H.264及AVS的顶层语法元素。定长码的解码过程比较简单,只需要按照给定的码字长度,从码流中截取相应位数的比特位,再根据需要选择查表或者是直接返回截取的比特位即可。哥伦布编码是变长编码,解码要相对复杂一些。

AVS标准中定义了9种不同的语法元素解析方式,顶层解码用到的主要有以下几种:

1)u(n),n位无符号整数。在语法表中,如果n的值为v,其比特数由其他语法元素值确定。解析过程由函数read_bits(n)的返回值规定,该返回值用高位在前的二进制表示。

2) r(n),连续 n 个 0。 解析过程由函数 read_bits(n)的返回值规定。

3)i(n),n 位整数。 在语法表中,如果 n的值为 v,其比特数由其他语法元素值确定。解析过程由函数read_bits(n)的返回值规定,该返回值用高位在前的2的补码表示。

4)f(n),取特定值的连续n个比特。解析过程由函数 read_bits(n)的返回值规定。

5)b(8),一个任意取值的字节。解析过程由函数read_bits(8)的返回值规定。

6)ue(v),无符号整数指数哥伦布码编码的语法元素,左位在先。

在H.264标准中,顶层用到的语法元素解析方式主要有 b(8),f(n),i(n),u(n)及 ue(v),其含义与 AVS 中的相同。

MPEG-2与MPEG-4标准中的语法元素解析方式主要有以下几种:1) Bslbf(bit string,left bit first),比特串,左位优先。2)Uimsbf(unsigned integer,most-significantbit first),无符号整数,最高位优先。

3) Simsbf(signed integer,in twos complements format,most significant(signed) bit first),有符号整数,2 的补码形式,最高位(符号位)在先。

VC-1标准中,顶层用到的语法元素解析方式主要有Uimsbf和Bslbf,其含义同MPEG-2标准中的定义。因此,在多标准解码器的设计中,可在顶层语法元素解析模块中重用定长解码模块,对于H.264及AVS标准可重用哥伦布解码,从而实现有效的重用结构,以实现代码的优化与管理。

3.3 参考帧管理机制重用

在前文所述的5个视频标准中,H.264采用最多16个参考帧的参考帧管理方式;AVS采用最多两帧的参考帧管理方式(其中P帧前向最多两帧,B帧前后各一帧);MPEG-2,MPEG-4和VC-1采用最多两帧的参考帧管理方式(其中P帧前向最多一帧,B帧前后向各一帧)。

鉴于H.264的参考帧管理方式与其他标准不同,笔者设计了两种管理方式,一种是专门针对于H.264的参考帧管理机制,另一种是为AVS,MPEG-2,MPEG-4和VC-1这4个标准而设计的一种参考帧管理重用方案。其中适用于AVS,MPEG-2,MPEG-4以及VC-1的参考帧管理重用方案的主要技术要点如下:

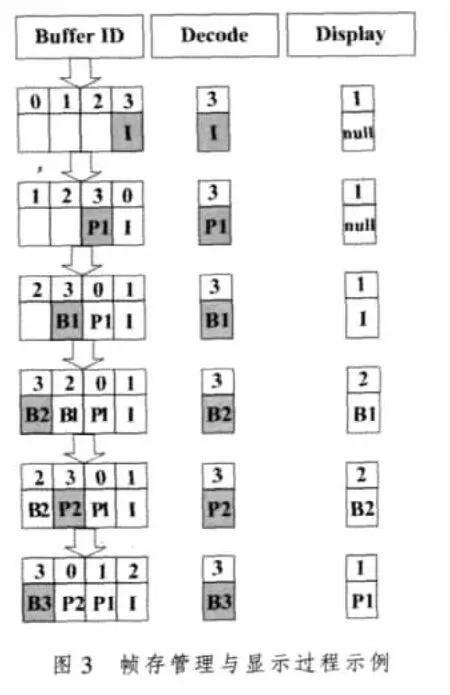

1) 分配4个帧存缓冲区,分别标识为 0,1,2,3。 其中,3表示写入缓存区的索引号,0表示后向参考帧的缓存区索引号,1表示前向参考帧的缓存区索引号。

2)每次帧存索引号的刷新都在解码一帧后进行。索引刷新过程为:当前解码帧为非B帧时,帧存索引值均加1(3号要变为0号);当前解码帧为B帧时,帧存索引值中的2号与3号互换。

3)帧图像的显示在帧存号索引刷新之后进行。帧图像显示过程为:当前解码帧为非B帧时,显示1号所指向的帧存空间数据;当前解码帧为B帧时,显示2号所指向的帧存空间数据。参考帧管理的过程如图3所示。

4)对于场的情况,只对本帧的第一场进行帧存索引号的刷新操作。

3.4 码流缓存区设计与管理

在多标准视频解码的流水线设计中,需要为顶层解码以及VLD模块提供足够的码流以防止缓冲区下溢,从而流畅地解码,因此需要设计一个适用于多标准解码并且可重复利用的码流缓存区域,这部分的主要技术要点有:

1)为保证VLD解码对码流数据的正确请求,必须保证码流缓存中的有效数据足以维持至少一个片或一帧图像的所有宏块数据解码。

2)码流缓存的刷新操作位于解码完毕一个片或一帧图像之后。

3)缓存区的管理必须能够模拟硬件对码流数据的刷新操作。

4)为适应硬件读写操作,缓存区的读写位宽为32 bit。

根据以上技术要点,设计出如下方案。码流缓存区的大小根据不同的图像格式进行动态分配。以CIF(352×288),4∶2∶0格式的视频图像为例,首先设定码流缓存区大小为0x80000 byte(考虑到无压缩情况下4帧码流的数据量大小)。在第一次刷新缓存区的码流数据时,首先填充0x40000 byte(如果码流足够),之后在每次解码一帧后进行缓存区的刷新操作。

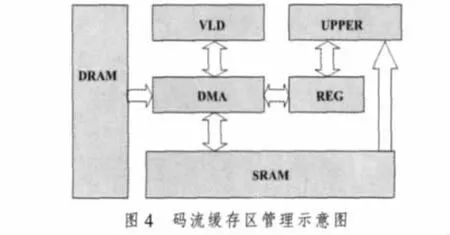

缓存区的刷新判断操作位于顶层的Bbv_Buffer_Ctrl模块,在每次解码完一个片后进行。如图4所示,SRAM为码流缓存区,DRAM为外部大容量存储器。VLD解码一个片后所得到的码流数据偏移地址通过DMA及寄存器REG模块传给顶层模块,当发现缓存区的有效数据小于整个码流缓存区容量的1/4时,顶层模块执行缓存区的刷新操作,将码流数据从DRAM读入到SRAM中;否则不执行刷新操作。设定码流缓存区的1/4大小为判定依据是因为考虑到每帧只划一个片时所对应的最大片数据量。缓存区的刷新仍通过DMA模块完成,且刷新操作要使得码流数据填充满所有的缓存区空间。

4 小结

本文对多标准视频解码器的顶层结构的重用方案进行了分析和设计。通过cmodel的验证,设计的顶层方案可实现正确解码。该方案对于多标准解码器的软硬件协同设计有一定的指导意义。

[1]Draft ITU-T recommendation and final draft international standard of joint video specification(ITU-T Rec.H.264/ISO/IEC 14496-10 AVC)[S].2003.

[2]数字音视频编码技术标准工作组.信息技术 先进音视频编码 第2部分:视频[S].2006.

[3]SMPTE,VC-1 compressed video bitstream formatand decoding process[S].2005.

[4]谢朝辉.多模视频解码器复用方法研究与运动补偿的实现[D].兰州:兰州大学,2006.

[5]汪毅,林祖伦.新一代多模视频解码芯片的硬件结构设计[D].成都:电子科技大学,2008.

[6]毕厚杰.新一代视频压缩编码标准——H.264/AVC[M].北京:人民邮电出版社,2005.

[7]李玖玲,邓记才.H.264/AVC中运动估计搜索算法研究[J].电视技术,2009,33(S1):38-39.