基于PCIe总线的超高速信号采集卡的设计

王 伟,傅其祥

(国防科技大学 电子科学与工程学院,湖南 长沙410073)

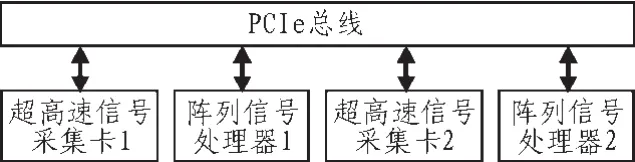

在雷达对抗系统中,需要对于雷达信号进行实时测频,并可以对感兴趣的信号进行储频,为假目标欺骗干扰或压制干扰提供测频结果和储频数据。而数字测频是当今发展最快的测频技术之一。数字测频、储频的关键技术之一即是超高速、高精度、不间断的信号采集技术。采样速率和精度的不断提高,使得数据传输和存储越来越成为数据采集系统的技术瓶颈[1-2]。目前大部分高性能数据采集卡都是基于PCI、CPCI、VME等总线,最高持续传输速率难以超过400 MB/s,因此大多数采集卡采用采集和存储分时工作的模式,即在板内设有一定容量的存储器,当存储器存储数据到一定量时,停止采集而开始上传数据,上传完毕后再重新启动采集,不断循环[3-4],文献[5]也提出采集传输的流水工作模式,提高采集的效率。这些工作方式虽然也能满足大部分数据采集的要求,但是在信号非常密集的环境中,交替工作模式将导致侦察截获概率降低,带来干扰的效能下降。基于上述原因,本文论述了一种基于PCIe总线的数据采集卡,该采集卡不但可以达到800 MHz/s采样率、14 bit采样精度,还具有不间断采集、实时上传的能力(在测频只取其中8位分辨力,储频时取14位分辨力,根据系统的总数据量可编程)。该采集卡可以与高速信号处理器配合使用,构成信道化的数字测频、储频系统,双信道系统的组成示意图见图1。

图1双信道数字测频储频系统示意图

1 系统总体设计

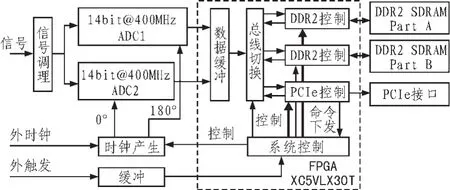

本采集卡的设计主要包括超高速A/D转换器模块、时钟产生模块、大容量存储器模块和基于FPGA的控制模块。如图2所示,待采集的模拟信号经过信号调理放大到合适的电平范围,送入到两片工作于交叉采样模式的A/D转换器,转化后数字信号直接送至FPGA控制器,在FPGA内部实现信号电平转换数据缓冲后,首先存储于A路动态存储器中,当A路存储器存满后,数据立即转存于B路存储器,同时启动数据上传操作,将A路存储器的数据通过DMA方式上传至主机存储或传输到信号处理板中;当B路存储器存满后,数据存储立即切换至A路存储器,同时也启动B路存储器的上传操作,如此反复循环。由于PCIe接口传输速率大于信号采集速率,因此可以保证数据的不丢失。

图2系统总体设计原理图

2 双路高速高精度A/D转换器设计

高速A/D转换器模块是采集卡工作的最前端,它的设计优劣将决定着采集卡的性能指标。其中信号调理部分的功能就是在保证待测信号不失真的前提下,对输入的信号进行低噪声放大、滤波等处理。由于待采集的信号为高频信号,需要进行阻抗匹配和前置放大,可以选用低失真的有源放大器或射频变压器。有源放大器的优点是输入动态范围大,在一定带宽内增益可调,缺点是有源设计会引入一定噪声;射频变压器的优点是无源设计、带宽相对高,缺点是增益固定不可调,输入信号的幅度受到限制,并且给系统带来插入损耗。综合考虑系统设计指标要求,本系统选用TI公司的THS4509放大器作为信号调理器件,该运放具有非常好的宽带特性,增益设置为10 dB时,-3 dB带宽达1 900 MHz,单电源供电以及输出共模电压可调的特性使得THS4509非常适合于高性能的信号采集系统中;考虑到目前市场上难以得到单片A/D转换器可以达到800 MHz/s采样率和14 bit分辨率的设计指标,因此采用了两片ADS5474作为本采集卡的A/D转换器,该A/D转换器的最高采样率为400 MHz/s,14 bit的分辨率,-3 dB带宽达1 400 MHz,LVDS电平的信号输出可以直接连接至FPGA处理器,方便了系统设计,两片ADS5474工作于交叉采样模式,达到了等效于800 MHz/s的采样效果。

信号采集是连续的,而数据的上传是由主机软件通过DMA方式间断获取,因此需要设计大容量的存储器以缓存数据,同时为了达到不间断采集目的,设计了两块存储区采用乒乓缓存的工作方式,即一块存储区用于缓存A/D转换器高速数据时,另一块存储区用于将先前已存储的数据上传。大容量内存采用Micron公司的内存模块MT4HTF3264HY-53E,该内存模块容量256 MB,数据总线宽度64 bit,采用SODIMM封装形式,数据访问带宽最高可达4.3 GB/s,远超出本系统的需求。

当采集卡工作于最高采样率800 MHz/s、14 bit分辨率时,转换的数据率将会达到1.6 GB/s,给后续的数据传输带来非常大的压力。常用的总线如PCI,PXI等已经满足不了如此高的速率要求,本系统采用了8通道的PCIe总线来实现高速数据传输,每通道运行速率2.5 Gb/s,采用8b/10b编解码方式工作,可以得到总数据带宽约2 GB/s,达到实时传输数据的要求。

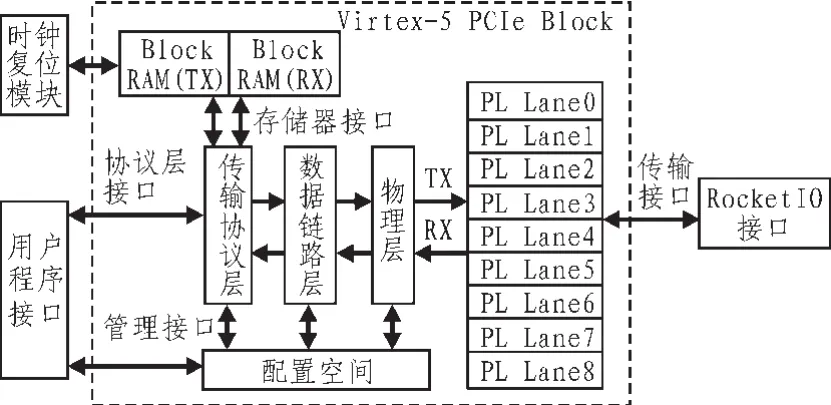

3 基于IPCORE的PCIe控制接口设计

PCIe接口控制电路是本采集卡的关键模块,通过PCIe控制核完成主机与采集卡的数据交互。PCIe拥有多种组件类型,每一类型均采用了复杂的系统级折衷方案,以满足严格的设计目标。为了能加快产品研发进度,本设计采用Xilinx公司的Logicore IP for PCI Express来设计PCIe高性能互连设计接口[6],该IP核占用FPGA资源少、功耗低,包含有物理层、数据链路层、传输协议层和配置空间。如图3所示,层与层之间有明确的分工,相比PCI总线不分层的协议描述更加抽象,传输协议层与数据链路层负责将采集到的数据按批次组包,包在层与层之间传递时会附加对应的校验和帧信息。PCIe标准使用应答重传机制,在数据链路层包括相应的应答延迟和重传延迟定时器,这两个定时器收到串行解串模块与传输介质延迟的影响比较大,太小的重传延迟往往会造成不必要的重传,从而显著降低性能,因此在不同的采集环境下需要进行针对性的调整。设计中这两个定时器的值可以通过软件界面进行配置修改,通过驱动软件来动态修正两个定时器以达到采集传输性能的最优化。

图3基于FPGA的PCIe控制核设计原理图

4 基于FPGA的时序控制设计

采集的时序控制也是基于FPGA完成的,采用了Xilinx公司65 nm工艺的XC5VLX30T,内部资源非常丰富,总线速度最高可达550 MHz,系统的时序控制主要包括DDR2控制器模块和系统采集状态时序控制模块。

4.1 基于FPGA的DDR2控制器设计

设计DDR2控制器完成对两块SODIMM存储器的访问:DDR2控制器是通过行地址选择 (RAS#)、列地址选择(CAS#)、写使能(WE#)、时钟使能(CKE)和芯片选择(CS#)一组控制信号线组合成控制命令,来完成对DDR2 SDRAM的操作,如加载模式寄存器、自动刷新、预充电、选择组激活行、写命令、读命令和空操作。DDR2控制器由物理层、主控制器和用户控制接口组成,如图4所示。物理层由存储器初始化逻辑和地址/命令/数据的I/O逻辑组成;主控制器层包括DDR2 SDRAM控制器状态机和用于地址/命令/数据的FIFO逻辑。其中,物理层是外部DDR2存储器总线的直接接口,提供存储器工作所需要的时钟信号、地址/命令信号和数据读写总线,系统上电和复位时执行初始化和读时序校准操作;用户控制接口为外部应用接口提供3个FIFO来发送命令和数据到存储器和从存储器中读取数据;主控制器在物理层执行完初始化和读时序校准操作后接管地址/命令总线控制权,根据用户控制接口块的命令产生存储器控制命令(如读、写、预充电等)。

图4 基于FPGA的DDR2控制器的设计

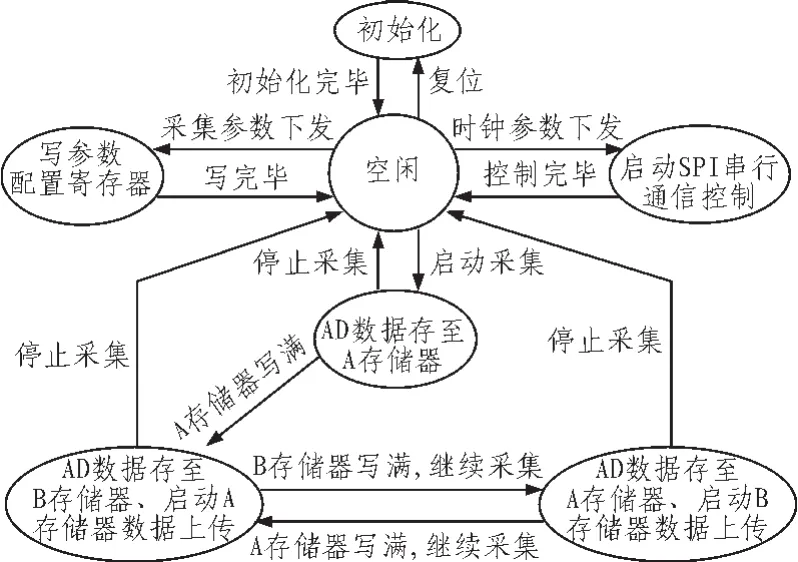

4.2 系统采集时序控制

系统控制模块完成采集数据上传、主机命令的下发和执行:系统控制采用有限状态机的控制方式,如图5所示。当系统上电后控制器默认进入初始化状态,完成默认参数的配置,包括采样频率、采样深度、触发方式、时钟源的选择、模拟输入的量程和耦合方式等,初始化执行完毕后进入空闲状态,等待接收主机命令和执行操作;当接收到启动采集的命令后,控制器首先将AD输入的数据总线挂接在内存A数据总线上,并启动内存A的DDR2控制器执行写操作;当内存A存储到软件设定的深度或存满时,切换AD输入的数据总线挂接在内存B数据总线上,启动内存B的DDR2控制器执行写入操作,同时通过DMA中断通知主机,等待主机上传内存A中的数据;如此反复循环工作,直到收到主机停止采集的命令再返回到空闲状态。

图5 系统控制器的状态转移图

5 结束语

本文介绍了基于PCIe高速串行总线和FPGA控制器的超高速信号采集卡的设计技术,实现了不间断采样和连续传输等关键技术。采集到的信号频谱见图6。该采集卡已应用于某雷达侦察和干扰系统,取得了良好的效果,具有重要的实用价值。

图6 采集到的信号频谱

[1]周振安,范良龙.数据采集系统的设计与实践[M].北京:地震出版社,2005.

[2]张卫杰,侯孝民.高速大容量数据采集系统设计与实现[J].电子测量与仪器学报,2005(4):51-55.

[3]王伟,邱兆坤,姜卫东,等.雷达目标特性数据自动采集技术研究[J].信号处理,2002,18(6):530-534.

[4]付强.雷达目标回波数据采集系统的设计与实现[J].系统工程与电子技术,1995(9):71-76.

[5]米根锁,王瑞峰.基于PCI总线的流水式高速采集系统设计[J].自动化仪表,2006(8):32-36.

[6]Xilinx.Virtex-5 FPGA integrated endpoint blockfor PCI express designs[EB/OL].2008.http://www.xilinx.com/support/documentation/user_guides/ug197.pdf.