FPGA在空空导弹武器系统测试中的应用

国海峰,范惠林,陈丹强

(空军航空大学,长春 130022)

某型空空导弹是我军装备的先进的主动雷达复合空空导弹,在我国先进战机上都有挂载,其作战性能的好坏直接关系到航空兵的超视距作战能力。因此,空空导弹武器系统的技术保障显得尤为重要。针对目前空空导弹现有测试设备检测效率低、使用复杂、设备故障率高、功能单一等缺点,构建了基于VXI总线的测试系统。极大的提高了保障设备的效率和可靠性。在导弹发射时序测试中应用了现场可编程门阵列 FPGA(Field Programmable Gate Arrays)对空空导弹发射控制逻辑进行测试,实现了测试设备自动化,解决了测试设备必须等待信号、易打断测试流程的问题,应用VHDL多进程程的编程方法实现了系统的并行测试。

1 空空导弹的发射控制原理

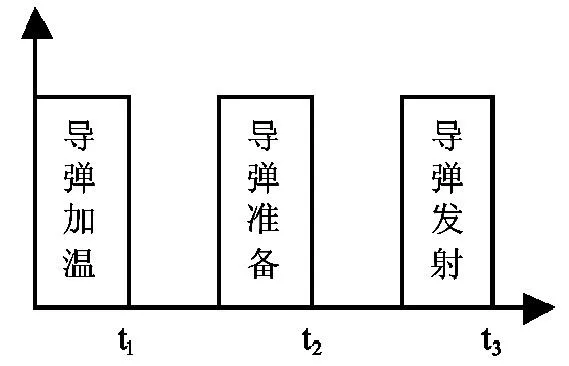

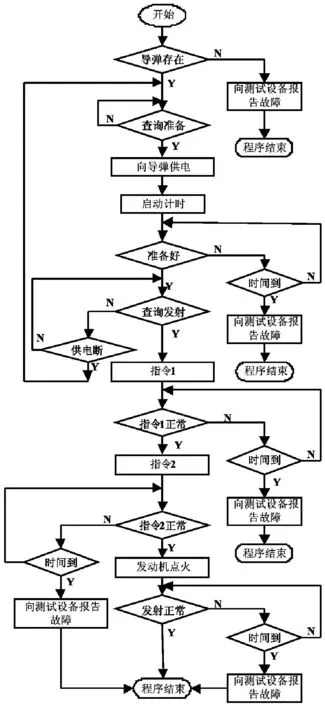

空空导弹的发射控制过程分为导弹加温、导弹准备和导弹发射三个阶段[1],如图1所示。

图1 导弹的发射时序Fig.1 The launch scheduling of the missile

发射控制流程如下:在导弹加温阶段,主要完成对导弹的加温供电,如果加温正常,则返回加温正常信号给发射控制装置,等待一定的时间,等待导弹准备信号的到来,从而进入导弹准备阶段,在导弹准备阶段,导弹完成空中修正,目标对准等指令,飞行控制系统传递攻击任务参数,准备工作完成后,导弹会回送准备好信号,满足发射条件后,飞行员按下发射按钮,导弹进入发射阶段,接收点火信号,点燃发动机,脱离导弹发射装置,完成导弹发射。

2 基于FPGA的时序控制电路的设计与实现

2.1 FPGA及编程环境选择

根据可用逻辑门、I/O数目和 EAB模块的需求,本设计采用Actel公司的ProASIC3型FPGA产品,内核设计在该公司提供的集成开发环境Libero-IDE8.4下完成的,综合工具采用了Synplify公司的Synthesis 9.6A工具,仿真工具采用MentorGraphic公司的ModelSim 6.4A软件。

硬件描述语言的作用是把待设计的逻辑功能、实现该功能的算法、选用的电路结构和逻辑模块输入计算机,至今已有百余种之多,如Texas公司的HIHDL、Carnegie-Mellon大学的ISP、GatewayDesign Automation公司的Verilog HDL和美国国防部提出的 VHDL等[2]。本系统编程语言采用 VHDL来编写。

2.2 硬件的开发与设计

发射控制装置和测试设备之间的交联信号数量多,逻辑关系复杂。考虑到测试系统可以直接跟发射控制装置之间进行数字信息的传输,不需要对其进行时序控制。其硬件结构图如图2所示。

图2 硬件结构图Fig.2 The structure of the hardware

发射控制装置向FPGA发送的指令经电平转换后,送入FPGA进行处理,作出响应,一方面输出至发射控制装置,发射控制装置根据传来的信号作出响应,传给飞机在多功能显示器上显示;另一方面输出至测试设备进行显示,响应测试步骤。在测试设备中选择故障设置,输出控制信号控制FPGA模拟发射故障。

2.2.1 电平转换电路

发射控制装置与空空导弹之间传输的信号有的高电平有效,有的是低电平有效,但其有效电压都为28V,而FPGA工作在TTL电平或CMOS电平下,所以输入输出电平要按照要求进行相应的变换。输入输出信号的变换都采用光电耦合电路设计。

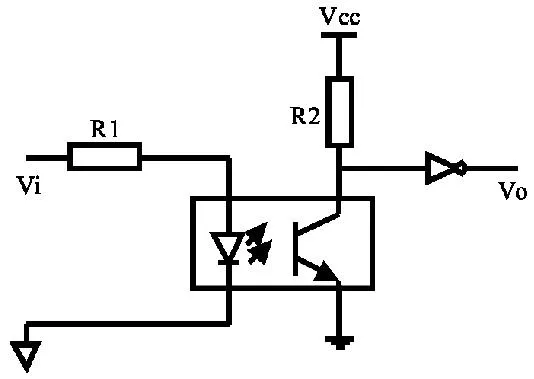

(1)输入信号的变换[3]

图3 输入信号变换Fig.3 The change of the input signal

当有28V信号输入时,光敏二极管导通,进行光电耦合,经反相器反相,输入“1”,当没有信号输入时,输出为“0”。若信号是低电平有效的,不需要输出信号之前的反相器。

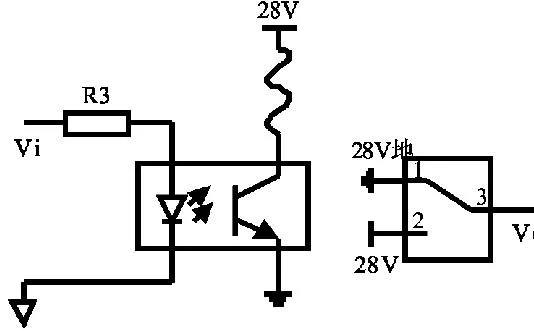

(2)输出信号的变换

图4 输出信号变换Fig.4 The change of the output signal

当TTL电平为高时,光电耦合单元工作,驱动右侧继电器吸合,输出28V,当TTL电平为低时正好相反,输入为0V。

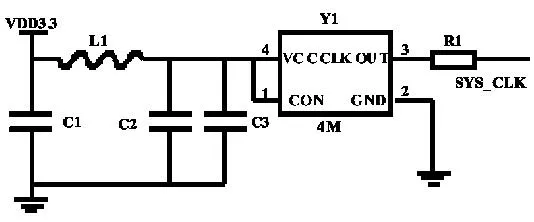

2.2.2 时钟、复位电路

图5 时钟电路Fig.5 The clock circuit

由于导弹发射流程中要判断信号响应时间,需要为FPGA设计时钟电路,采用晶振时钟电路,如图5所示。

当整个系统复位时,FPGA也要完成复位,利用上位机控制一个D触发器的方式完成FPGA的复位。

2.3 软件的设计

软件包括上位机控制软件和FPGA内核软件,软件的时序控制是整个空空导弹测试系统的核心,完成对空空导弹发射流程的时序控制以及对测试设备故障的响应。程序的主框架流程,以空空导弹的发射时序控制流程为主线,依次完成系统初始化、故障识别、测试信号的输入输出等功能。

图6 主程序流程图Fig.6 The flow chart of the main program

图7 正常时序逻辑图Fig.7 The logic diagram of the normal scheduling

2.3.1 上位机程序的编写

测试设备作为上位机在导弹发射流程测试中实现对FPGA的控制和故障判别显示,上位机程序采用 LabWidows/CVI编写,其主要功能包括:控制FPGA的开始和复位;向FPGA发送故障设置控制指令;接收FPGA发送来的故障响应指令。

上位机可以设置的故障有:导弹存在故障、导弹准备故障、导弹电池故障、舵机故障和导弹未发射故障。

2.3.2 软件开发流程

根据某型空空导弹的发射流程和测试系统对时序控制循环检测,自动检测的要求,软件的开发采用模块化的设计思想,按空空导弹的发射流程分为三个模块,加温模块、准备模块和发射模块。前一个模块的输出作为后一个模块的输入,顺序执行程序。

空空导弹的挂点有多个,为了满足并行测试的要求,软件采用多线程并行调用的方式,每一个测试点作为一个进程,按照挂点选择同时运行测试程序。其单个挂点的主程序流程图如图6所示。

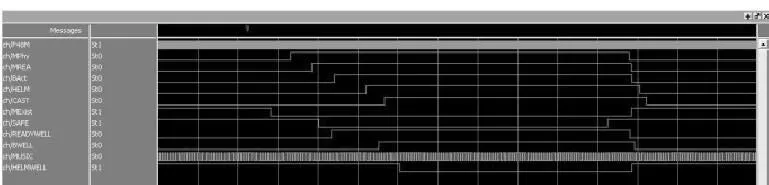

2.3.3 程序的仿真结果

程序的仿真包括无故障情况下的仿真和有故障条件下的时序仿真,本文只给出正常时序下的仿真,如图7所示。

由时序仿真波形可看出,各信号的逻辑关系符合空空导弹发射控制流程,该程序能够满足测试系统对于导弹发射控制测试的要求。

3 结束语

FPGA应用于空空导弹武器系统测试中控制导弹的发射流程,解决了以往的测试设备中必须人为按照测试步骤进行测试的问题,实现了系统的自动测试和故障设置。应用多进程的编程方法,解决了并行测试的问题,提高了测试效率。这对提高武器系统,特别是先进导弹的武器系统的战斗力具有十分重要的意义,对于同类产品的研制也有一定的借鉴意义。

[1]孟秀云.导弹制导与控制系统原理[M].北京:北京理工大学出版社,2003.

[2]阎华,王民钢,王桂华.导弹模拟系统嵌入式电子组件的设计与实现[J].计算机测量与控制,2007,15(2):202-204.

[3]闫春光,姜文志,丰海波.基于FPGA的某发控仪模拟器设计[J].指挥控制与仿真,2006,28(6):96-99.