基于FPGA的HDB3编码方法及其在测井电缆传输中的应用研究

李丰波,鞠晓东,卢俊强

(中国石油大学油气资源与探测国家重点实验室,北京102249)

0 引 言

测井技术的新发展迫切需要获取井下更丰富更真实的岩性、物性、含油性及渗透性等方面的数据信息,这使得井下数据信息量成级数式的增长。国内外电缆测井的数据信息传输通道通常是铠装7芯电缆,国产的如W7BP/W7BPP型,国外的如Rochester Wire &Cable公司7-H-464A型等。然而,受电缆自身性能及制造工艺的限制,还有井下高温、高压及冲击、振动和井下空间狭小等恶劣环境的影响,测井电缆数据传输速率低,信号衰减、失真及干扰也比较严重,而且数据容量、带宽亦有限。由此可见,测井电缆数据传输的问题已经成为了现代测井系统发展的瓶颈。因此,对先进的数据编码调制方式及适合测井实际应用环境的高速数据传输系统的研究很有意义。

1 几种主要的电缆测井数据传输编码技术

测井电缆的传输性能与所传输信号的频率关系密切[1],当频率超过100kHz时,信号衰减和时延特性变差使得难以对信道解码。而且测井电缆的两端是通过变压器实现耦合,低频信号(<100Hz)在耦合时必然衰减严重,故可将其视为频带宽度有限的带通信道。

因此,为了充分利用测井电缆有限的带宽资源,提高信息的传输速率,数据必须有适当的编码调制方式,研究更适合测井电缆数据传输的数据编码调制方式便显得尤为重要。

(1)双二进制码/调制双二进制码。Halliburton EXCELL-2000成像测井系统使用的数字通信系统DITS,上传数据用的是调制双二进制码。这种码的特点是用同样的带宽可以传输2倍的数据量,但代价是信噪比降低,波形畸变严重,接收端恢复困难变大,增加了地面通信接口D2MP的难度和复杂性。

(2)正交振幅调制QAM。这是高速传输系统中使用的一种编码技术,如Schlumberger公司MAXIS-500测井系统中的DTS数字遥测系统,上传数据可以实现高达500kbit/s的传输速率。还有国产的EILog系统,采用COFDM(正交频分复用)调制,上传数据时其子信道内即采用16/32QAM方式,传输速率可以达到300kbit/s。QAM虽然传输速率高,但其编译码过程相当复杂[2],井下部分更要考虑其特殊环境下的工艺要求。

(3)曼彻斯特码。它是测井数据传输中最常用的编码方式之一,如BAKER ATLAS公司早期的PCM3508系统即是采用的曼彻斯特码[3],以及后来的ECLIPS-5700测井系统中的WTS电缆遥传系统中仍然采用的是曼彻斯特码。编解码实现通常的做法是用HD6408(HD15530)与并入串出、串入并出移位寄存器及输入输出缓冲器等外部电路配合完成。

此外还有Schlumberger公司CTS电缆遥测系统中采用的BPSK编码技术[3],以及通过引入受控制的码间干扰来达到压缩传输频带、提高传输速率的相关编码技术[4]等。

2 HDB3码原理

HDB3码(High Density Bipolar of order 3,三阶高密度双极性码)是在AMI码(Alternative Mark Inversion,传号交替反转码)的基础上改进的一种双极性归0码。它除具有AMI码功率谱中无直流分量,可进行差错自检等优点外,还克服了AMI码当信息中出现连0码时定时提取困难的缺点,而且HDB3码频谱能量主要集中在时钟频率1/2范围内,提高了信道频带的利用率。

AMI码就是把单极性脉冲序列中相邻的1码(即正脉冲)变为极性交替的正、负脉冲。即将0码保持不变,把1码变为+l、-1交替的脉冲。HDB3码的编码规则如下:当输入码流连0码小于或等于3个时,用0表示信息0,把1码变为+l、-1交替的脉冲,分别用+B、-B来表示。当出现4个或4个以上连0码时,每4个连0为1节,称为取代节,把每节的第4个0码变为1码,用V码来表示,称为破坏点。而且规定V码的极性与前一非0码相同以便识别,用+V、-V表示。但为了防止破坏码流极性交替反转,必须保证相邻V码的极性交替反转。当相邻V码间非0码的个数为奇数时是可以的,但若为偶数,则必须将其变为奇数,方法是将取代节中第1个0码变成1,极性与前一非0码相反,亦用+B、-B表示,并让后面的非0码从V码开始再交替变化。

在同样的频带宽度下,HDB3码的传输速率能达到曼彻斯特码的2倍左右。若传输速率相同,HDB3码的频带宽度是相关编码信号频带宽度的1倍左右,这对于频带资源十分宝贵的测井电缆来说,大大提高了频带的利用率。相关编码信号在测井电缆中传输时,是一种伪三元序列,有+2、-2电平和0电平,与HDB3的3个电平(+l、0、-1)类似,但其电平比HDB3码的高1倍,这意味着传输相同的信息相关编码需要更大的驱动功率,这对电源及驱动电路提出了更高的要求,而且限于井下的特殊环境,设计中应该尽量减小系统的功耗。

由HDB3码的编码原理可以发现,HDB3码自身就具有检错能力,当传输过程中出现单个误码时,破坏点序列的极性交替规律将受到破坏,因而可以在使用过程中监测传输质量,而其他的编码技术多数需要加上循环冗余检验单元(CRC)来检查信息传输的准确性。

3 试验系统整体设计

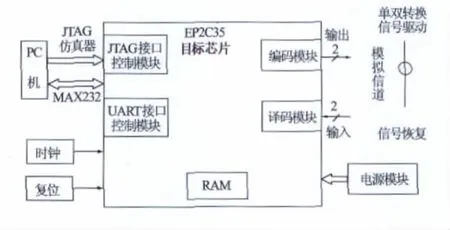

该系统将核心HDB3编、译码模块及相应接口控制模块集成在同一片FPGA(Field Programmable Gate Array)目标芯片中,并通过外接相应模拟电路单元,实现了双极性的HDB3码输出。经过试验用的模拟信道的传输及信号恢复后,再输入到译码模块的输入端进行译码。而且通过RS-232C接口实现同PC机的通讯。PC端将准备好的一批测试数据通过串口发送给编码模块进行编码输出,通过模拟电路进行单双极性转换及驱动,经过在模拟信道上的传输及信号恢复后再经过译码,再将译码得到的数据又通过串口传回给PC端作对比分析处理,通过设计的PC端应用软件,可以得到我们关心的一些信息,如误码率及传输数率等。系统整体示意框图见图1。

图1 系统整体示意框图

该系统主要由主FPGA模块、配置模块、UART接口模块、电源模块、时钟模块等构成。①主FPGA模块。目标FPGA芯片采用Altera支持Nios II嵌入式软核的Cyclone II EP2C35高性价比芯片。它有33 216个Les,4个PLLs,105个M4K RAM blocks,475个用户管脚,有很大的设计利用及升级扩展空间。②配置模块。使用EPCS16配置芯片通过JTAG接口完成对目标FPGA的配置,将.sof文件烧到配置芯片中可以方便地进行在线调试。③UART接口模块。为通用串行通信接口RS-232C,通过MAX232电平转换芯片和9-pin DSUB实现和PC机的通讯及数据交互。④电源模块。EP2C35内核供电电压Vccint为1.2V,I/O供电电压Vccio为3.3V,Cyclone II系列Datasheet上对上电顺序没有特殊说明,但一般先给内核供电。⑤时钟模块。1个50MHz晶振,提供固定时钟频率。1个外部时钟输入通道,可以根据需要另行设置时钟频率。

4 编译码核心模块实现方法

4.1 编码模块原理及设计

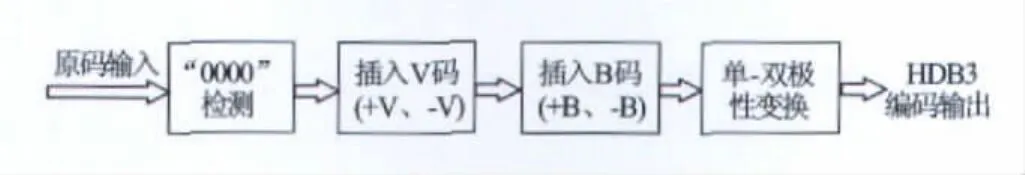

根据HDB3码的编码规则,编码过程首先要做连续0000的检测,目的是要找到插入V码的位置(也称破坏点),同时也为下一步插入B码提供位置参照依据,所以此处如何快速便捷地识别V码也成为关键。故设计在此引入双相码表示法来解决这一难题,V码用11表示,而信码1用01表示,以示区别。根据相邻V码间非0码的奇偶性来判断是否要插入B码,奇偶性的正确判断是此步的关键。FPGA只支持单极性电平,所以要实现单极性到双极性的转换。有的做法是在插入V码、B码的同时就附带极性信息[5],例如+1用101,-1用001表示,这样双相码就变成了三相码,所以最后还要额外进行处理,将三相码转变成双相码,才能转化为2路单极性输出,以便后续模拟电路的处理。为了使设计简洁和节省FPGA内部资源,设计将极性处理放在最后一个环节。编码模块原理示意框图见图2。

图2 HDB3码编码模块流程图

VHDL实体部分端口有时钟端clk、异步清0端clr、源码输入端datain、以及2路单极性输出(HDB3)端dataout等。结构体部分由插V码、插B码及单双极性变换3个process构成。

4.1.1 连0检测及插V码模块设计

因为要通过计连续0码的个数实现连0000检测,所以定义一个内部信号count0计算0的个数。另一个内部信号Vout来表示及暂存插V码后输出的双相码,如前文所述,V码用11表示,信码1用01表示,信码0用00表示。当检测到4个连0时,将第4个0变成V码输出,即Vout≤11,其余则按原码输出。其中要注意的是原码输入为1时,count0也要及时清0,而不仅仅是在检测到连续第4个0后才清0,因为破坏点V码的位置必须是连续的第4个0处。

4.1.2 插B码模块设计

如果把上述插V码后的字符串000V称之为取代节,那么插入B码的位置也即是该节的首个0码处,由于V已用11表示,就很容易识别取代节。B码插入与否是由相邻V码间的非0码(此处也可理解为信码1)的奇偶性来决定的,那么要解决的首要问题是信码1奇偶性的判断问题,由于只需要知道它的奇偶性而不需要知道确切数目,所以该步需用到一个内部信号count1判断奇偶性,值为0表示偶数个1码(0个1也视为偶数),值为1表示有奇数个1码。同时还必须设置一个标志位firstV检测首个V码的位置,作为起始位。B码亦采用双相码10表示,以区别表示1码的01。

与插入V码过程不同,B码的插入不是立即进行的,而是要综合当前的状态信息对过去状态进行判断修改的,即只有当前的输入是V码且与前一V码间的1码个数为偶数(count1=0)时才插入B码,所以该步须定义2个4级移位寄存器作为缓存,R1(3downto 0)存入Vout的高位码,R0(3downto 0)存入Vout的低位码,再定义一个内部信号Bout来表示及暂存插B码后输出的双相码,Bout值为R1(3)&R0(3)。

4.1.3 单双极性变换模块设计

由HDB3码编码规则及前面插V和插B过程知道,B码的极性是和前一非0码极性相反的,这与信码1的极性规律相同。而V码是与前一非0码极性相同的,但相邻V码间的极性仍然满足反转交替,所以可以将B码和信码1看成一类,统一完成极性的反转交替,而V码的极性则由前一相邻的非0码(即B码或1码)的极性来决定,即与之同极性即可。所以定义一个内部信号last_polarity作标志位,表示前一个码的极性,并附初值为0。0表示极性为正,1表示极性为负。最终的双路单极性编码输出dataout则用10表示+1,01表示-1,00表示无极性的0,当然也可以采用其他形式的编码安排。然后将dataout的输出外接到模拟电路单元,实现编码到实际的正负脉冲及0电平的转换。

4.2 译码模块原理及设计

译码过程首先得通过模拟电路单元将输入的双极性HDB3码变换恢复成2路单极性数字编码,然后输入给目标FPGA芯片做译码处理。译码过程流程框图见图3。

图3 HDB3码译码模块流程图

译码的过程就是将取代节还原成0000的过程。取代节的形式通常为000V、B00V等2类,若带上极性,则为+1000+V、-1000-V和+B 00+V、-B 00-V等4种。在正负交替的码流中,只有V码的极性是与前一非0码的极性相同的。利用这一特点便可以找到取代节的位置。所以,码元的极性及码流的组成形式便是译码过程的关键依据。

为此,定义一个内部信号polarity作为标志位来提取码元的极性信息,即当codein为10时,polarity≤1,代表+;当codein为01时,polarity≤0,代表-。还要定义1个内部信号S,表示1个4级的移位寄存器,暂存码流,并根据极性信息及组成形式判断是否为取代节。例如当S(2downto 0)为100或S为1000时,若此时codein为10(即+1)且polarity=1,说明寄存器中的码流即为取代节,将其还原即可,反之亦然;若极性不同,则说明不是取代节,直接移位并且低位S(0)≤1,然后输出即可。若codein为00,则直接移位并且低位S(0)≤0,然后输出即可。译码模块的输出codeout为寄存器的最高位S(3)。

通常的做法是定义2组4级的移位寄存器,分别存放译码输入的高、低位码,再按取代节的不同组合形式分别检测及还原。但设计由于编码时对±1及0编码形式的安排,再加上特意提取极性信息后将2路信号变成1路的设计,故设计只需用1组寄存器S(3downto 0),程序也相对简化,既达到了目的又节省了FPGA内部资源,从而相对优化了设计过程。

5 PC端软件设计

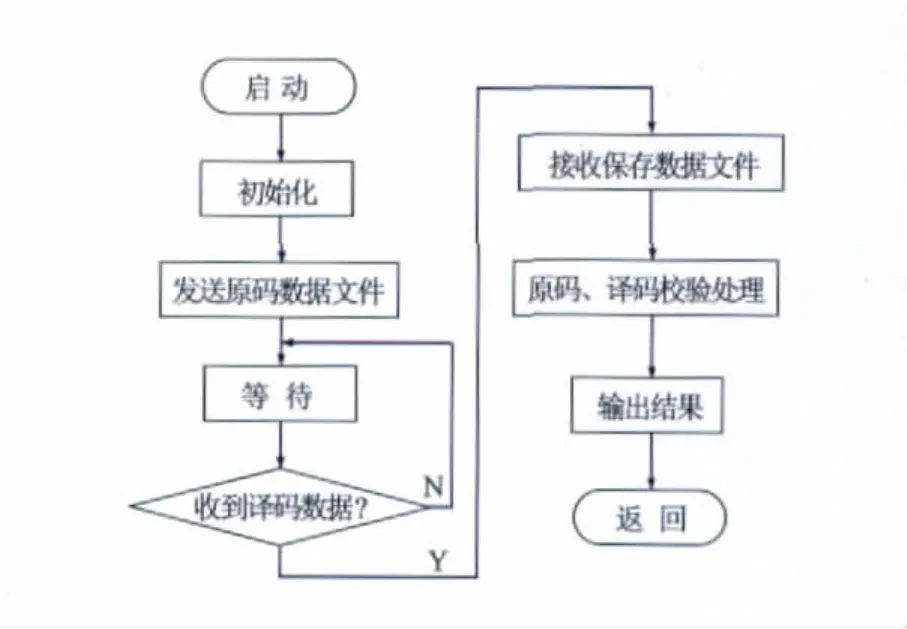

PC端软件主要实现数据的发送和接收,编、译码数据的显示,以及通过对2份数据的对比校验,计算该时段的误码率等功能。在VC++下通过ActiveX控件MSComm完成PC端的通讯程序。原码数据的发送通过MSComm控件的Output属性完成,译码数据的接收可以通过捕获MSComm控件的OnComm事件完成。程序主要流程示意图见图4。

将HDB3码经过试验系统模拟信道传输并经信号恢复及译码后的数据通过串口发送给PC机,PC接收数据后并以文档文件txt形式保存下来。每次从txt文件中读取2个字符即1个字的数据,并将其转化为二进制码显示,读取前均要判断txt文件结束标识符EOF(-1)以判断文件是否结束。通过与原码数据的对比便可以计算误码率。

图4 主要流程示意图

6 结 论

试验系统充分发挥了FPGA的优势,将相应功能模块集成在1块芯片上,简化了硬件的结构,减小了系统的体积,提高了系统的稳定性,缩短了开发周期,而且也便于修改调试,系统小巧灵活。实验系统有效地对电缆测井数据传输过程的关键环节如HDB3编码、模拟信道上的传输、以及接收端译码等进行了实验模拟分析,取得了预期的效果。但仍有进一步研究的空间,如相应数字滤波处理、消除码间干扰的时域均衡处理等,或者为了更进一步提高传输效率而在编码之前先进行数据压缩处理等,均是进一步研究探讨的方向。系统设计时采用高性价比的有丰富资源的EP2C35芯片,正是考虑了系统的扩展性和冗余性,使得在试验系统的基础上进行进一步的研究具有可行性。同时从实现技术上,因为EP2C35还支持Nios II嵌入式软核,所以可以将相应功能模块封装成一个基于Avalon内部总线的软IP核,也即基于Nios II的自定义外设,由Nios II内核控制,实现软硬件协同设计,形成一个SOPC应用系统。

[1] 陈国瑞.成像测井系统中影响电缆传输性能因素的分析[J].现代电子技术,2004,27(04):40-42,45.

[2] 陶立伟,张 伏,王小波,等.全数字16QAM解调器设计与实现[J].无线电工程,2008,38(10):53-55.

[3] 杨建军,林兴春,郝秀权,等.测井电缆通信系统综述[J].石油仪器,2007,21(03):1-4.

[4] 葛 辉,庞巨丰,张芳向,等.几种应用在高速测井电缆传输系统中的编码技术[J].电子测试,2007,(11).

[5] 吴翠娟.基于SOPC技术的HDB3编码器的建模与设计[J].湖南科技学院学报,2009,30(04):82-85.