大规模集成电路中开闭路测试的优化与改进

顾 晨

(上海交通大学通信电子系,上海 200030)

1 引言

在典型的直流测试中,应用PMU(Precision Measurement Unit)对被测芯片进行直流测试,虽然原理简单,但是也存在着弊端,那是由于直流测试时,PMU需要测量出每个引脚的精确值,从而导致测试时间相当长,我们可以从两方面来解决:

(1)对开闭路测试流程进行优化;

(2)对测试方法进行改进,在大规模生产中,运用功能测试的方法(动态电流负载测试和VTT终端电阻测试),将测试结果直接与测试标准进行比较,即可判断出功能测试在时间以及效率上有了显著的提高。

2 开闭路测试的优化

2.1 流程优化

典型的开闭路测试流程是将开路和闭路测试完全分开,共分为4个步骤:上半保护二极管的开路和闭路,下半保护二极管的开路和闭路。

考虑到在对闭路进行测试时,测试状态与保护二极管无关,由此对典型的开闭路测试流程优化改进,在测试下半保护二极管开路的同时,将闭路测试一并进行,如图1。

动态电流负载测试分为两部分:第一部分是专门负责测试被测芯片的短路以及与地面连接的保护二极管的工作状态,在测试与地面连接的保护二极管同时,其实也就进行了一半的开路测试。第二部分专门负责与电源连接的保护二极管的工作状态,其实也就完成了剩余一半的开路测试。这个新流程通过将原有的三部分开闭路测试(闭路测试、上半开路测试、下半开路测试)优化为两部分从而降低了测试时间。

在测量下半二极管开路的时候,对于各个引脚是必须分开测试的,其原因在于除了要测是否开路的同时,我们还要测量每根引脚之间是否与地或者相互短路。一旦通过第一部分的测试后,第二部分就简单了,只需要将所有的引脚同时进行上半二极管的开路测试,无需再重复地测量短路状态,这相对于传统静态直流测试而言,节约了相当可观的测试时间。改进后的测试简易流程如图1。

2.2 测试方法

典型的静态直流测试主要通过PMU向被测芯片灌入IOL(output low current)和IOH(output high current)电流,测量VOL(output low voltage)和VOH(output high voltage)的值,将其精确结果与标准值进行比较。

由于现有的Schlumberger测试机内部都具有PEC3或者PEC4板卡,根据不同的PEC卡的构造,我们可以考虑将其运用在测试方面,从而替代原有的静态直流测试方法。PEC3卡具有动态电流负载电路,而PEC4具有一个VTT的50 Ω终端电阻电路。

PEC3卡中的动态电流负载功能测试方法是运用测试设备内部自带的负载电路作为可编程的电流来源,再通过电压功能比较器将测量出来的电压与VOL或者VOH进行比较,从而输出“通过”或者故障的结果。

在测试时,在程序的pattern中将VDD以及所有不参与测试的引脚全部设置为逻辑0的状态,将待测引脚与动态电流电路接上,同时打开动态电流继电器,当测试动态闭路以及下半二极管开路的时候,在测试程序中将Vref设在-3V,正常情况下,动态电路会从被测芯片中引出IOH电流,大约在-1mA左右,同时将该引脚的电压值通过比较器进行比较,比较的上下限在测试程序中分别设在-1.5V和-0.25V。当测试动态闭路上半二极管开路的时候,在测试程序中将Vref设在3V,正常情况下,动态电路会向被测芯片灌入IOL电流,大约在1mA左右,同时将该引脚的电压值直接和比较器中事先设置好的上下限进行比较,上下限分别设在0.25V和1.5V。在运行该功能测试的时候,需要将测试设备设置为表1和表2的状态,同时运行所需要的patterns,测试结果是直接由patterns中的通过/故障设置比较得出的。

表1和表2的关键在于对芯片引脚初始状态的设定,在测试闭路的时候,需要将所有未测引脚接为逻辑0,这样才能有效地检查出引脚对地或者引脚之间是否有短路的现象。在稍后的开路测试中,就可以将所有引脚直接接在测试电路中进行并行测试,无需担心是否有短路产生。

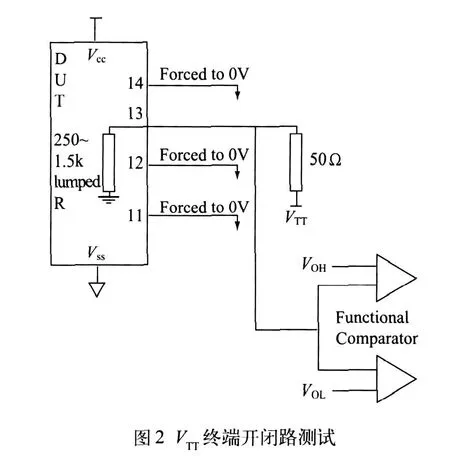

PEC4和PEC3的相同之处在于在电路中都有输出比较器,区别在于PEC3是通过电流负载电路实现电流的灌入和吸出,PEC4则通过一个50 Ω的终端电阻和VTT相连的电路实现。如图2,在VTT的终端点用测试程序设置为-450mV,并在程序的pattern里面将所有不测的引脚都设置为逻辑0状态,这样对于下半个保护二极管来说就是正向偏置,功能比较器的输入所测到的电压是通过保护二极管以及I/O口的降压而得到的,所测量到的电压值与测试程序中设置的上下限做比较,在测试下半二极管的时候,上下限分别设为VOH=-375mV,VOL=-435mV,当测试上半二极管的时候,VTT的终端点用测试程序设为450mV,上下限分别设为VOH=435mV,VOL=100mV。

动态电流负载电路和VTT终端电路的优势在于巧妙地运用了测试机内部的电路结构对被测芯片进行测试,同时无需测量精确直流电压值,从而大大节约了测试时间。

2.3 测试数据比较

为了验证改进后的开闭路测试的测试时间是否有了明显的变化,我们对同一个被测芯片进行实验,发现运用原先直流测试方法得出的开闭路测试时间大约在1s左右,而运用动态功能测试方法所得出的开闭路测试时间大约在190ms,仅一块被测芯片的测试时间就比原先缩短了800ms,一般来说一个批次大约有3 000颗芯片,那么节约的测试时间将达到2 400s,将近40min,对于大规模生产而言,这是相当可观的。

3 结论

这一测试方法的改变对整体测试时间的改进是显而易见的。另外,这两种动态测试方法还能普及到其他静态直流测试项目中,例如VOL/VOH等测试单元中,同样可以取代传统的静态直流测试方法对测试本身进行优化和改进,其测试结果无疑对大规模生产的半导体工厂来说是一个显著降本增效的方法。

[1]陈光禹,潘中良.可测试设计技术[M].北京:电子工业出版社,1997.