基于SOPC的LAMOST光谱仪IP控制核的设计与实现

张 力,王家宁,朱永田,吴莉艳

(1.中国科学院国家天文台南京天文光学技术研究所,江苏 南京 210042;2.中国科学院研究生院,北京 100049)

1 LAMOST多目标光谱仪电控系统的总体设计

光谱仪系统由16台多目标光纤光谱仪组成,正样机的被控部件与样机的被控部件相比有较大的变化,每张控制台上放置十几个可动部件,如何使为数众多的被控部件快速、准确、安全、协调地运动到位,是要解决的问题[1]。16台光谱仪要协同工作合适的方法是构建一个局域网,采用集中分布式控制方案。控制室内放置一台主控制计算机,完成中央控制策略,每台光谱仪设置光谱仪控制器,用来完成本台光谱仪上各运动部件的实时控制和管理。中央控制计算机有人机界面,用以接收操作人员的命令,并将其分解成子命令发送到各个光谱仪的控制器,同时接收被控部件的工作状态和现场数据,归整后发往观测控制系统OCS[2]。

图1 LAMOST低分辨率光谱仪视图Fig.1 The sketch diagram of the low-resolution spectrograph for the LAMOST

根据光学和机械设计,控制对象分为狭缝快门、Hartmann快门(2个)、电动调焦装置、狭缝切换装置、光栅切换装置、照相机转动装置、光纤背照装置等,并预留4个电机接口用作光谱标定。其中快门和狭缝切换装置的位置精度要求一般,其他装置的位置精度要求较高。每个光谱仪平台上放置红区照相机和蓝区照相机2个转台,每个转台上放置2套不同分辨率的光栅,相机转动装置和光栅切换装置的重复定位精度要求较高,被控部件暂定为14[3]。

采用FPGA构建LAMOST低分辨率光谱仪IP控制核。整个系统设计可以划分为硬件和软件两部分。

为了节约开发时间,硬件平台选用现成的FPGA开发板,除了FPGA芯片外,开发板上已经集成了FLASH、SRAM、SDRAM、RJ45接口和串行口等FPGA运行时需要的外设。将光谱仪控制器部分用FPGA片内电路实现,这样只需要设计能完成光谱仪中步进电机动作的步进电机控制电路,再将电路下载至FPGA内即可。而硬件部分不需要改动,这正是使用FPGA设计的优势所在[4]。图2 中的计数器、方向鉴别、零位判别、限位电路、脉冲发送电路和IO读写电路都是片内电路,是需要设计的硬件部分。这部分主要解决步进电机驱动信号的产生和9个步进电机之间的动作时序的协调[5]。

整个底层硬件和控制计算机的交互采用现有的标准9针串行口和工业以太网通信。串行口可以作为本地计算机控制和远程控制时的冗余通信链路,特点是使用方便,实现简单,稳定性好[6]。远程计算机控制时使用工业以太网,接口使用RJ45口,通信协议是UNIX下的标准Socked接口[1]。

系统软件部分包括两部分,一是固化在FLASH里的FPGA上电自加载程序,系统一通电,FPGA即载入这段程序,监听通信端口(串口或RJ45口),如果有相应的命令传送过来,就驱动电机控制器执行相应的动作。这部分又分为通信实现、命令解析和软硬件接口(底层电机控制信号产生)3部分[7]。多个步进电机的协调动作也由这部分软件调度完成;还有一部分是上位机上运行的控制程序,应该有一个友好的控制界面,方便用户进行控制。同时也要有软件通信程序的编写,以便通过控制界面与下位机正常通信。

图2 嵌入式系统组成的光谱仪IP控制器Fig.2 IP controller core of the spectrograph consisting of embedded systems

2 光谱仪IP控制核的硬件设计

2.1 硬件开发器件的选择

为了加快研制速度,减少硬件设计带来的风险,采用了ALTERA公司的基于CycloneⅡ器件的NIOS开发板。所有的开发都基于已有的开发板,这样的好处是硬件部分基本不需改动,只需要完成片内设计和软件设计即可,大大缩短了设计周期。

2.2 片内步进电机控制器设计

从中可以看到,片内电路主要是复用了9个步进电机控制器,这些步进电机控制器挂接在片内AVALON总线上,与NIOS Ⅱ软核通信,并输出步进电机控制信号给步进电机驱动器。9个步进电机之间的协调动作使用软件完成,这些程序固化在板上的FLASH里,一通电就自动运行[1]。

为了缩短设计时间,方便扩展,把步进电机控制器封装为一个IP核,可以在SOPC Builder里重复调用。所谓IP核的封装就是将用户设计的完成某一功能的逻辑电路作为一个整体组件封装起来,以后设计者可以在设计中任意复用,并定义不同配置,同时CPU(NIOS Ⅱ)通过AVALON总线标准信号对其访问,具体访问细节用户可以不用关心,用户只要在编写完设备驱动函数后,在上层应用程序中直接调用驱动里定义的库函数即可完成对组件的操作[8]。

图3 片内步进电机IP控制器硬件设计Fig.3 Illustration of the design of hardwares of the on-chip IP controller core for a stepping motor

硬件的实现是用Verilog HDL硬件描述语言来实现。采用自顶向下的设计方法实现。自顶向下设计是从系统级开始,把系统划分为若干个基本单元,然后把每个基本单元再划分为更低层次的基本单元,这样一直划分到可以直接用EDA元件库中的基本元件实现为止[8-9]。

步进电机控制器模块的具体划分如图4。各个模块对应的文件及其关系如图5。

图4 步进电机IP控制器模块结构示意图Fig.4 Modules of IP controller core for a stepping motor

图5 步进电机控制器硬件文件Fig.5 Files for the hardwares of a controller of stepping motor

文件motor_driver_avalon_interface.v描述了步进电机控制器的顶层模块,此文件定义了2个底层模块的信号连接方式,还有要传递给底层模块的参数。文件motor_driver_regs_2.v定义了步进电机控制器内部的寄存器模块,此文件实现软硬件的接口。文件motor_driver_core.v实现步进电机控制器的核心控制逻辑,主要是输出步进电机控制信号和设定信号,并返回步进电机运行状态。

完成步进电机控制器的IP后,在SOPC Builder里实例化9个步进电机控制器,编译生成CPU模块。然后在QUARTUSⅡ里调用已经编译好的模块,正确连接CPU外围电路,并进行引脚分配,最后进行全编译。将编译生成的.sof文件下载到开发板上,整个系统的硬件平台即设计完成。

3 光谱仪IP控制核的软件设计

整个软件程序的开发可以分为两部分,一是固化在FPGA里的程序的开发,这部分程序开发的环境是NIOSⅡIDE开发集成环境;还有一部分是控制计算机(本地)上的控制主程序,采用VC++6.0开发环境开发[10]。

需要固化在FPGA里的程序也可以分为两部分,一是步进电机控制器的设备驱动程序,这部分程序放在系统库里,编译时就加入工程;还有一部分是通信控制子程序和多个电机协调调度的子程序,这部分程序放在开发板上的FLASH里,系统一通电,CPU就从FLASH里的指定地址处载入程序,开始执行。这两部分程序开发都基于NIOSⅡ的HAL系统库。

步进电机的驱动程序实现与硬件的接口,包括3个文件,分别是altera_avalon_motor_driver_regs.h、altera_avalon_motor_driver_routines.h和altera_avalon_motor_driver_routines.c,altera_avalon_motor_driver_regs.h文件是寄存器映像文件,定义了读写寄存器的宏和一些寄存器相关的参数值,这个文件是唯一的接口。altera_avalon_motor_driver_routines.h是为用户应用程序提供的设备头文件,用户要使用控制器这个IP,必须先把这个头文件包括进来。这个文件声明了供上层程序调用的电机控制函数以及和电机有关的参数。altera_avalon_motor_driver_routines.c提供了电机控制器驱动函数的代码,即具体实现[1]。

编写好步进电机控制器驱动函数以后,在SOPC Builder里将软件文件集成到步进电机控制器IP,在编译时,NIOSⅡIDE自动将库中的控制器驱动函数加入编译。这样就将整个底层和硬件相关的细节封装了起来,用户只需要关心上层的程序实现,而不必关心底层硬件如何组织,大大方便了应用程序开发者。

4 仿真和实验分析

4.1 仿真结果和实际信号观测

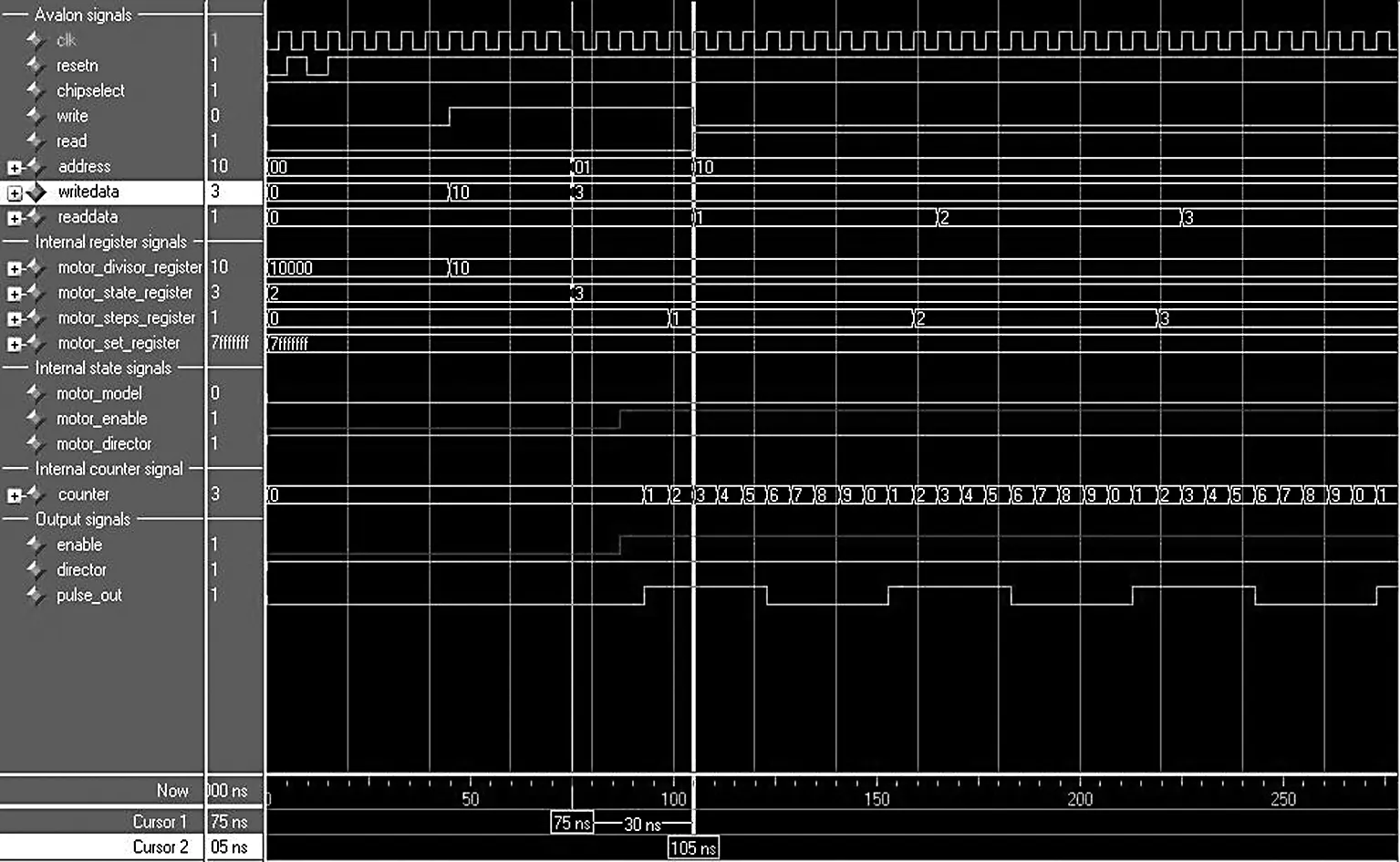

仿真环境采用Modelsim 6.1f,仿真步长1ns,仿真精度1ns,仿真时间设为20μs,系统时钟周期为6ns。

从仿真波形(图6)可以看出,在系统复位之后,寄存器中写入默认值,默认电机正转,运行在连续模式下,电机频率为系统时钟频率/10000,设定步长寄存器的值为0x7fffffff;书写有效,写入分频系数10(address=00,writedata=10),此时电机频率是系统时钟频率/10;在75ns时设置电机运转方向为正转,电机输出脉冲使能;在105ns的时候设置读取有效,可以看到电机步数开始送到读数据总线上。

从仿真和实际观察的信号波形可以看出,步进电机控制器IP完全达到了设计要求,时序正确,可以应用于接下来的设计。

图6 0~250ns之间的运行在设定模式下的步进电机控制器的仿真Fig.6 Simulation of the running of the controller of the stepping motor within 0 ns to 250 ns under a set mode

4.2 电机控制器驱动函数一点说明

无论电机运行在什么模式下,电机正转时,一旦到达设定步数(设定模式下等于设定步数,连续模式下等于0x7fffffff),电机控制器就停止发出脉冲,并且只有把方向设定为反转或是重置后才能重新启动电机。同样当电机反转时,步数为0时,电机即停止,直到方向设为正转或是重置后才能重新启动。这样是为了保护步进电机,避免步进电机在走到设定步数或是回到零位后还发生不希望的动作。在编写使步进电机发生点动的操作的时候,要注意这一点。

电机当前运行步数是对某一个原始位置(一般是电机初始位置)的绝对位移,而不是实际步数的累加。

5 LAMOST光谱仪IP控制核的应用,设计指标及控制目标

所设计的IP控制核主要用于控制多个步进电机,同时多个步进电机之间必须协调动作,满足一定的时序关系。具体要求如下:

(1)狭缝切换电机和CCD快门控制电机接到相应的命令则发生动作。

(2)Hartman快门1电机必须先开后关。即开启时Hartman快门1开,然后Hartman快门2开;关闭时Hartman快门2先关,然后Hartman快门1再关闭。

(3)电动调焦电机除了正反转控制以外,还要实现点动和预设步数操作。

(4)红蓝两区的切换和转动装置中的每个电机都有“小”、“大”两个位置。红区光栅切换电机处于“小”位置时,红区照相机转动装置才能动作;蓝区光栅切换装置处于“大”位置时,蓝区照相机切换装置才能动作。

此程序编译下载到开发板上的FLASH里,系统一通电就自动运行,根据通信端口传递来的控制信号和外接IO口的状态,安排各个步进电机按正确的时序动作[1]。

设计过程中具体的指标以及要达到的目标:由于光谱仪各部件的定位过程,是一种逐步逼近目标位置的调整过程,要求在目标位置处定位精度高,能够断电自锁, 而对调整过程中的平稳性、快速性没有严格要求,考虑到器件选择的方便性,本方案拟采用步进电机做执行部件,部分有特别要求的地方选用了力矩电机[5]。其中电动调焦装置控制指标:定位精度±0.02mm,采用丝杆传动,如果螺距2mm,理论计算整步1.8°的步进电机就能达到0.01mm分辨率,再选用细分步进电机驱动器驱动电机工作。新方案加装光栅尺,实行闭环控制。光栅平移(两套)控制指标:每个光栅台上装有两块不同分辨率的光栅,其中高分辨率光栅采用平移方式切换,定位精度在5丝,可以用霍尔元件检测[1]。

目前,16台装有IP核的光谱仪实时控制器其已经全部安装在国家天文台兴隆观测站的LAMOST上。多次的观测测试充分证明了对光谱仪的控制效果稳定,可靠。对所获得光谱的分析达到了预期的精度。整个装置于2008年10月通过了国家重大科学工程验收组的验收。

6 总结和展望

本文初步探讨了SOPC技术在天文仪器设计与控制中的应用,尝试使用NIOSⅡ软核技术设计了LAMOST中的低分辨光谱仪IP控制核。重点研究了步进电机控制器IP的封装,并基于ALTERA的FPGA,实现了多个步进电机的控制,成功实现了软件的固化,并完成了串口控制的设计,研究了以太网控制的实现。采用控制器IP复用技术,大大缩断了设计时间。

由于时间较紧,还有很多后续工作没有展开,如何更好的在HAL系统库中使用以太网进行控制;怎样进一步裁剪系统以节约资源,而不是使用通用性较强的开发板;如何在更复杂的控制设计中利用FPGA和SOPC的优势,如何更高效地使用软核;这些问题,都可以进一步研究探讨。

[1]朱永田,王磊,胡中文,等.LAMOST低分辨率光谱仪VPHG方案[R].2005.

[2]朱永田,王磊,胡中文,等.LAMOST低色散光谱仪的科学要求[R].LAMOST-TR-SCI,2000-001.

[3]朱永田,王磊,胡中文,等.LAMOST低分辨率光谱仪多种方案分析[R].LAMOST-TR-NAIRC,2000-L6-002.

[4]朱永田,王磊,胡中文,等.LAMOST低分辨率光谱仪初步设计修改过程[R].LAMOST-TR-NAIRC,2001-L6-007.

[5]朱永田,王磊,胡中文,等.LAMOST低分辨率光谱仪初步设计修改过程[R].LAMOST-TR-NAIRC,2002-L6-007.

[6]朱永田,王磊,胡中文,等.LAMOST低分辨率光谱仪(初步设计修订)[R].LAMOST-TR-NAIRC, 2002-L6-001.

[7]任爱锋,初秀琴,常存,等.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004.

[8]王诚,吴继华,范丽珍,等.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005.

[9]吴继华,王诚.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005.

[10]李洪伟,袁斯华.基于Quartus Ⅱ的FPGA/CPLD设计[M].北京:电子工业出版社,2006.