ARM在LED显示控制系统中的应用与设计

王丽萍 周珍艮

(光电子应用安徽省工程技术研究中心,安徽 铜陵 244000)

ARM在LED显示控制系统中的应用与设计

王丽萍 周珍艮

(光电子应用安徽省工程技术研究中心,安徽 铜陵 244000)

基于ARM(S3C44B0)嵌入式处理器提出一种采用CPLD技术开发LED显示控制系统的设计。应用CPLD实现ARM(S3C44B0)中LCD与LED显示系统的转接,使LED具有强大的数据处理和实时显示功能。文章重点讨论了控制系统的软硬件和逻辑设计的设计方案,在实际应用中具有一定的参考价值。

LED控制系统;ARM;CPLD;LED

近年来,LED显示系统在信息显示领域得到了广泛的应用。北京奥运会、上海世博会上LED彩屏风采尽显;大型歌舞晚会LED背景墙以其色彩鲜艳、动态逼真,给予人们视觉享受无限;LED电视也即将进入百姓家庭,形成具有相当发展潜力的新型光电子产业。

LED显示技术涵盖了微机控制、视频、光学、机械和数字图像处理等多种技术,是计算机技术与信息处理技术相结合的综合电子信息技术。LED彩屏特别是视频显示系统要实现系统图像快速显示,需要对红、绿、蓝LED进行灰度调节。如果三色都能实现8位灰度可调,就可以形成256*256*256共168万种颜色。控制LED的灰度主要是采用占空比法,将显示一帧的时间分为8个不相等时间长度子帧,8位共有256个灰度等级。如此复杂的时序逻辑功能和庞大地、高速的数据处理,只能由大规模集成电路来实现,使用ARM+CPLD技术,能够完成LED显示系统的数据传输控制、灰度控制,系统控制等系统功能,设计开发难度不大,产品应用灵活性较强。

一、LED显示控制系统工作原理

数据的采集和处理利用专门的模块来完成,把它与显示控制模块分开,不使用CPLD来完成这个部分的工作。因为网络的应用已经有比较成熟的技术和器件,利用Intemet网络传输数据可以很好地解决数据的传输问题。不必要再花费专门的时间开发数据的采集和传输控制模块,这对于缩短产品开发周期是极其有利的。

图1工作原理框图

图1是系统工作原理框图。整个控制系统是以ARM微处理器为核心的一个小型计算机结构[1]。该控制系统采用大容量闪速存储器和通信模块实现数据的存储和更新,并在控制上配备CPLD来分担ARM微处理器的压力,以达到全彩LED显示屏的高灰度级、高复杂性特技和高速度、大容量数据传输的显示要求。

二、基于S3C44B0(ARM7TDMI)的LED显示系统的硬件设计

1.设计目标:本文研究的主要目标是实现小型的、可脱机播放的彩色视频系统,根据LED显示屏的工作原理以及视频系统的主要功能和技术指标,归纳出以下主要几点:

(1)LED显示屏的分辨率:128行x256列

(2)LED显示屏的刷新率:7OHz

(3)实现灰度显示,灰度级为256级

(4)LED 显示屏的基色:R(红)、G(绿)、B(蓝)

(5)系统控制器必须支持一般显示屏所需的与上位机实时通讯和全部显示功能。

2.系统的主要硬件设计

图2主要硬件设计

(1)嵌入式微处理器的选择

本系统选用的S3C44B0是基于ARM公司ARM7TDMI内核、0.25μmCOMS标准单元和存储器开发的16/32位RISC处理器,一般应用于提供高性价比和高性能的微控制器解决方案。S3C44B0X内含部件:8KB Cache、可选的内部SRAM、LCD控制器、2通道UART、4通道DMA、系统管理器(芯片选择逻辑、FP/EDO/SDRAM控制器)、6通道带PWM的定I/O口、RTC、8通道12位ADC、I2C/I2S总线接口SIO接口和成对时钟PLL。

针对全彩LED显示屏的各种功能需要,在本控制系统中扩展了 FLASH、SDRAM、8021 以太网卡、CF 卡、UART、JTAG调试接口、自动亮度控制等模块,

在本系统中,充分利用了功能强大的S3C44B0X的内置LCD控制器,使用其256色双行扫描模式,大大提升了系统的运行效率.。但是S3C44B0的LCD控制器输出无法与LED屏幕控制器直接接口,因此,系统中使用CPLD作了LCD到LED的转换。S3C44B0的GPIO口内部编码以连接红外接收器,解析各种命令、温度和时间是LED屏幕经常包含的内容。选用DS18B20温度传感器采集温度,并充分利用S3C44B0的内部实时时钟(RTC),减少了系统成本。系统运行于60M主频,程序存储器选用16M byte FLASH 28F128芯片,同时在FLASH中保存系统设显示的内容以及设置参数等;Boot程序被应用程序搬移到SDRAM区域运行大大提高了系统运行速度

(2)JTAG测试接口

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试。JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(TestAccess Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。通过JTAG接口,可对芯片内部的所有部件进行访问,JTAG接口还常用于实现在系统编程功能,如对FLASH器件进行编程等。S3C44B0专用ICE引脚TDI、TDO、TCK、和TMS实现了ARM7TDMI的ICE接口,为目标板仿真提供了一个完全的、低成本的调试方案。

(3)数据通信TCP/PI协议的获取

利用嵌入式微处理器作为Intemet通讯的终端。嵌入式微处理器控制功能强大,可以运行嵌入式操作系统,实现TCP/IP,因此能够很容易地实现Intemet数据通信。

市场上有很多的TCP/IP协议栈可供选择,本系统选用lwIP,它结构清楚,占用存储器空间小,这对于存储资源比较紧张的微处理器来说是很有利的。

三、CPLD的选择与应用

本系统的CPLD选择了XC9572实现显示数据的仲裁和扫描控制[2]。它具有很好的组合逻辑和时序逻辑功能,能够完成LED显示所需要的扫描控制信号。CPLD设计框图如图3所示,它主要包括以下几个模块:⑴时钟进程:产生各种频率的时钟;⑵FIFO:CPLD与MCU之间的接口部分,用作数据缓冲,它使得MCU可以对显存进行全速写操作;⑶写入地址及数据产生器:产生向显存进行写操作的地址和数据;⑷读地址产生器:扫描方式不同,从显存中读取数据时的寻址方式也不同,读地址产生器,可根据扫描方式的不同,产生不同的读显存的地址,从而完成1/16.1/8.1/4等扫描方式;⑸扫描控制电路:在不同的扫描方式下,根据从显存中读取的数据。产生相应的扫描控制信号;⑹读写切换电路:对显存的读写状态进行切换。

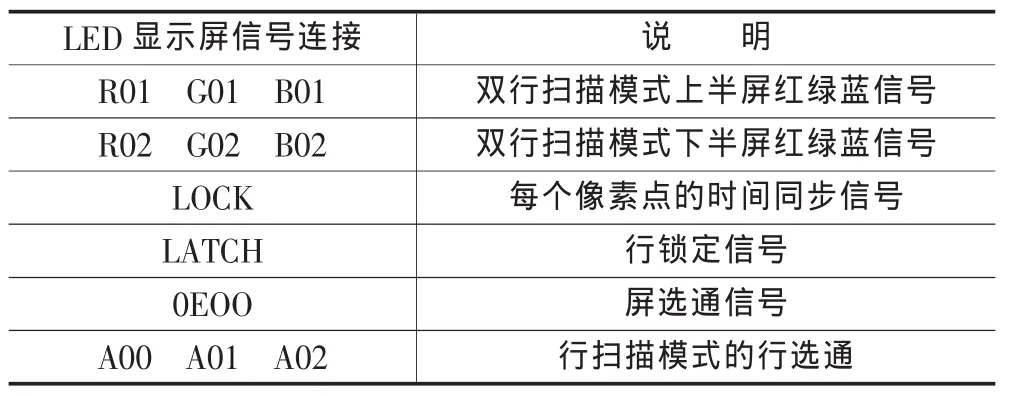

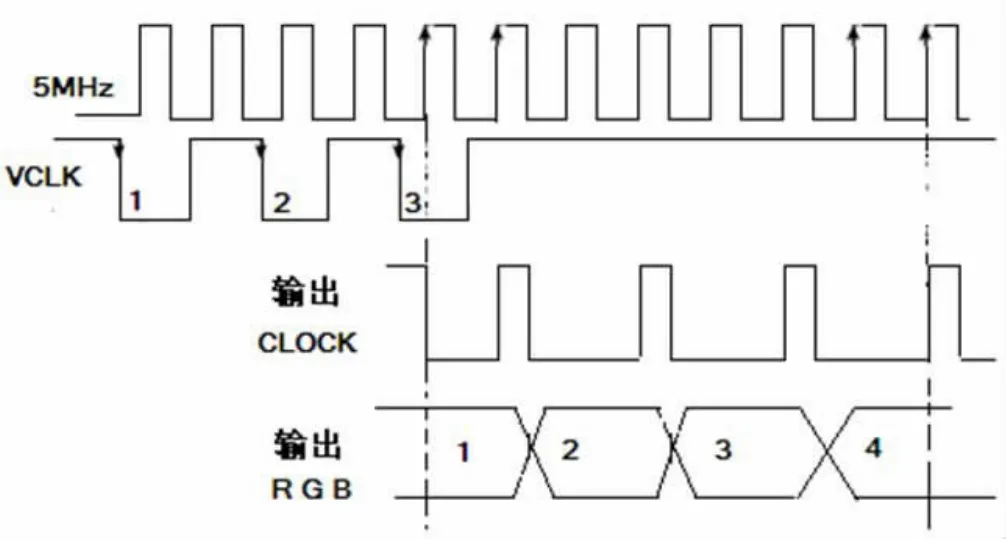

LED显示屏的控制信号的连接如表1。在逻辑设计上,OE信号由S3C44B0的GPIO直接控制屏幕的亮和灭;;LATCH信号和A00、A01、A02由VILINE信号和VFRAME信号来控制产生(VFRAME用作同步A00、A01、A02到0);这里主要是RGB信号的产生。如果S3C44B0的4位双行扫描工作于256颜色模式,每3个VCLK产生的数据为D3D2D1(R1G1B1)、D0D3D2(R2G2B2)、D1D0D3(R3G3B3)、D2D1D0(R4G4B4),代表4个像素的RGB信息。因此,CPLD采样时钟选用25MHz,每采样3组VCLK,输出4组RGB信息,完成了从LCD到LED的转换。图3给出了由LCD到LED的时序逻辑图。

表1 LED显示屏控制信号接口

图3 LCD到LED转接的时序逻辑图

四、嵌入式操作系统的选择

uC/OS一11作为操作系统的内核,编写应用程序比较简单,主要的任务是完成多任务之间的调度和同步,并为设备驱动和系统服务程序提供信号量、消息队列的服务[3]。因为内核需要实现时间延时和确认超时,所以还需要时钟节拍(Tme Tikc)中断服务程序为其服务。

本系统划分的任务包括:灰度显示、JPEG解码、亮度控制、显示模块、时间/日期定时显示、消息响应事件等任务。编写好这些任务的代码(包括系统服务的调用)和用到的中断服务程序后,启动操作系统则应用程序就开始运行。若要增添功能,只需增加相应任务和调用一定的系统服务即可。

五、结论

采用高性能的32位ARM微处理器替代传统的单片机,在uC/OS-Ⅱ嵌入式实时操作系统高效的多任务管理下设计的全彩LED显示屏控制系统,具有更强大的功能和实时处理能力。采用基于ARM(S3C44B0)的LED显示技术在实际工程应用和产品设计中具有一定的参考价值。

[1]张玉杰,马立云,张贺艳.基于RAM和FPGA的LED显示屏系统的设计[J].计算机测量与控制,2009,17(12):2429-2431.

[2]黄毅,朱为.基于CPLD的LED显示屏异步控制系统设计[J].电子器件,2007,(1): 143-146.

[3]GE Xin, MENG Fanrong.UsingμCGUI to Develop Graphical User Interface[J].ComputerEngineering andDesign,2005,26(1):253-255.

TP368

A

1672-0547(2010)04-0062-02

2010-06-20

王丽萍(1965-),女,安徽南陵人,光电子应用安徽省工程技术研究中心副教授,研究方向:电子信息处理。

安徽省教育厅自然科学研究重点项目《ARM及其嵌入式系统在LED显示控制系统中的设计应用研究》成果(编号:KJ2008A27ZC)。