基于AD9956的任意频率合成器研制

樊战友,樊西青,2,张首刚,3

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院研究生院,北京 100039;3. 中国科学院时间频率基准重点实验室,西安 710600)

基于AD9956的任意频率合成器研制

樊战友1,樊西青1,2,张首刚1,3

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院研究生院,北京 100039;3. 中国科学院时间频率基准重点实验室,西安 710600)

为满足精密时间测量和高性能星载原子钟等国家重要研究课题的实验应用需求,研制了主要由AD9956芯片和8位高性能单片机构成的一种DDS(直接数字合成)任意频率合成器。在分析DDS的基本原理和特点的基础上,从硬、软件等方面较为详细地介绍了该频率合成器的设计,对同时完成的专用于控制该合成器工作的计算机应用软件也作了介绍。实际使用结果表明:研制的合成器符合实验使用要求,并对促进课题的研究完成发挥了积极作用。

直接数字合成(DDS);频率合成;频率(或相位)控制分辨率

直接数字合成(direct digital synthesis,DDS)是利用数字技术产生模拟波形信号(通常是正弦波形)的一种方法和技术。它将先进的数据处理理论与方法引入频率合成领域,是继直接频率合成(DS)和间接频率合成(IS)之后的第三代频率合成技术[1]。DDS的基本原理是:通过D/A变换将具有一定规律(通常是正弦函数)产生的随时间连续变化的数字信号转换为相应的模拟波形信号。获得随时间连续变化的数字信号的方法有查表法和寄存器法。为了保证或改善产生的模拟波形信号的技术指标,通常还要采取滤波、光滑等一些处理措施[2-3]。

DDS的主要优点是:

1)极低的相位噪声(优于-144 dBc/Hz)和时钟抖动(<1 ps)。这是DDS最关键的性能优势。

2)很高的频率、相位控制分辨率。频率分辨率可达10-6Hz,相位分辨率可达0.02°。

3)输出频率或相位转换快速准确。转换时间通常在ns量级。由于没有跟踪或锁定过程,不会出现输出频率过头或不足的情况。

4)数字控制接口结构,能够与计算机紧密结合和充分发挥软件灵活、方便的控制功能和作用,可用于频率和相位的远距离控制。

5)数字结构技术克服了由于器件老化或温度改变引起的工作参数漂移,免除了手动调节和调试。

6)低成本、高性能、多功能、高集成度。

随着设计和处理工艺的进步,DDS芯片在性能、功能、功耗和集成度等方面的优势变得愈益突出和明显。DDS芯片和技术在时频、测控、通信、医疗、工业等多项技术领域得到了日益广泛的应用。

高精度、高稳定、低相噪的频率基准是开展高精度时间测量与研究的前提,也是航空航天、国防建设等高技术领域的基本要求。采用DDS频率合成技术和计算机控制技术,将原子内在稳定的高频跃迁信号转化为稳定的频率(原子钟)信号输出,是得到高性能频率基准的一种很好的选择和方法[4-5]。

本文介绍一种已研制完成并主要应用于某量子频标研究室原子钟研制实验中的任意频率合成器。该任意频率合成器是DDS技术和计算机控制技术相结合的结果,具有功能强、技术指标较高、使用方便、体积小等特点。作为频率基准,它除了具有高精度、高稳定度、低相噪的特点外,其突出优点是输出频率可以在很大范围内设置和调整。

1 任意频率合成器设计要求

对该任意频率合成器的设计要求主要是:

1)性能方面[6-7]:

输入:0 dBm(可调)400 MHz正弦信号;相位噪声@1 Hz<-80 dBc,@10 Hz <-100 dBc。

输出:相位噪声@10 Hz <-130 dBc;输出频率分辨率不低于1μHz,相位分辨率不低于0.1°。

2)功能方面:

PC计算机或单片机可通过RS232接口设置和控制任意频率合成器的输出频率、相位和工作模式。

2 任意频率合成器硬件设计

2.1 DDS芯片选择

合理选择DDS芯片是使用DDS技术实现任意频率合成的关键之一。选片的主要根据是对频率合成器性能和功能的具体应用要求和使用条件,同时也要兼顾成本、与DDS之外其他单元的接口等诸多因素。

技术成熟的DDS芯片很多,如Qualcomm公司的Q2220、Q2230、Q2334、Q2240、Q2368,其中Q2368的时钟频率为130 MHz,分辨率为0.03 Hz,杂散控制为-76 dBc,变频时间为0.1μ s,还有美国AD公司的AD9850、AD9851、AD9852、AD9956等。AD公司的器件价格较高,但性能稳定可靠,有很好的信誉,其中AD9956的主要技术指标为:400 MSPS内部DDS时钟,48-bit频率调谐字,14-bit可编程相位偏移量,内部集成有14-bit数模转换器,相位噪声≤135 dBc/Hz@1 kHz频偏,相位噪声@100 Hz<-126 dBc/Hz,相位噪声@10 Hz<-115 dBc/Hz,IOUT输出口处的无杂散动态范围(SFDR):-80 dB 160 MHz@(±100 kHz偏离),25 Mb/s串口I/O写控制速度,655 MHz可编程相位频率检测输入除法器(÷M,÷N){M,N = 1,…,16}(可旁路),内核1.8 V供电,I/O和电荷泵3.3 V供电。没有输入信号倍频器。

综合考虑后,我们选择了AD9956[8]。图1是AD9956功能框图。

图1 DDS芯片AD9956功能框图

2.2 硬件框图和工作原理

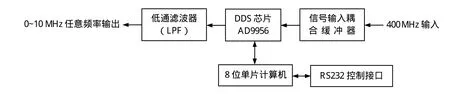

图2是任意频率合成器的硬件设计框图[9]。400 MHz的频率基准通过信号输入耦合缓冲器,经共轭参考时钟REFCLK(28、29脚)进入AD9956。信号输入耦合缓冲器的作用一方面是隔离AD9956和信号源的直接连接以改变频率合成效果,另一方面是防止过高的信号电压烧坏AD9956。合成的模拟频率信号经AD9956共轭电流口IOUT(5、6脚)输出后,再经低通滤波器(LPF)输出。低通滤波器的作用是进一步改善合成的模拟频率信号的技术指标,尽管AD9956输出的指标本来就已经很高。8位单片机的作用是通过串口(SDI/O、SCLK、CS)和其他控制线(PS0、PS1、PS2、I/O_RESET)设置AD9956的工作参数和运行方式。RS232控制接口提供单片计算机与外部的交互通道。任何具有RS232接口的设备,如计算机、带显示和键盘的单片机系统等,都可以通过此接口控制任意频率合成器的运行。

图2 任意频率合成器硬件设计框图

3 C51软件设计

频率合成器的输出频率表达式为

式(1)中的FTW为频率调整字(代表FTW 0~FTW 7中的任何一个),6字节长,0≤FTW≤247,存在片内寄存器中。共有FTW 0~FTW 7 8个频率调整字,这8个频率调整字内可写入不同的数值。通过PS0、PS1、PS2三个引脚可选择8个频率调整字中的任意一个作为工作FTW。式(1)中的fs为DDS内部时钟频率,最大值为400 MHz。由图1可知:fs值由从共轭REFCLK输入的频率基准和RF除数因子共同决定。单片机的主要任务是控制输出合成频率值。此外,单片机还负责选择DDS的工作模式、输出相位控制、与其他系统的同步控制、锁相控制、电荷泵控制、通过串行口与外部通信等。单片机软件采用C51语言设计。图3是单片机的C51软件流程图。

AD9956有单调、一般线性扫描和线性扫描无驻留等3种工作模式。初始化状态如下:选择单调模式,工作寄存器选8个频率调整字组(图3中的FTW代表寄存器组FTW 0~FTW 7)中的FTW 0,RF除数因子R=1,FTW 0值=10×248/400,频率源fs= 400 MHz。由(1)式可知:输出频率=10 MHz。

串行口初始化为:串口=1,波特率=9 600 bps,数据位=8,校验=无,停止位=1。

图3 单片机C51软件流程图

4 通信协议和应用程序设计

4.1 通信协议

通信协议指频率合成器和PC机的串口之间的通信协议。计算机通过RS232串口可以控制频率合成器的运行和了解频率合成器工作状态。串口通信协议为:计算机发送的数据格式为:[#];[,];

当频率合成器收到来自RS232串口的“读”指令后,作为响应,会从串口给计算机发送数据。发送的数据格式为:[#];[,];

4.2 应用软件设计

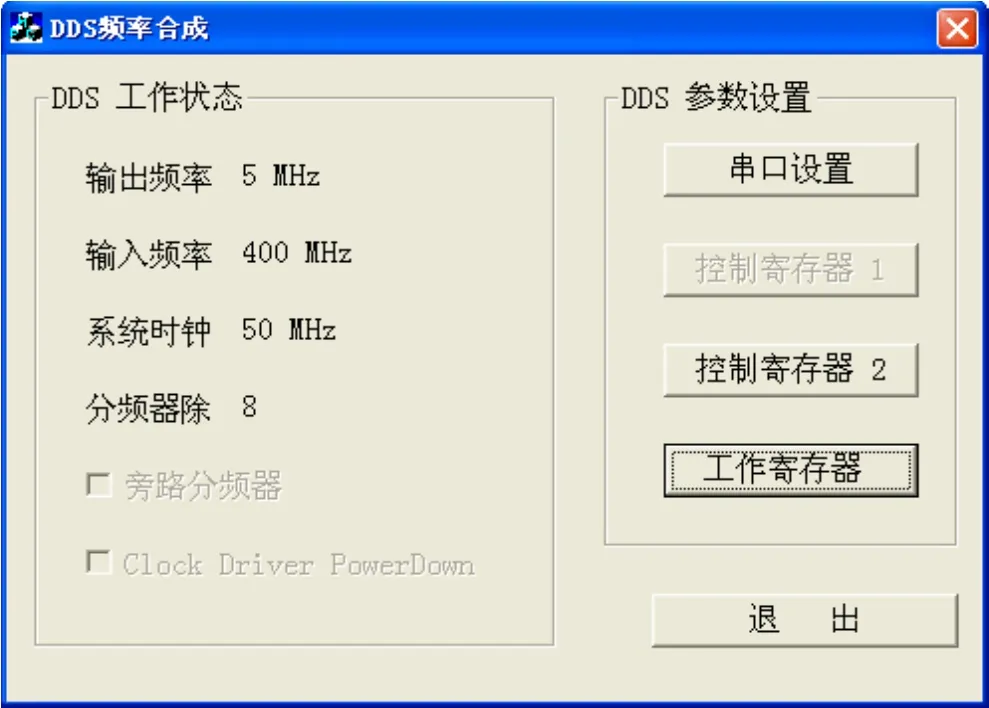

为了充分利用计算机软、硬件资源,便于频率合成器的使用,我们在Windows XP平台下,采用VC 6.0语言设计了界面友好、操作快捷、控制可靠的任意频率合成器的专用控制软件。

软件基于基本对话框设计,具有关于框符、3D控制、ActiveX控件、共享DLL等支持。图4为软件启动界面。该软件包含串口设置、控制寄存器1、控制寄存器2和工作寄存器等4个对话框,以完成不同控制和参数设置,并显示工作状态。图5是控制寄存器2的对话框界面。

图4 频率合成器软件启动界面

图5 控制寄存器2的对话框界面

5 研制结果和结论

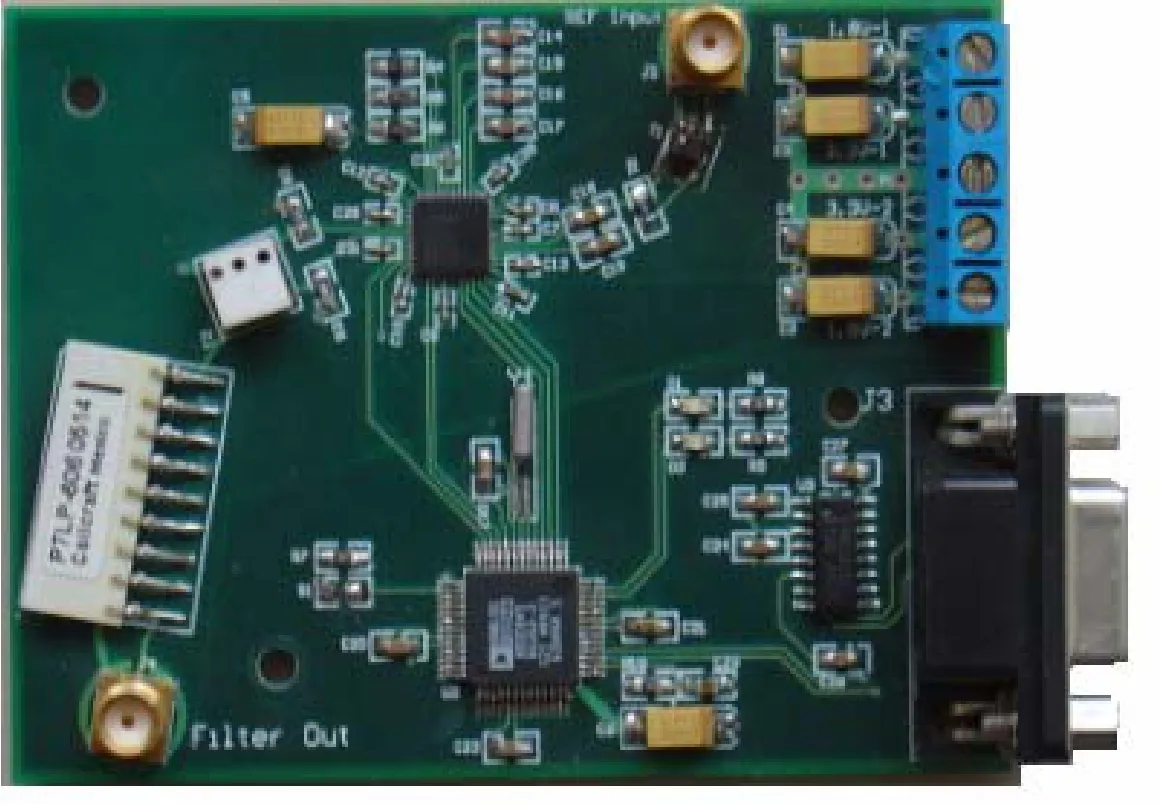

图6是研制的任意频率合成器的实物图。该合成器采用4层电路板设计。工作电源为直流3.3 V和1.8 V,总功耗低于1 W;输入频率范围为0~2 700 MHz,输出频率范围为0~10 MHz;相位噪声<-80 dBc @1 Hz。

图6 研制的任意频率合成器的实物图

使用DDS技术研制的合成器输出频率信号有很高的相位噪声特性。图7是输入频率400 MHz、输出频率10 MHz时的波形图,输出波形十分干净光滑。

图7 合成器输出频率为10 MHz的波形图

该频率合成器还有以下特点:

1)输出频率范围较宽、分辨率很高:如果不考虑低通滤波器,输出频率范围为0~200 MHz,分辨率最高为10-6Hz。

2)操作简单、功能强:使用专用的计算机软件,可以十分便捷地设置合成器的工作方式、输出信号的频率、相位和幅度,甚至可以使输出信号的频率按预计的波形或规律变化,这对雷达、跳频通信系统很有用。

3)集成度高、能耗低、整体成本也较低。

研制的该任意频率合成器,已实际应用于一国家重点预先研究项目。该合成器的功能和技术指标完全满足要求,为项目的顺利完成发挥了不可替代的作用。

该合成器在精密时间测量研究和实验中也发挥了积极作用。

[1] 秦蕾, 高伟, 陈智勇, 等. 一种铷原子频标射频倍频单元的实现[J]. 时间频率学报, 2009, 32(1): 6-11.

[2] 王丹妮, 陈淑芳, 边玉敬. 一个甚高频频率合成器的设计[J]. 陕西天文台台刊, 1996, 19: 105-107.

[3] TIERNEY J, RADER C M, GOLD B. A Digital Frequency Synthesizer[J]. IEEE Transaction on Audio and Electroacoustics, 1971, 19(1): 48-57.

[4] 周渭, 王海. 时频测控技术的发展[J]. 时间频率学报, 2003, 26(2): 87-95.

[5] ZHOU Wei, LI Zhi-yong, ZHOU Hui. A Practical Method to Process Time and Frequency Signal[J]. IEEE Transactions on UFFC, 2000, 47(2): 480-483.

[6] 田新广, 张尔扬, 邬书跃. DDS幅度量化杂散信号的频谱研究[J]. 通信学报, 2003, 24(7): 79-85.

[7] 王永, 刘志强, 刘硕. DDS在任意波形发生器中的应用[J]. 仪表技术, 2001, 4: 22-23, 33.

[8] Analog Devices Inc. 2.7 GHz DDS-Based Agile RFTM Synthesizer[K]. [S.l.]: Analog Devices Inc, 2004.

[9] GRIFFITHS H D, BRADFORD W J. Digital Generation of Wideband FM Waveforms for Radar Altimeters[J]. IEEE International Conference Radar, Radar-87, 1987: 325-329.

A Random Frequency Synthesizer Developed Based on AD9956 Chip

FAN Zhan-you1, FAN Xi-qing1,2, ZHANG Shou-gang1,3

(1. National Time Service Center, Chinese Academy of Science, Xi’an 710600, China;

2. Graduate University of Chinese Academy of Science, Beijing 100039, China;

3. Key Laboratory of Time and Frequency Primary Standards, Chinese Academy of Sciences, Xi’an 710600, China)

In order to meet the needs of some important research projects such as precise time measurement and high-performance on-board atomic clocks, a DDS(direct digital synthesis) random frequency synthesizer, which is composed mainly of AD9956 chip and 8 bit high-performance SCM(single chip microprocessor), has been developed. Based on the analyses of the basic principles and characteristics of DDS, the authors made a detailed description of the design of the random frequency synthesizer in both of hardware and software in detail, and the authors also introduced a dedicated application software which is used for computer to control the synthesizer. The experiments show that the frequency synthesizer meets the requirements of the advanced researches and has played an active role in promoting the completion of research project.

DDS(direct digital synthesis); frequency synthesis; frequency (or phase) control resolution

TN74

A

1674-0637(2010)02-0108-07

2009-12-17

国家自然科学基金资助项目(10773012);国家自然科学基金重点课题资助项目(10834007)

樊战友,男,硕士,研究员,主要从事时频测控理论与技术方面的研究。