基于原理图输入的补码加法器设计

关键词:EDA;原理图输入;全加器;补码加法器;溢出

中图分类号:TP311 文献标识码:A

文章编号:1009-3044(2025)03-0046-03 开放科学(资源服务) 标识码(OSID) :

0引言

电子设计自动化EDA(Electronic Design Automa⁃tion) 是一种利用计算机辅助设计CAD(ComputerAided Design) 软件,来完成电子电路功能设计、综合、仿真验证等流程,完成PCB电路板设计验证,以及完成超大规模集成电路(VLSI) 芯片的功能设计、综合、验证、物理设计等流程的设计方式。依赖于计算机工作平台,以及各种电子设计软件工具,EDA技术极大地提高了设计效率。EDA技术用计算机平台及相应的工具软件,来进行设计模拟、仿真、检验、布图和测试,不但提高了设计效率,加快了设计进度,提高了设计的可靠性,而且在设计阶段就可以进行所有部件直至整个系统的仿真、测试、方案比较、参数优选,从而极大地提高了设计质量。从发展历程来看,因为早期计算机的运行速度慢,内存储器的存储容量很低,导致计算机的图形处理能力很低,因此这个阶段诞生了一些功能相对简单的CAD程序。这些早期的程序在电子电路逻辑功能设计、仿真、印刷电路板布局布线,以及集成电路版图设计等方面代替了设计人员的工作,提高了电子电路设计、系统设计,以及集成电路设计的效率。到了20世纪80到90年代,计算机技术、集成电路技术得到快速发展,计算机的运行速度加快,内存储器容量越来越大,图形处理能力进一步增强,各种CAD程序功能越来越强。这些CAD程序被逐渐集成,形成功能强大的EDA软件系统。这些软件采用图形界面,可以直接将电子电路原理图作为输入,对电路的功能进行仿真和模拟,并有自己的元件库,用户使用时,可以调用库中的元件进行电子电路的设计和绘图工作,进一步提高了设计效率[1]。

随着集成电路技术和计算机技术的发展,EDA技术得到了飞速发展。尤其是随着微电子技术的发展,用户对电子系统提出了更高的要求,包括多功能、高速度、智能化等方面的要求,而这些对集成电路的容量、速度都有着更高的要求。这些都要求EDA软件进一步演化升级,以满足日益高涨的设计要求。同时,随着集成度的提高,甚至可以把一个复杂的电子系统集成在一块芯片上实现,而这又要求EDA软件不仅能够描述电子系统的功能和行为,能够根据功能要求设计逻辑电路,还必须能够将设计的系统映射为集成电路版图,以便制造出系统芯片。这个阶段开始,EDA 系统真正具备了自动化设计能力,能够根据系统功能设计要求,设计出电子系统,对电路结构和参数进行处理和优化,并转化为集成电路芯片版图,从而制造出系统芯片。综上所述,EDA技术已经不是一个学科的分支,而是一门综合性学科[2]。

Quartus II是一个集成开发平台,采用可视化技术,并引入了标准的EDA工具接口,方便了硬件电路设计,提高了设计和仿真效率。在Quartus II平台进行EDA设计时,可以采用多种设计输入的方式,如原理图输入、硬件描述语言HDL(Hardware DescriptionLanguage) 文本输入,网表输入以及波形图输入等,提高了设计效率。硬件描述语言HDL是一种程序设计语言,主要用于描述数字电路和设计数字系统,描述数字电路的功能、信号连接关系,以及时序关系等。目前,比较常用的硬件描述语言主要有Verilog HDL 和VHDL(Very High Speed Integrated Circuit Hardware Description Language)两种[3]。

为了更好地理解和应用EDA 技术,本文利用Quartus II平台,采用原理图输入的方式,首先设计一个全加器,然后在此基础上设计实现三位补码加法器。

1 一位加法器设计

一位加法器分为半加器和全加器,半加器把两个一位二进制数相加,一个是被加数,另一个是加数,不考虑低一位邻位送来的进位[4]。

全加器把三个一位二进制数相加,一个是被加数,一个是加数,以及低一位邻位送来的进位。如果两个多位二进制数据相加,每一位都要考虑低一位邻位送来的进位,所以要构造多位加法器,一般采用全加器,不采用半加器。

以a表示被加数,b表示加数,ci表示低一位邻位送来的进位,so表示和,co表示向高一位邻位的进位。根据二进制数加法规则,可以列出全加器真值表如表1所示。

根据上述真值表,可以写出输出逻辑量的函数表达式:

so=a⊕b⊕ci,co=aamp;b+aamp;ci+bamp;ci

根据上述公式,在Quartus II平台画出全加器的原理图如图1所示。

仿真结果如图2所示。

2多位补码加法器设计及溢出判断

2.1多位补码加法器设计

由一位全加器构成多位加法器,采用串行进位的方式。补码在数字系统中,特别是计算机中应用广泛,现代计算机中都采用补码作加减法运算,而且通常把减法运算转化为加法。假设加法器的两个操作数,即被加数和加数都是补码,最高位是符号位,其余位是数值位。

无论是整数还是小数,都有下式:[5]

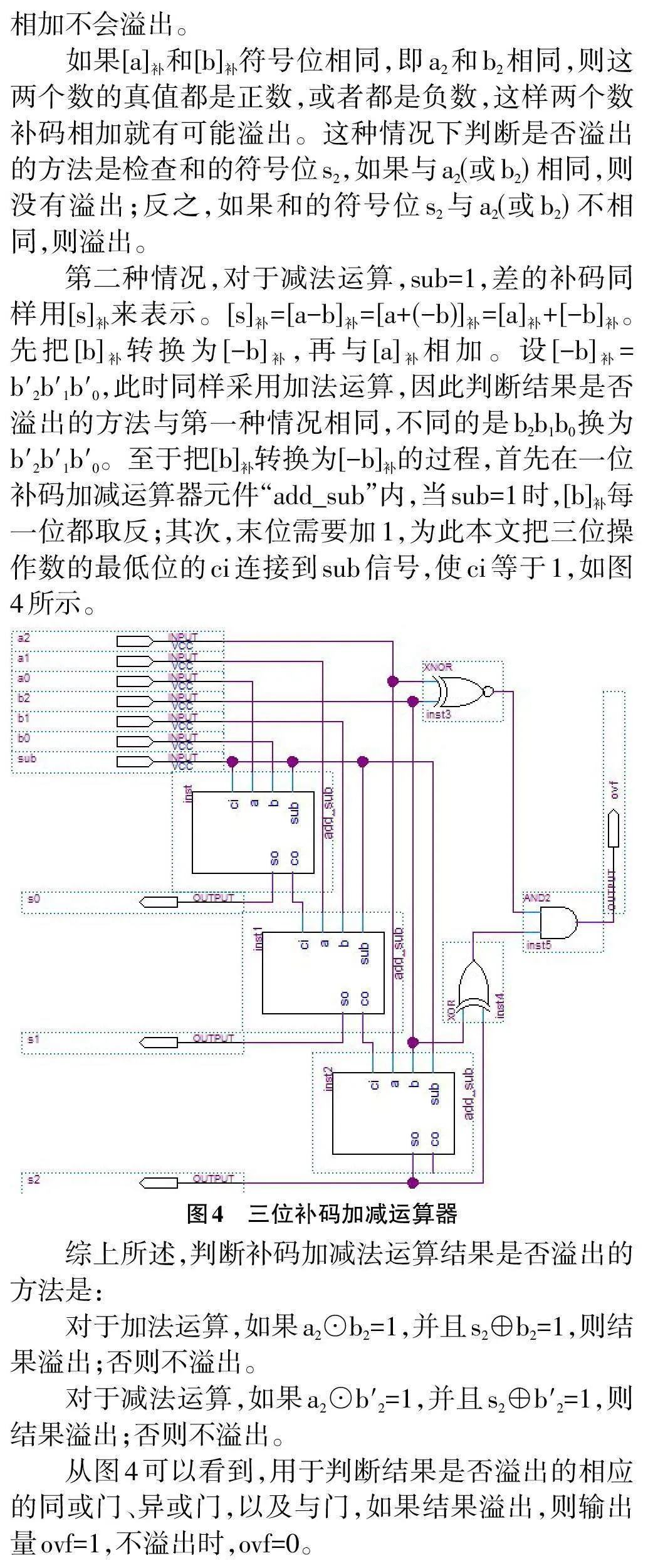

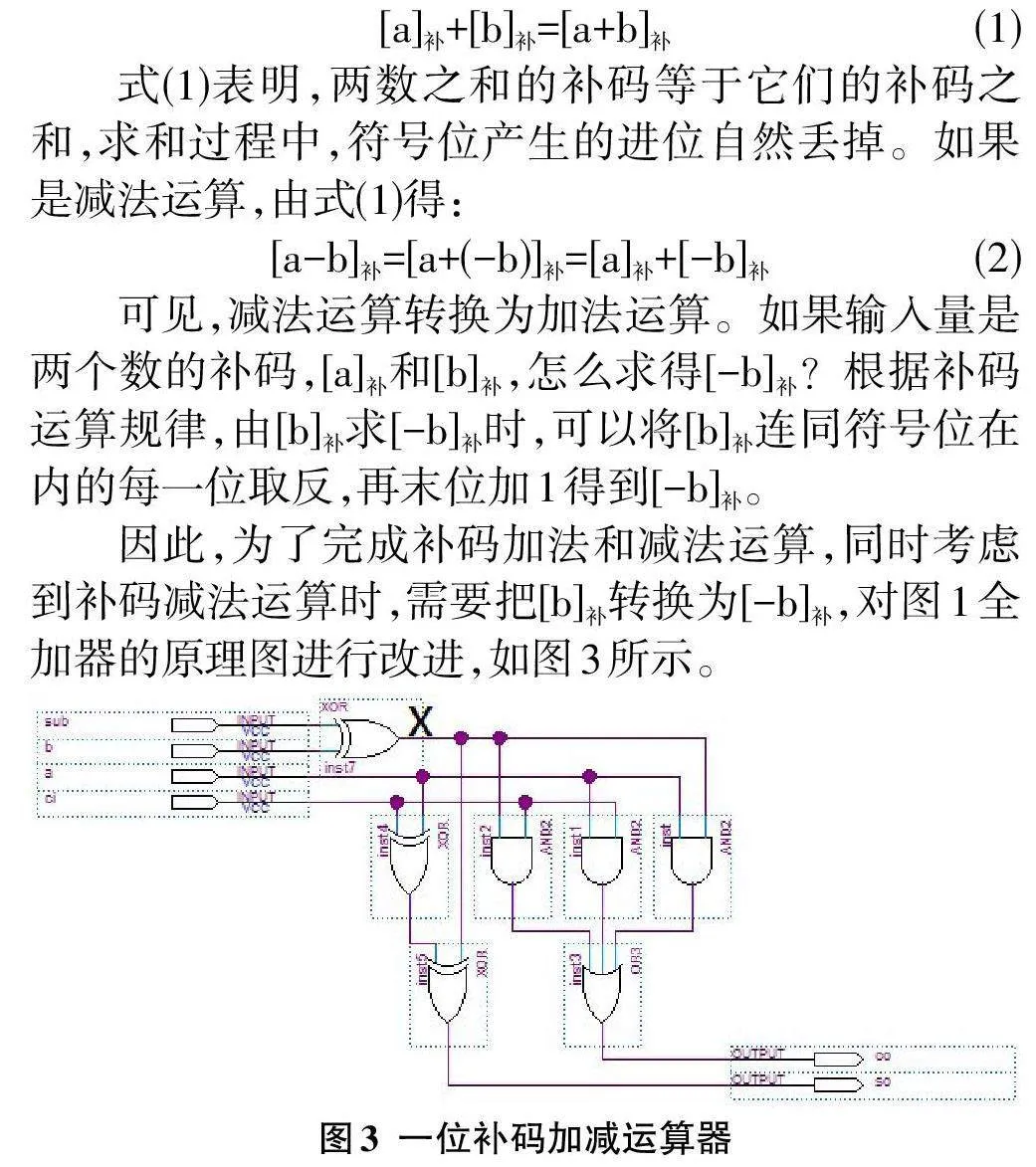

与图1相比,多了一个输入端“sub”,该输入量与加数b输入一个异或门,异或门输出x相当于图1的加数b,x=sub⊕b。

如果sub=0,则x=sub⊕b=0⊕b=b,此时完成加法运算。如果sub=1,则x=sub⊕b=1⊕b=/b(b取反),此时完成减法运算。选择菜单File→Create/Update→Cre⁃ate Symbol Files for Current File,将这个一位补码加减运算器生成为一个元件符号“add_sub”,供下面的设计调用。

3仿真结果

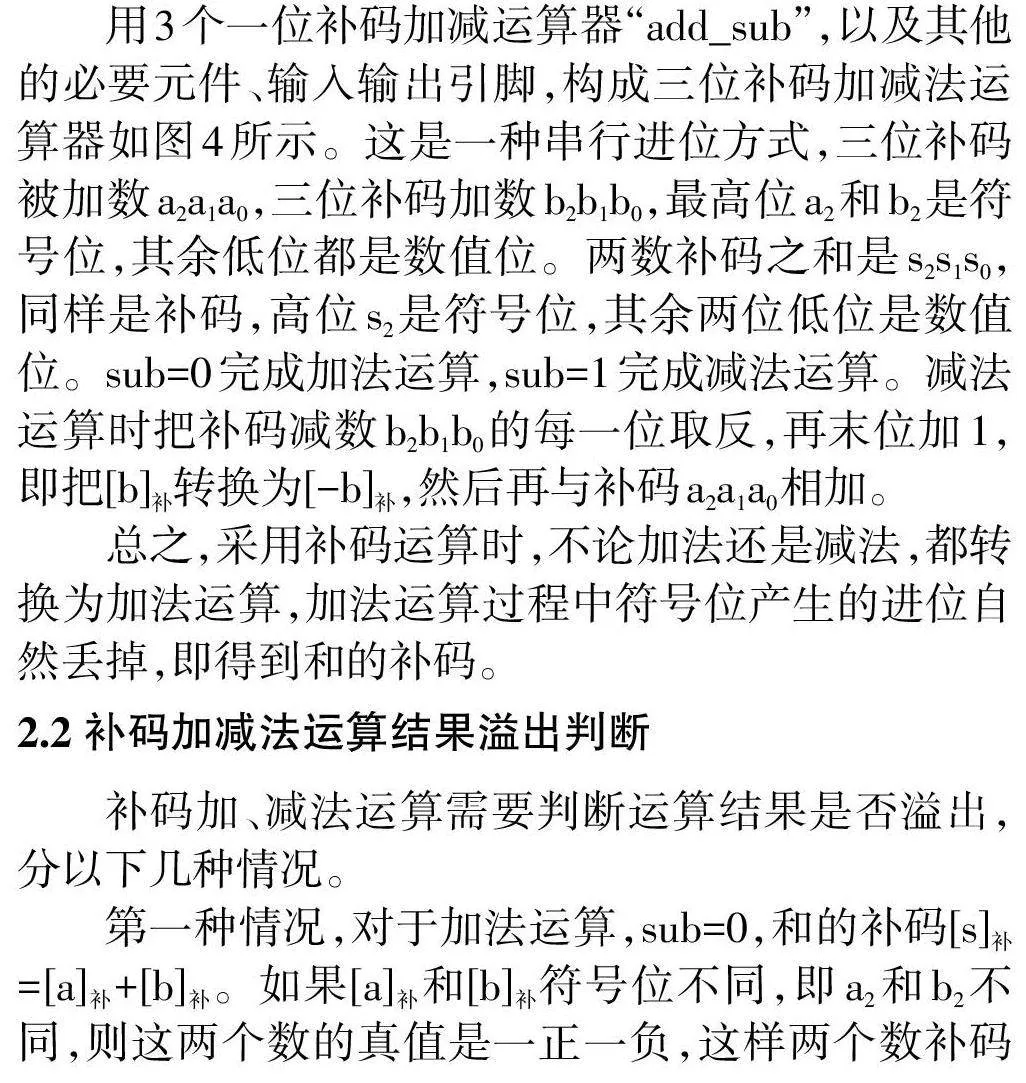

在QuartusII平台进行功能仿真,得到结果如图5 所示。

从图5可见,sub=0完成加法运算。被加数a=010 时,若加数b=001,两者真值都是正数,它们之和为s=011,ovf=0,没有溢出;而若加数b=011,两者同样都是正数,它们之和为s=101,ovf=1,溢出,由于两者之和是补码,其符号位是1,说明其真值是一个负数,这个结果是错的。因为结果溢出了,超出了表示范围。若加数b=101,其真值是负数,它们之和为s=111,其真值同样是负数,ovf=0,没有溢出。

被加数a=101时,若加数b=101,两者真值都是负数,它们之和为s=010,符号位的进位1被自然丢掉,这个和的真值是正数,结果是错的,因为溢出了,故ovf=1;而若加数b=111,两者同样真值都是负数,它们之和为s=100,这个结果是正确的,ovf=0,没有溢出;若加数b=011,其真值是正数,它们之和为s=000,这个结果同样是正确的,ovf=0,没有溢出。

4结束语

算术逻辑运算是数字系统的基本功能之一,是数字计算机中不可缺少的功能,其中的算术运算完成基本的二进制四则运算。在计算机中,多采用补码进行算术运算,进行二进制数据的加、减运算时,转换为加法运算。对乘除运算,则转换为加法和移位运算。所以,加法器是必不可少的元件。

本文在全加器的基础上,实现三位补码数据的加、减法运算,该方法简单易于实现,且容易推广到任意多位数据的加减运算,不足之处是采用串行进位的加法器,速度比较慢,这个可以通过并行进位加以改进。