基于力导向算法的国产继电保护装置热优化方法

摘要:为保证变电站继电保护装置的运行可靠性,突破原有仅凭经验进行热设计与分析的局限,对国产核心芯片与板卡进行精准建模,采用力导向算法优化热源布局。通过精细化热分析及实验验证表明:本方法改善了板卡局部热点与温度梯度分布,增加了国产化继电保护装置的热安全余量,提升了装置在工程现场长期运行的可靠性。

关键词:国产芯片;继电保护装置;精准建模;力导向算法;精细化热分析;可靠性

中图分类号:TK123文献标志码:A文章编号:1671-5276(2024)06-0205-06

Abstract:To ensure the operation reliability of relay protection devices in substations, by breaking through the limitations of the original thermal design and analysis merely based on experience, builds precise models of domestic core chips and printed circuit boards, and optimizes the layout of heat sources by using force-directed algorithm. The refined thermal analysis and experimental verification indicate that the optimized method improves the local hot spot and temperature gradient distribution of the pcb, increases the thermal safety margin of the domestic relay protection device, and reinforces the long-term operation reliability of the device on project site.

Keywords:domestic chip; relay protection device; precise modeling; force-directed algorithm; refined thermal analysis; reliability

0引言

长期以来,变电站继电保护装置CPU、FPGA等核心芯片完全依赖进口,随着中美贸易摩擦加剧,尤其是美国《2022芯片与科学法案》的签署,使自主可控、安全可靠成为智能电网的重要发展方向[1-2],继电保护装置芯片自主化进程进一步加速。国外半导体技术比较发达,芯片制程工艺先进,封装集成度高,功耗低,芯片研发、应用与量产均已经过多场景、长时间验证,可靠性较高。相比而言,国内芯片产业仍处于发展上升期,国产芯片在单位性能下的功耗和热稳定性与进口芯片相比存在较大差距。应用国产芯片的继电保护装置在工程现场运行的可靠性与装置内部发热情况息息相关,如芯片功耗高、发热大,加之散热设计不充分,将引起芯片参数漂移、热击穿等而引发设备误动或拒动等严重故障,危及电网运行安全[3]。

据统计,电子设备超过50%的失效故障均由器件温度超限导致,且失效概率随温度增加呈指数增长趋势[4],因此在系统及部件设计过程中开展科学合理、精确的热分析显得尤为重要。张瑾等[5]对自主龙芯3A处理器进行了封装和散热分析,使封装管壳能满足处理器高功耗的散热需求;谢秀娟等[6]针对FC-BGA(flip chip ball grid array)倒装芯片球栅格阵列的封装形式,通过详细的热模型分析以提高芯片的热可靠性;周辉等[7]通过理论模型与仿真分析相结合的方法,分析并改进了继电保护装置内部温度分布。但以上研究均只聚焦芯片或板卡单体,仿真分析颗粒度较粗,实际工程应用中设备对温度环境的适应性与仿真分析结果存在较大差异。

另外,许多继电保护装置有严格的防水、防尘要求,无法选择水冷、风冷等主动散热方式,通常采用密闭箱体与被动散热相结合的结构形式。虽然被动散热不需要冷却剂驱动装置,可靠性高,但散热效率低,元器件温升大,因此精细化的热分析对提升基于国产芯片的继电保护装置热可靠性具有更为重要的意义。本文在国产芯片与板卡两个维度开展热仿真精细化建模,突破了仅依靠经验进行优化设计的传统模式,应用力导向算法优化布局并进行仿真和实测验证,为基于国产芯片的继电保护装置开发提供指导,有利于提升设备在现场长期运行的可靠性。

1国产芯片与板卡精准建模

1.1芯片热仿真模型构建

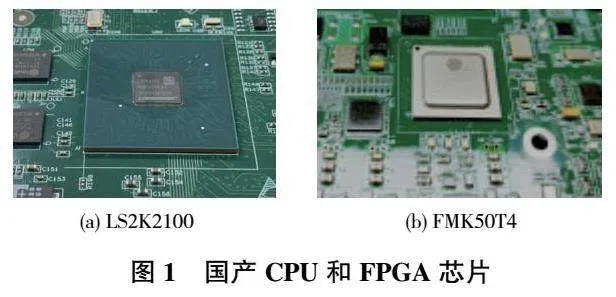

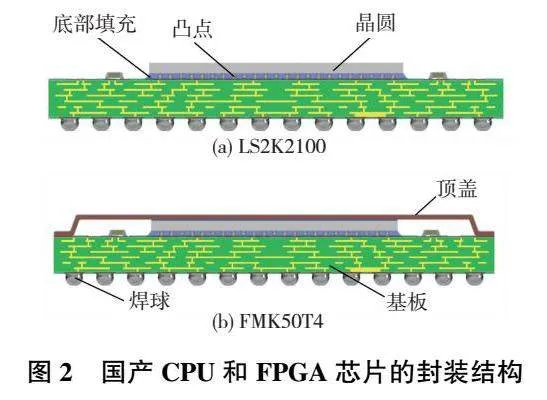

CPU芯片和FPGA芯片是继电保护装置中实现采集计算、通信处理等核心功能的关键元器件,单体功耗较高,是设备可靠性的关键。龙芯LS2K2100是一款面向工业控制与终端等领域的自主通用处理器,采用FC-BGA封装形式,将芯片正面朝下倒扣于封装管壳顶部,通过焊球凸点将芯片焊接到封装基板上,芯片上方无顶盖设计,如图1(a)所示。复旦微电子FMK50T4是一款高性能、小封装的自主可编程逻辑芯片,同样采用FC-BGA封装,且芯片上方有散热金属顶盖,如图1(b)所示。

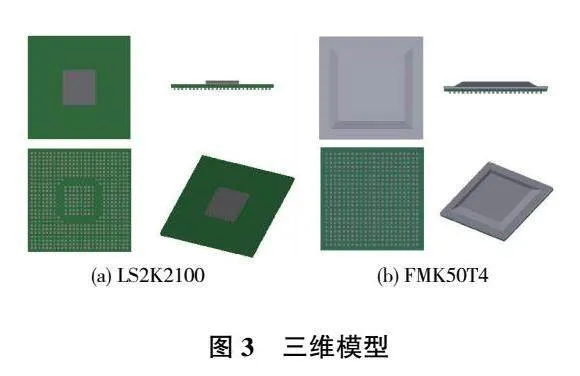

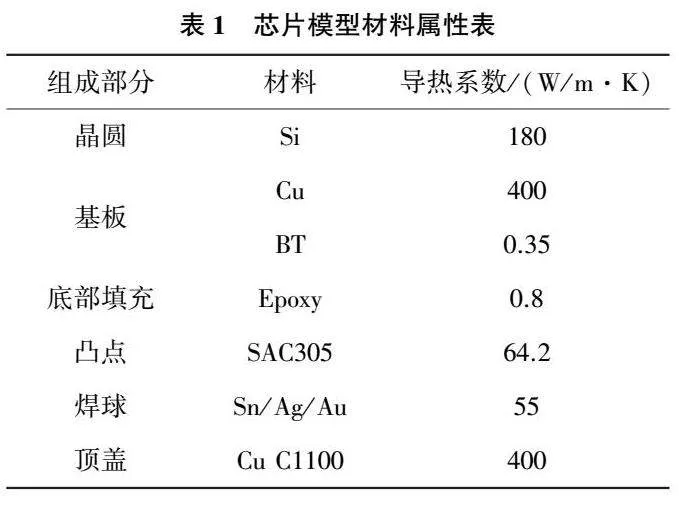

FC-BGA是目前自主CPU和FPGA芯片普遍采用的高密度封装形式。采用底部朝上、倒装在基板的结构形式,使芯片背面贴近封装管壳顶部,更利于散热[8]。龙芯LS2K2100与FMK50T4的封装结构,分别如图2(a)、图2(b)所示。根据CPU芯片、FPGA芯片的几何结构参数,建立如图3所示的三维模型。模型由晶圆(die)、基板(substrate)、底部填充(underfill)、凸点(bump)、焊球(solder ball)和顶盖(cover)等部分组成,并按表1设置各组成部分的材料属性与导热系数。

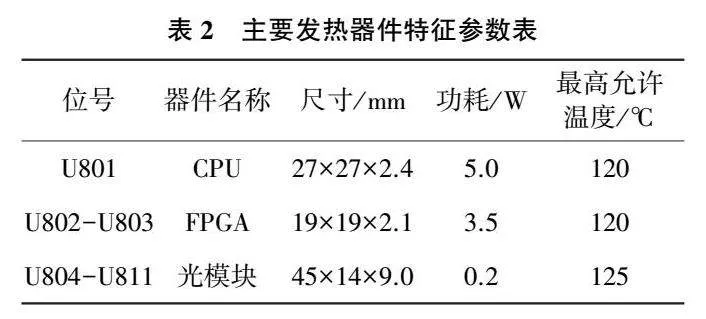

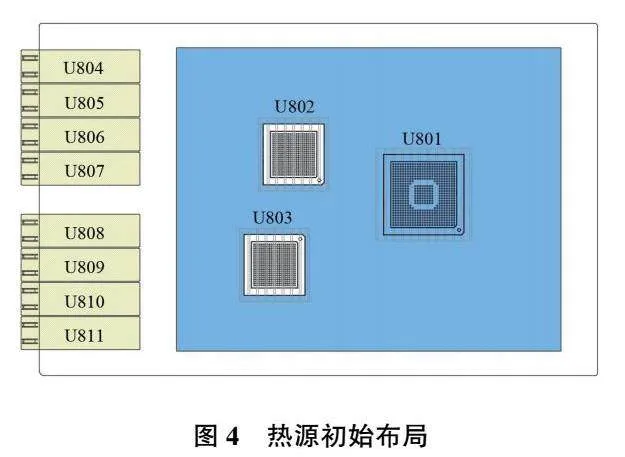

以继电保护装置的过程层通信处理板为例,该板卡实现过程层SV(sampled value)的接收和GOOSE(generic object oriented substation event)的收发功能,并和中央处理板之间交互实时数据。该板卡采用1片龙芯LS2K2100CPU芯片和2片FMK50T4FPGA芯片,CPU和FPGA之间通过PCIe接口交互实时数据。主要发热器件的初始布局如图4所示。CPU芯片、FPGA芯片和光通信模块是最主要的发热器件,其中光通信模块为外部物理接口,位置相对固定。为保证热仿真分析的裕度,器件功耗按正常工作时最大功耗或设计最大功耗取值。板卡上主要发热器件的特征参数如表2所示。

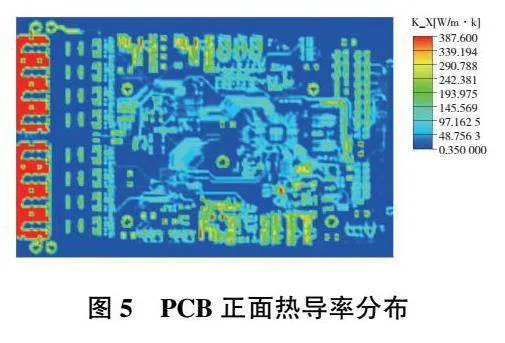

部均有不同的导热率特性。仿真分析时,通常将PCB粗略地简化为平面方向和垂直方向呈不同热导率的均匀材质,此种简化对于PCB各层走线分布相对均匀的设计具有一定的合理性。但是,采用自主CPU和FPGA的通信处理板器件密度大、走线复杂,如果不考虑PCB热导率的局部变化,仍使用简化模型,将无法清晰反映实际PCB的导热特性,从而影响热仿真分析的准确性[9]。

为此,本研究先期完成通信处理板的首版设计,并在热仿真分析时通过导入ECAD布线与过孔信息建立板卡的精准模型,如图5所示。从PCB正面热导率分布可以看出,精准模型下PCB热导率与铜层分布、走线疏密、过孔分布相吻合,铜层面积大的区域热导率高,最高约387.6W/m·K,而绝缘介质区域热导率仅0.35W/m·K。该模型较准确地反映了PCB各向与局部均有不同的热导率特征,为板卡热仿真分析的精准性提供了基础支撑。

2基于精准模型的热仿真分析

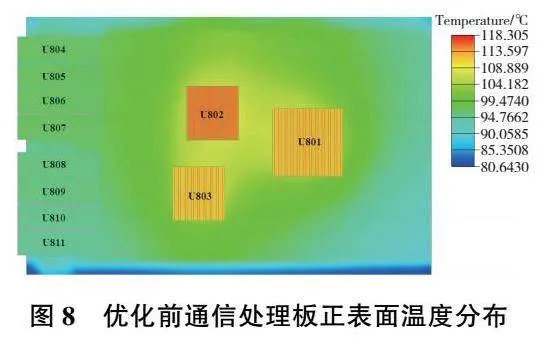

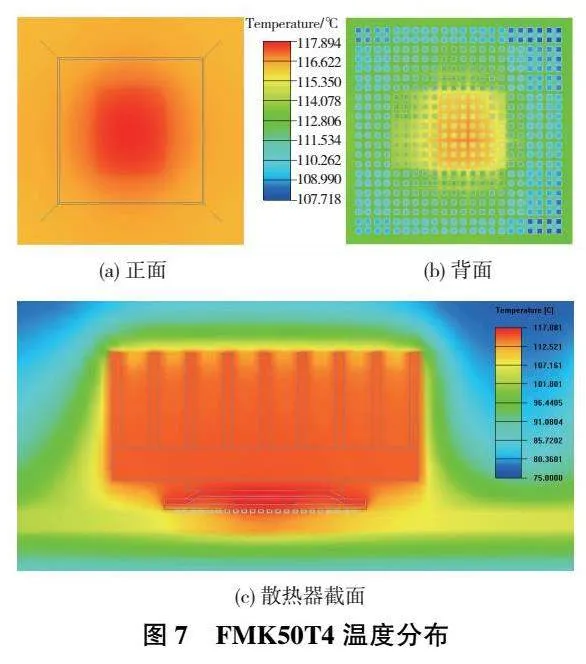

基于上述国产芯片和板卡的精准模型,使用有限元法求解环境温度75℃、自然散热条件下通信处理板的稳态温度分布。LS2K2100CPU芯片温度分布如图6所示,位号U802的FMK50T4FPGA芯片的温度分布如图7所示。CPU芯片最高结点温度118.3℃,位号U802、U803的FPGA芯片最高结点温度分别为117.9℃、115.1℃,都非常接近芯片最高允许的结点温度,安全余量较小。通信处理板正表面温度分布如图8所示。从仿真结果可以看出,芯片产生的热量主要集中在封装内部,通过芯片顶部散热器传导至周围空气中。通信处理板3颗芯片附近热量集聚,在热耦合作用下,热点附近温度梯度大,很可能产生较大的热应力。当热应力到达一定数值,将导致PCB变形、焊接部位开裂和元器件失效等可靠性问题[10]。因此,为确保国产芯片在75℃环境温度下能可靠地工作,需要科学合理地优化上述芯片布局,降低芯片结温的同时,使板卡的温度分布更加均匀,提升板卡的热稳定性。

3基于力导向算法的热布局优化

3.1力导向算法布局优化

器件热布局可以通过优化算法来求解。近年来,国内外许多学者对此类问题进行了深入的探讨和研究,取得了显著的进展,提出了多种优化模型和算法,其中应用较多的有遗传算法、模拟退火算法和力导向算法等。遗传算法训练时间长,对初始种群的选择有很强的依赖性[11];模拟退火算法采用慢降温、多抽样等方式,算法效率有所提高,但容易导致局部最优解情况[12]。力导向算法兼具上述算法优点,综合性能较好[13]。

力导向算法假定任意器件之间都存在互斥力,斥力大小与芯片功耗成正比,与芯片距离成反比。设PCB长为L,宽为W,(Xi,Yi)是元器件di(i=1,2,…,m)的位置坐标。由于PCB侧面耗散的热量与PCB顶面、底面耗散的热量相比可以忽略,因此模型假设PCB侧面绝热。为解决边界不连续问题,将对称平面放置在4个侧面,如图9所示。此时左下角位于原点的物理区域PCB与有限个热源被镜像成无边界PCB与无限个镜像热源。其中row、column是指力导向算法提及的镜像模型中,某PCB对应位置的行与列位置数值。

设图9中物理区域PCB上器件dj的位置坐标为(Xj,Yj),镜像模型中位于r行c列的PCB上器件dj的位置坐标为(Xj(r,c),Yj(r,c)),则有:

为模拟热传导机制,定义无边界板中器件dj施加到物理区域器件di的斥力为

式中:αi为器件di的热敏感系数,一般器件αi=1,热敏感器件αigt;1;qj是器件dj的功耗;Δri,j(r,c)是无边界板中器件dj到物理区域器件di的距离。

将fi,j(r,c)分解,得到x轴、y轴分量:

根据线性叠加原理,将热源扩充至无边界区域的m个热源,则物理区域中器件di受到的总斥力为

Fzi=∑mj=1fzi,j+∑式中z是x轴或y轴分量。由于f(r,c)i,j随Δr(r,c)i,j平方而快速衰减,算法在实际应用中可以将a设为5,此时物理区域被镜像为原来面积的121倍。至此,热布局优化问题转变为求解方程Fzi=0,获得热源坐标的问题。先求Fzi的偏导数:

F′zi=∑mj=1{f′zi,j+∑将器件di的位置zi按式(12)、式(13)进行迭代:

式中系数取0.5是因为两个器件之间斥力是相互的。如计算得到的zi,new超出物理区域,则将Δzi减半取值,直至zi,new在物理区域内。为了使求解计算能收敛,定义

当迭代计算满足式(15)、式(16)时,判定计算收敛:

设置求解精度ε1=0.01,ε2=0.01。从初始布局开始计算Norm,判断是否满足精度要求,若不满足精度要求,则按式(12)、式(13)计算新的器件位置进行迭代,直至同时满足收敛准则式(15)与式(16)为止。此时器件坐标即为力导向算法优化后的热布局。

3.2热布局优化仿真验证

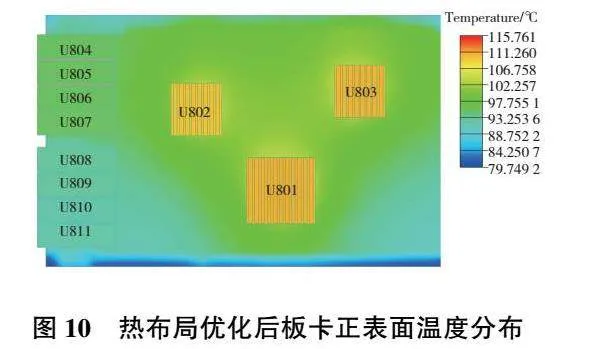

在图4所示的通信处理板上划定深色阴影区域为CPU芯片与FPGA芯片布局可调整区域,作为算法的物理区域。将物理区域的尺寸与芯片对应功耗输入由Python语言实现的算法程序中。程序从随机布局开始,计算收敛后得到CPU芯片与FPGA芯片优化后的位置坐标。按算法优化后的芯片位置重新调整板卡电路设计,使用热仿真分析软件求解其在自然散热条件下的稳态温度分布,如图10所示。热布局优化前后芯片温度的仿真计算结果如表3所示。

从仿真对比结果可以看出,优化前CPU芯片与FPGA芯片布局位置比较靠近,芯片产生的热量没有足够的空间传导,因热量积聚导致芯片温度的升高。算法合理优化了芯片间距与位置关系,使CPU芯片和两颗FPGA芯片的结温分别下降了2.5℃、5.3℃和1.6℃,芯片温升得到较大改善。

3.3热布局优化实测验证

为进一步验证基于力导向算法热布局优化方法的有效性,按优化前后两种热布局设计制造通信处理板,并在CPU和两颗FPGA芯片正表面固定铂电阻温度传感器,配置相同负载,放入标准温度试验箱VC37060内,进行75℃高温运行实验。引出温度传感器连接到数据采集终端,通过计算机读取、处理后得到芯片的结温数据。在运行2h后,记录热平衡时测试芯片表面温度如表4所示。

从实测结果看,CPU芯片结点温度下降了2.9℃,两颗FPGA芯片分别下降了5.9℃、2.5℃,PCB平均温度下降了2.2℃。通信处理板高温运行实测数据和仿真结果接近,进一步验证了热仿真模型的准确性和布局优化效果。板卡实测效果略优于仿真数据,主要是因为温度试验箱为了保证箱内温度均匀性,配置了系统风扇,内部相比自然散热条件有相对更高的气流速度,一定程度上提升了PCB与芯片散热器的散热效率。

需要注意的是,设计板卡电路时,在仿真优化的基础上还需要结合板卡的硬件资源情况和接口设计复杂度,统筹考虑整体优化布局,在电路设计和仿真优化之间进行迭代,才能设计出满足实际目标要求的产品。

4结语

目前国产CPU、FPGA等高端芯片制造工艺相对落后,芯片功耗较高。采用国产芯片的继电保护装置在工程应用时面临热可靠性问题。针对此问题,本文建立了国产芯片与板卡的精准模型,并开展了热仿真计算与分析。同时,采用力导向算法对原来仅凭经验布置的芯片热源位置进行了科学布局优化,并通过仿真与实测对比加以验证。本研究采用精细化热分析和热布局优化的闭环验证方法,实现了国产芯片热源的控温要求,改善了板卡局部热点与温度梯度分布,增加了国产化继电保护装置的热安全余量,提升了设备现场长期运行的可靠性,对工业领域高防护要求的电子设备热可靠性设计具有一定的借鉴意义。

参考文献:

[1] 仲伟,王仲,陶保震,等. 新一代自主可控保护装置软硬件平台技术[J]. 电力系统保护与控制,2022,50(6):135-140.

[2] 李友军,周华良,徐广辉,等. 基于龙芯处理器的继电保护装置平台及关键技术[J]. 电力自动化设备,2022,42(3):218-224.

[3] 郑玉平. 电网继电保护技术与应用[M]. 北京:中国电力出版社,2019:164-168.

[4] 于慈远,于湘珍,杨为民. 电子设备热分析/热设计/热测试技术初步研究[J]. 微电子学,2000,30(5):334-337.

[5] 张瑾,王剑. 龙芯3A处理器封装的散热设计[J]. 计算机工程与科学,2009,31(增刊1):120-124.

[6] 谢秀娟,杨少柒,罗成,等. 倒装陶瓷球栅阵列电子封装的热模型研究[J]. 电子元件与材料,2011,30(11):68-71.

[7] 周辉,郑立亮,沈敏,等. 基于Icepak的电网保护装置热设计研究[J]. 机械制造与自动化,2022,51(4):206-210.

[8] MALLIK D. Advanced package technologies for high-performance systems[J]. Intel Technology Journal,2005,9(4):259-271.

[9] 马岩. 印制电路板详细模型的热仿真分析[J]. 机械设计与制造工程,2016,45(1):52-55.

[10] 文惠东,黄颖卓,林鹏荣,等. 陶瓷封装倒装焊器件热学环境可靠性评估[J]. 半导体技术,2019,44(9):723-727.

[11] 阎德劲,周德俭,黄春跃,等. 基于遗传算法的表面组装电子元件热布局优化[J]. 电子机械工程,2007,23(2):12-17.

[12] 王乃龙,戴宏宇,周润德. 用模拟退火算法实现集成电路热布局优化[J]. 半导体学报,2003,24(4):427-432.

[13] LEE J. Thermal placement algorithm based on heat conduction analogy[J]. IEEE Transactions on Components and Packaging Technologies,2003,26(2):473-482.

收稿日期:20230309

基金项目:国家重点研发计划资助项目(2021YFB2401000)

第一作者简介:甘云华(1983—),男,高级工程师,硕士,研究方向为电力二次设备共性平台技术,shenmin1981@sina.cn。

DOI:10.19344/j.cnki.issn1671-5276.2024.06.041