基于FPGA的多通道采集系统时序设计方法

摘 要:舰船声呐的湿端设备位于水下,其所在环境复杂多变,设备受小型化和高集成度要求约束,声呐湿端信号采集系统时间同步精度难以保持稳定,因此不能保证声呐设备的工作稳定性。本文对硬件电路设计、现场可编程逻辑门列阵(Field Programmable Gate Array,FPGA)控制程序和设备应用环境可能会对控制时序产生影响的3个方面因素进行分析,优化基于FPGA的多通道采集系统时序设计,在FPGA中构建同步检测模块,对同步采集延迟进行闭环补偿,形成负反馈环路。对多通道时序进行补偿并修正,既保证信号采集的同步性,又提高了FPGA控制程序时序设计裕度,解决了数据采集系统受物理位置等因素影响导致各个通道同步延迟不一致的问题,保证多通道采集系统各通道的一致性,提高设备运行的稳定性。

关键词:多通道采集;时序设计;同步延迟

中图分类号:O 235" " " " " " 文献标志码:A

随着我国近海资源陆续开发,水下探测设备需求增加[1],水下控制系统小型化、集成化和模块化的设计方法在工程中的应用前景广泛[2-3]。受水下安装使用环境复杂、安装布置空间狭小等因素限制[4],大规模传感器阵列以及其配套电路对水下可应用空间将进一步压缩[5]。本文高效地利用一套控制处理电路以及相应程序完成所需功能,利用高性能现场可编程逻辑门列阵(Field Programmable Gate Array,FPGA)实时实现多通道模数[6]、数模转换以及同步数据计算处理和高速传输等功能,并采用时延补偿等手段[7]使控制电路时序裕度满足复杂环境应用要求。

1 多通道采集系统电路设计

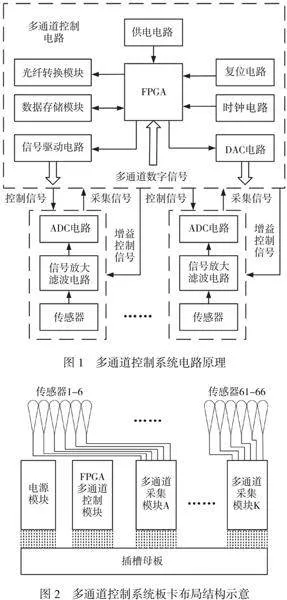

多通道采集系统电路原理如图1所示,本系统采用高性能FPGA为核心处理器,同步控制多通道控制信号,实时并行处理多通道采集信号,并根据处理数据控制模/数转换(Digital to Analog Convertor,DAC)电路产生反馈信号,利用增益控制信号调节各个通道放大幅度,在采集数据处理过程中利用数据存储模块对高速大规模矩阵数据进行缓存处理,最终利用高速差分数据接口,将数字信号转换为光纤信号进行远距离传输通信。

多通道采集系统电路板卡布局如图2所示,将电源模块、FPGA多通道控制模块和多通道采集模块分别安装在插槽母板上,利用扩展多通道采集模块对更多接收通道信号进行采集控制。传感器利用引线将实时接收的电信号传递至多通道采集模块,FPGA多通道控制模块利用组合逻辑与时序控制完成多通道信号采集处理功能,利用千兆以太网光纤实时接收上位机指令并传输处理后的数据。

2 多通道采集系统程序设计

多通道采集系统程序设计主要包括同步采集信号控制程序设计、时序设计、同步延迟校准程序设计和FPGA驱动信号参数设计。

2.1 同步采集信号控制程序设计

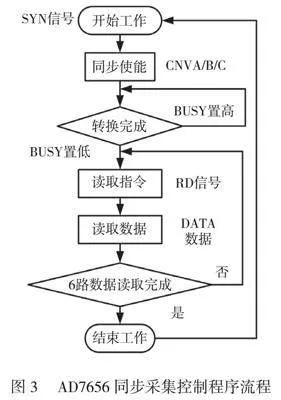

在多通道采集系统中,FPGA对各个采集模块中各路模拟数字转换(Analog to Digital Convertor,ADC)芯片直接进行控制,完成多通道信号实时同步转换,单路ADC控制主要针对时钟信号(Serial Clock,SCK)、片选信号(Chip Select,CS)、转换信号(Convert,CNV)、非空闲信号(BUSY)、读信号(Read,RD)和串行数据输出(Serial Data Output,SDO)信号进行读、写控制等操作。本系统采用16位250 kHz采样频率的AD7656作为ADC芯片,完成同步采集6路接收通道。根据AD7656内部三路并行控制信号接口的时序逻辑图进行程序设计,须转换使能AD7656信号至CNVA/B/C端口(内部有A、B和C三路并行转换通道),使ADC进行模数转换,当ADC工作状态指示信号显示已完成数据转换时,可进行读取转换结果指令操作,读取并行数据位转换结果,在该过程中须保持片选信号使能,六路通道重复完成读取数据操作后,本周期采集控制程序结束,具体流程如图3所示。

2.2 多通道采集控制时序设计

当接收同步信号后,FPGA将同步产生多路CNV控制信号,ADC进行模拟信号采集锁存,并进行数字转换,在转换过程中使BUSY信号置高,转换时间tCNV为典型值3 µs。转换结束后,控制RD信号置低,进行ADC读操作,ADC转换至读使能信号时间间隔t1无最小值要求,RD控制信号脉宽t2为36 ns~45 ns,2个通道读取RD控制信号最小使能间隔t3为6 ns,ADC数据端口响应RD信号延迟时间t4为36 ns~45 ns,数据信号保持时间t5为10 ns,多通道采集电路控制信号时序如图4所示。

2.3 同步延迟校准程序

在多通道ADC电路设计中,经过简单测量很难得到FPGA控制信号与同步信号延迟的具体数值,但是可以利用FPGA产生高频Check信号,实时读取各个ADC反馈的BUSY信号状态。AD7656内部转换周期为3 µs,因此可以检测各个CNV转换信号与同步信号的时延周期数,并对时延一致性进行调整,同步延迟校准检测时序如图5所示。

2.4 FPGA驱动信号参数设计

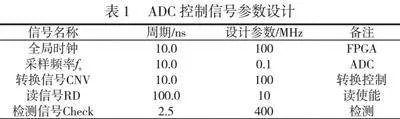

在多通道采集系统中,利用FPGA 进行倍频、分频等操作,得到各个控制信号。FPGA输入时钟为100 MHz信号,利用内部锁存转换为全局时钟,经过计数器1 000倍分频得到CNV信号,因此ADC采样频率为100 kHz,Check信号为100 MHz,全局时钟信号倍频4倍得到400 MHz检测信号,当检测BUSY信号由置高变为置低时,即CNV信号上升沿至BUSY信号下降沿的时间周期为3 μs,Check检测信号累计计数至1 200次后,以10 MHz频率将RD信号置低,同时下达对模数转换器进行数据并行输出的指令,满足数据输出时间为10 ns限制要求,ADC各控制信号参数设计见表1。

3 时序影响因素分析

3.1 硬件电路设计影响分析

在多通道采集系统硬件电路中,在不同的布局、布线条件下,各个信号会出现不同的延迟误差,由于FPGA驱动信号能力不足,因此需要利用驱动芯片作为控制信号的中继放大,增强多通道采集电路的驱动性能,同时ADC芯片数字输出端也需要利用缓存器对多路数据信号进行隔离、保存,因此带来的FPGA控制时序需要进行测量补偿。

在采集电路中经常使用串联、并联阻抗来减少高频时钟、数据信号尖峰对模拟信号的干扰,因此FPGA输出的源端信号经过阻抗处理后,受电路中寄生电容影响会产生RC滤波效果,原来较为陡峭的上升、下降时序会更加平缓。各个采集通道电路特性存在细微差别,FPGA的同步控制信号在不同通道的响应也存在差别,导致多通道控制时序出现错误或延迟,需要时序测量并补偿来对这类问题进行修正。

3.2 FPGA控制程序影响分析

在FPGA程序设计过程中,对模块化进行功能设计、调试,在程序整合过程中会出现顶层程序融合导致FPGA内部资源优化,寄存器传输级(Register transfer level,RTL)结构改变导致原程序时序裕度不能满足多通道采集电路同时工作的要求。在FPGA控制程序设计过程中,受芯片内部资源限制,多个D触发器、与非门电路多层级嵌套使用,导致触发信号延迟时间累加,当累加结果超过FPGA内部工作周期限制时,原程序时序出现错拍现象,导致时序整体延迟或引起程序逻辑错误。可设计内部校验模块,根据计数器对控制程序的时序以及逻辑结果进行核验,解决FPGA内部控制程序中的时序问题。

3.3 设备应用环境影响分析

多通道采集系统在高温、低温、高盐度和湿热等复杂环境中长时间工作,会对系统控制程序的时序产生影响。在高温环境中,受温漂影响,供电电路、时钟电路、FPGA扇入端口参数、扇出端口参数、ADC驱动性能以及容性器件等均会产生变化,造成FPGA驱动控制信号以及ADC响应信号时序发生变化。在低温环境中,各个芯片程序启动、输入输出电路电平响应、分离元器件参数变化等也会对FPGA程序产生影响。声呐设备湿端受舰船在水中长时间摇摆状态以及海浪、洋流和暗涌等影响,设备结构会变动,导致设备散热部件导热性能下降,局部产生较大温升,多通道采集模拟信号会发生变化。在FPGA内部构建检测模块,实时监测程序的主要控制参数,利用计数器对多通道采集电路同步控制时序进行闭环控制,设置时序控制裕量,在FPGA时序裕度条件下,可以保证设备正常、稳定地运行。

4 多通道采集控制信号时延测量

4.1 同步时延测量方法

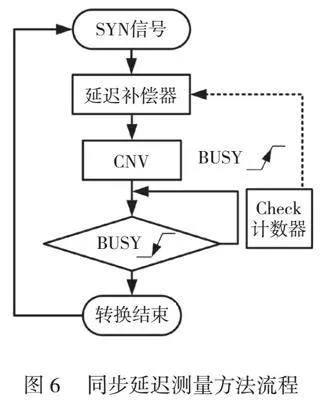

在多通道采集系统正常工作的过程中,利用Check信号对各个采集通道ADC芯片BUSY输出信号进行检测,以FPGA转换控制信号CNV上升沿为Check计数起始时刻,以ADC输出状态信号BUSY下降沿为截止时刻,统计Check信号个数,根据各个通道检测的Check信号个数计算实际信号延迟大小,并将各个通道延迟情况反馈至延迟补偿器中,在进行下个转换周期的过程中,对CNV信号进行延迟调节,按照Check检测信号周期将延迟周期补偿至各个转换信号,形成闭环式自动调节方法,同步延迟测量方法流程如图6所示。使用Check计数器缓存数据,并利用累加移位进行平滑处理,在每个转换周期均可进行自动补偿调节。在理论设计无延迟的情况下,CNV信号转换至BUSY信号时间应为3 μs,对应Check计数为1 200个。

4.2 同步时延测量结果以及分析

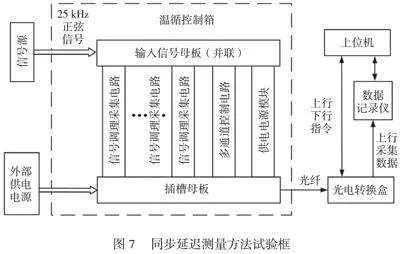

受高温环境中寄生电容变化影响,高速信号延时将产生较大偏差,利用温循控制箱创造50 ℃高温工作环境,将信号源产生的25 kHz正弦信号输入母板,进行并连后,接入各个信号调理采集电路ADC前端,多通道控制电路按照同步下行指令对不同采集板卡模块的同步延迟进行标校,构成同步信号延迟控制负反馈环路,在对各个接收采集通道进行同步延迟测量后,将采集系统的SYN同步信号按照各个ADC芯片Check计数器差值周期进行延迟。多通道同步采集数据光纤经光电转换后存储至数据记录仪中,具体测量方试验框如图7所示。

按照1 s工作周期对多通道控制电路FPGA中Check信号统计数据进行均值处理,输出延迟对照结果见表2,不同编号的采集模块的同步信号延迟主要受物理位置影响,FPGA与各多通道采集模块的距离增加,延迟量呈增大趋势。将多通道采集模块在插槽母板中的原顺序按逆序重新排列后进行测量,结果与原顺序测量结果基本保持一致。多通道采集系统对同步时延进行测量、闭环反馈补偿后,在各个采集模块中,ADC芯片的同步信号延迟均可降至1个Check信号周期内,即5 ns,各采集通道将很大程度地降低物理位置导致的同步采集时延,各个通道采集同步性很大程度地提高。对数据记录仪中多通道采集数据进行对比,经过延迟补偿后各通道转换数据未出现时序异常,各个通道相位一致性由0.5°提高至0.1°。

5 结论

在FPGA中构建高频检测模块,对同步采集延迟进行闭环补偿,形成负反馈环路,降低了多通道采集控制信号的同步延迟,在多通道水声信号检测的实际工程应用中,仅利用闭环调节同步采集延迟时间,即可获得较优秀的多通道采集系统一致性指标。在硬件电路设计、FPGA控制程序以及设备应用环境影响3个方面,对采集系统时序影响原理进行分析,有助于在FPGA控制程序设计中提高时序裕度,保证在复杂环境中采集系统性能指标,提高了设备的稳定性。

参考文献

[1] ROBERT W J. China’s maritime strategy and national security"in the South China Sea[J]. Journal intelligence and national security,2019,3(36):1-7.

[2]杨益新,韩一娜,赵瑞琴,等.海洋声学目标探测技术研究现状和发展趋势[J].水下无人系统学报,2018,26(5):369-386.

[3]张延厚,王超,张奇,等. 水声目标探测和识别融合技术发展综述[J].信号处理. 2023,10(35):1711-1727.

[4]卢俊,张群飞,史文涛,等.探测通信一体化研究现状与发展趋势[J].信号处理,2019,35(9):1484-1495.

[5]葛锡云,周宏坤,郭杨阳,等.水下平台声学兼容性技术综述[J].海洋工程装备与技术,2022,6(7):395-400.

[6]梁晨,于骏申.多通道高精度采集系统设计[J].声学技术,2019,5(38):281-282.

[7]田坦,刘国枝,孙大军. 声纳技术[M].哈尔滨:哈尔滨工程大学出版社,2004.