ESD保护电路在HDMI板级信号完整性中的影响分析及其布局优化研究

摘" 要: 为了解决HDMI接入ESD保护电路后信号完整性受破坏等问题,从器件的空间布局对HDMI信号完整性影响进行研究分析,同时考虑了瞬态电压抑制(TVS)高频寄生参数的影响,搭建了ESD放电模型和TVS高频等效电路模型,并对其可靠性进行了验证。从差分器件接入信号线旋转角度和彼此间错开距离研究其对信号完整性的影响,设计了25套不同夹角和4套不同错开距离的板级模型,在不同特性的传输频率下进行S参数仿真,并从中选取出垂直型、水平型、错开型三种具有代表性的空间布局模型,利用有限元仿真得到差分信号线的S参数和眼图。仿真结果表明,垂直型排布相比于其他两种典型空间布局,回波损耗平均降低了248.1%,插入损耗平均降低了20.6%,眼图的眼宽和眼高在三种空间布局中最大。研究成果为PCB静电放电保护电路分析与设计提供了布局优化指导。

关键词: 静电放电(ESD); HDMI; 信号完整性; 空间布局优化; 瞬态电压抑制(TVS); S参数; 有限元仿真

中图分类号: TN702⁃34" " " " " " " " " " " " " " "文献标识码: A" " " " " " " " " " " 文章编号: 1004⁃373X(2024)08⁃0068⁃07

Research on influence analysis and layout optimization of ESD protection circuits on signal integrity at HDMI board level

WANG Miao, LI Jiahao, TANG Hao, GUO Ya

(Key Laboratory of Advanced Process Control in Light Industry, Ministry of Education, School of Internet of Things Engineering,

Jiangnan University, Wuxi 214122, China)

Abstract: In order to solve the problem of signal integrity damage after HDMI is connected to ESD (electrostatic discharge) protection circuits, the effectegrity of HDMI signal is analyzed. Considering the influence of high⁃frequency parasitic parameters in transient voltage suppression (TVS), the ESD discharge model and TVS high frequency equivalent circuit model are established and their reliability is verified. The influence on signal integrity was studied from rotation angle and staggered distance of differential device access signal lines. Twenty⁃five sets of plate⁃level models with different angles and four sets of different staggered distances are designed, and S⁃parameter simulation is carried out under different transmission frequencies with different characteristics. Three representative spatial layout models, vertical, horizontal, and staggered, are selected. The S⁃parameter and the eye chart of the difference signal line were obtained by means of the finite element simulation. The simulation results show that, compared with the other two typical spatial layouts, the return loss and insertion loss of the vertical layout are reduced by 248.1% and 20.6% on average. The eye width and eye height of the eye chart are the largest among the three spatial layouts. The results provide layout optimization guidance for the analysis and design of PCB electrostatic discharge protection circuits.

Keywords: ESD; HDMI; signal integrity; spatial layout optimization; TVS; S parameter; finite element simulation

0" 引" 言

高速电路板的静电放电(ESD)保护是保证电子系统稳定运行的基础,目前电子系统的外部部件与内部高速电路板一般有对应的静电防护措施,如机壳接地处理、绝缘材料隔离等[1]。而高速电路板接口部分一般需要独立的静电放电保护,常见措施是在高速信号线接ESD(Electro⁃Static Discharge)保护芯片或者接TVS(Transient Voltage Suppressor)保护电路[2],后者相较于前者响应速度更快,适合高速的小信号保护。ESD保护芯片使用串联方式接入电路,对信号完整性影响小;而TVS保护电路多采用并联接入,不合理的空间布局会对高速信号完整性产生破坏[3]。

在PCB板级静电放电仿真和高速信号的信号完整性方面,国内外学者做了大量的研究工作。例如,林汉念对系统级ESD鲁棒性进行了研究,并就TVS位置对ESD抑制性能进行了实验。但该实验只研究了单端TVS与ESD抑制性能关系,并没有考虑到TVS对传输线性能的影响[4]。V. Kuznetsov搭建了TVS等效模型,并针对该模型的ESD抑制能力进行了研究分析。但该模型只适用于低频情况,其在高频下的可靠性无法确定[5]。黄阳志就ESD保护电路对传输线的信号完整性影响进行了研究,但并未提出优化ESD保护电路的设计方案,而是提出了一种新的电路模型进行改善[6]。李搏实现了一种系统级封装的ESD保护电路,采用TVS管构建合理的ESD电流泄放路径,减少了对信号的干扰[7],将TVS静电防护推进到系统封装级。该方案只适用于芯片封装设计,无法针对PCB板级设计进行改善。

综上所述,国内外学者在ESD保护电路中对信号完整性进行了深入研究,但多数是针对单端低频信号进行分析设计,还未有人研究过ESD保护电路对差分高速信号完整性的影响,尤其是HDMI高速差分信号总线,其对高频信号完整性要求更高。

HDMI作为人体直接接触的接口,极易产生静电放电现象并威胁电路板[8],而使用TVS管进行静电防护则会对高速差分信号的完整性产生破坏。因此,研究如何在保证静电防护下改善其信号完整性具有重要意义[9]。实际设计中,改变器件空间布局是一种便捷高效的优化方法,因此研究TVS器件空间布局对HDMI总线的信号完整性影响则具有重要的工程意义[10]。

国内外鲜有开展有关TVS管的空间布局对HDMI的信号完整性影响方面的研究,其他学者要么研究TVS电路对ESD抑制性能的影响,要么研究ESD保护芯片对信号完整性的影响[11],鲜有考虑到高频下TVS特性变化和对高速差分信号完整性的破坏。

针对该问题,本文研究ESD保护电路对HDMI板级信号完整性的影响,拟提出一种HDMI总线的ESD保护电路布局设计参考方法,在保证ESD的抑制性能下,最大程度地降低其对HDMI高速差分信号的信号完整性破坏。

1" TVS高频模型搭建及ESD电路仿真

针对HDMI总线的高速差分信号完整性研究,需要考虑TVS管的高频特性对差分信号的影响。利用半导体物理方法搭建TVS高频数学模型,再以EC61000⁃4⁃2标准设计静电放电模拟器,通过TVS高频模型对静电放电模拟器的抑制效果进行分析,验证TVS高频模型的可信度,以便后续将TVS高频模型加入板级系统进行仿真分析[11⁃13]。

1.1" TVS高频模型的建立

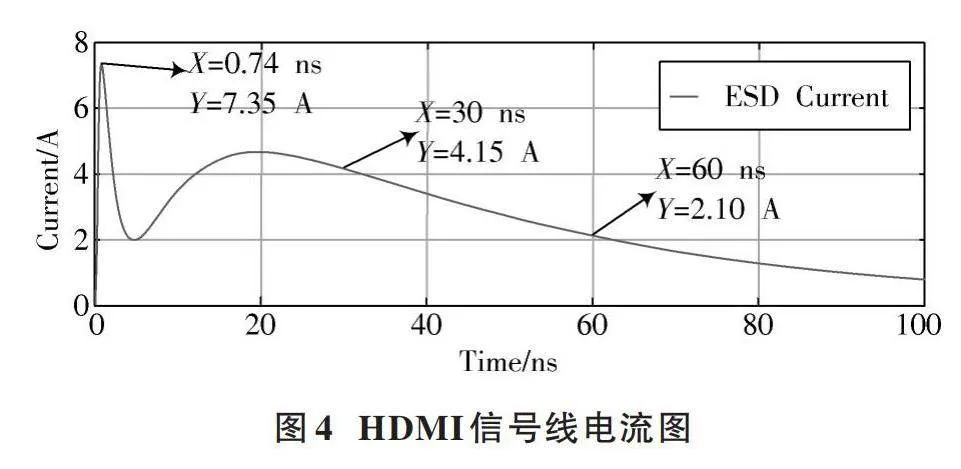

本文通过半导体物理估算方法建立一种TVS高频数学模型,并使用SPICE(Simulation Program with Integrated Circuit Emphasis)搭建等效电路模型进行电路仿真。该方法不需要精确的TVS电气参数,直接从物理模型推导而得[14]。瞬态二极管一般由齐纳二极管组成,其高频模型如图1所示。

当TVS正向导通时,PN结电气特性类似于普通二极管,主要由串联电阻(Rs)、寄生电感(Ls)、结电容(Cj)、扩散电导(Gd)和扩散电容(Cd)组成。通常TVS器件电压低于结击穿电压,此时TVS不导通,仅有泄露电流(IR)通过,对外呈现高阻态;当遇到静电放电现象时,TVS器件两端电压瞬间上升,超过结击穿电压,此时击穿电压和击穿电流之间的关系可以用击穿电阻(Rz)描述,PN结通过放电回路释放电荷。TVS对ESD干扰的抑制能力主要受器件的寄生电感、电阻影响,对首个静电脉冲抑制效果明显。故TVS高频模型主要考虑寄生电感、串联电阻、结电容的影响[15]。

1) 寄生电感(Ls):主要由封装引入的寄生串联电感和管脚引线电感引起。假设走线电感的长度为l,直径为d,其电感方程式描述为:

[Ls=200×10-9×l×2.3ln4ld-0.75] (1)

2) 串联电阻(Rs):主要是由导线电阻、金属⁃重掺杂的欧姆接触电阻和体电阻组成,一般在中低频情况下串联电阻可以等效成导线电阻。设电阻率为ρ,导线长度为L,导线截面积为A,则电阻方程式描述为:

[Rs=ρLA] (2)

3) 结电容(Cj):主要是TVS在空间耗尽区形成了平板电容。假设反向偏压为UA,真空介电常数为ε0,导线截面积为A,则结电容方程式描述为:

[Cj=11.9Aε011.9ε00.4×10-41-UA121-UA12] (3)

结合常用的TVS管P6SMB6的参数进行参考设计,假设截面积为0.2 cm2的N型掺杂硅,非击穿状态下反向偏压与HDMI信号电压相等为5 V时,代入式(3)可知,结电容为25.6 pF。假设TVS管两端引脚走线长度l=1 cm,d=0.15 cm,代入式(1)计算寄生电感Ls=15 nH。假设TVS管的导线电阻率为0.04 Ω·cm,导线长度为2 cm,导线截面积为0.2 cm2,代入式(2)计算串联电阻[16]Rs=0.4 Ω 。

1.2" 静电放电模型的建立

静电放电主要产生于物体接触过程中产生的电荷转移,本质是一种缓慢积累能量瞬间释放的过程,其特点为持续时间极短,瞬间电压极大,没有ESD防护措施,会瞬间损坏电子元件或者系统[17⁃18]。静电放电模拟器产生的静电放电参数有着国际标准。IEC61000⁃4⁃2标准是模拟操作人员或物体接触设备时产生的放电测试规范,该标准包含接触放电和空气放电两种测试方法。

本文模拟人体接触HDMI接口产生静电放电现象,故测试方法采用接触放电方法,直接在仿真软件搭建静电放电模拟器,对HDMI信号线进行放电电击,其静电放电模拟器应满足IEC61000⁃4⁃2标准[19]。基本指标如表1所示。

表中:Im表示最大电流;tr表示上升时间;I30 ns表示30 ns时电流;I60 ns表示60 ns时电流。

本文采用电路仿真模型的建模方法搭建静电放电电路模型,以便后续将该电路模型转化为SPICE电路仿真代码,并引入板级仿真软件来验证TVS高频模型的合理性。从人体⁃金属ESD电流波形标准出发,基于ADS (Advanced Design System)平台搭建了如图2所示的三电容电路模型[20]。该模型的特点就是通过C2、C3、C4三个自带初始电压的电容在不同的时间点进行放电,模拟IEC61000⁃4⁃2标准下的电流特征。其输出电流能够很好地满足IEC61000⁃4⁃2标准的静电放电电流波形参数,且在上升时间和峰值电流误差方面也有很好的表现。

在ADS平台上搭建了模型并进行仿真测试,模拟标准放电电压4 kV的ESD枪,其仿真电流波形如图3所示。图中,瞬态峰值出现在0.68 ns,最大电流达到15 A,且后续30 ns和60 ns时电流也满足IEC61000⁃4⁃2标准的ESD电流波形参数(分别达到了8 A和4 A),上升时间和峰值电流误差范围在5%以内。仿真结果表明,该电路模型符合IEC61000⁃4⁃2标准。将三电容电路模型转化为SPICE电路仿真代码,联合Sigrity进行后续的PCB板级静电放电仿真以验证TVS高频模型的合理性。

1.3" TVS高频模型及静电放电模型仿真验证

HDMI总线传输速率最高可达18 Gb/s,在如此高速的信号传输中进行ESD保护,尤其需要考虑ESD保护器件的高频特性[21]。而上文搭建的TVS高频模型需要验证其在PCB板下对ESD仍有较好的静电保护效果。

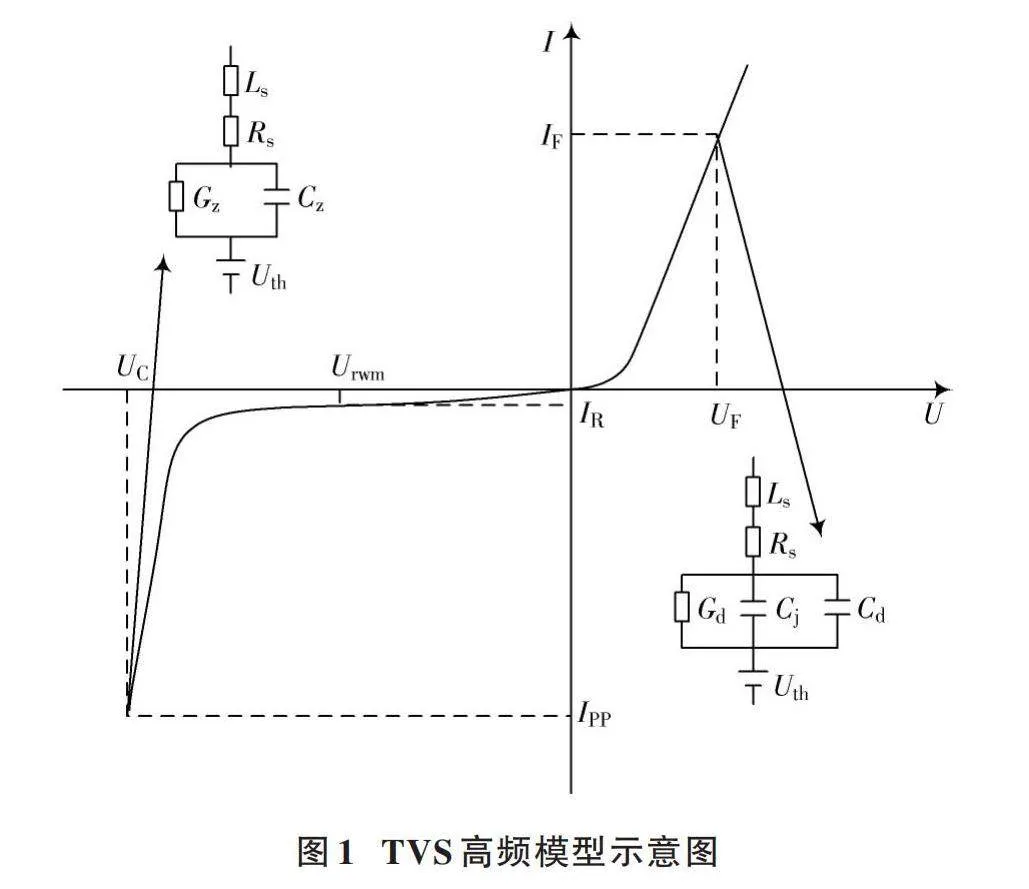

首先在Sigrity平台上加载静电放电枪SPICE模型。在PCB的HDMI接口上使用静电放电枪模型进行放电仿真,从而得到其信号线的电流波形,如图4所示。由图4可知,该电流波形基本与ADS仿真下的相同,证明在PCB板级电路中,不加任何ESD保护电路时会发生明显的静电放电现象,HDMI接口电路会产生一个7 A大小的瞬态大电流,对HDMI芯片与接口电路相连接的电路产生极大危害。

将TVS高频电路SPICE模型加入HDMI接口电路后,再进行静电放电仿真,得到未加TVS时HDMI信号线电压和加了TVS保护电路的HDMI信号线电压,如图5所示。当HMDI信号线未加TVS二极管保护时,瞬态电压在0.24 ns处达到最高14.8 V左右,远远大于HDMI信号高电平电压5 V;而在加了TVS保护电路后最高瞬态电压下降到6.3 V,最终电源在30 ns处基本稳定在5 V。可见,该TVS高频电路模型对标准静电放电现象有着良好的抑制效果,基本使得静电噪声达到可控的程度。

上述仿真结果表明,该TVS高频电路模型能较好地模拟TVS器件的电气特性,在正常情况下对ESD有较好的抑制效果,且保留了TVS的高频特性,为后续研究TVS保护电路对HDMI差分信号完整性影响提供支撑。

2" TVS空间布局仿真分析

一般而言,常见的HDMI驱动芯片的ESD保护较弱,需要外接ESD保护电路达到ESD保护的作用,但是保护器件带来的寄生特性和空间特性会影响信号质量,尤其是HDMI接口的高速差分信号。ESD保护器件的寄生特性是由其物理结构决定,难以对其进行优化;而由ESD保护器件的空间特性带来的不良影响却可以通过仿真分析进行优化设计,将其降至最低。通过分析不同空间布局的差分信号在频域下的S参数,可以知道哪种空间布局最优,能够有效地提高系统稳定性[22⁃23]。

本文以TVS管接入差分信号线的旋转角度和TVS管错开的距离为变量,在保证其他参数不变的情况下,设计了29套板级系统进行高频段S参数仿真,研究TVS管的空间布局对高速差分信号完整性的影响。最后再从中选取3种最具代表性的空间布局进行S参数仿真和眼图分析。

在差分信号线左右两侧各接入一个TVS管,以正上方为起始点,步长45°进行旋转,得到0°、45°、90°、135°、180°五种旋转角度,左右两侧共25种空间布局进行S参数仿真。以主流的1 920×1 080像素视频传输频率为例,36位真彩色,120 Hz刷新率,HDMI单通道传输一个RGB位,故单通道传输频率是总传输频率的[13],即1 920×1 080×36×120÷3=2.78 GHz。旋转角度影响最大的是回波损耗,其25种空间布局下的回波损耗三维图如图6所示。

图6中,旋转角度最大值为180°时,回波损耗为-14.2 dB,旋转角度最小值为90°时,回波损耗为-21.8 dB,最终体现在回波损耗性能提升239.1%,反射损耗值由19.3%下降到8%。

以两侧TVS管向外旋转90°为基础布局,并以两侧TVS管的水平中心错开距离为变量进行S参数仿真,错开距离分别为0 mil、22 mil、44 mil、66 mil。仿真S参数如图7所示。由图可以看出来S参数基本没有较大的变化,即在2.78 GHz频段处,TVS管空间布局在错开距离方面对信号完整性的影响较小,基本忽略不计。

为了给PCB设计者提供合理高效的参考设计,从上面29种不同空间布局中选取3种最具代表性的布局进行全频段S参数仿真和眼图分析,将TVS管空间布局分为三类,即:垂直型排布(旋转角0°)、水平型排布(旋转角90°)、错开型排布(错开距离44 mil),如图8所示。

TVS高频模型下,3种不同空间布局的传输线S参数如图9所示。以2K视频传输的标准频率点2.78 GHz为参考,垂直型、水平型、错开型排布回波损耗分别为-23.2 dB、-15.3 dB、-15.6 dB,垂直型排布相较于另外两种排布,回波损耗降低了248.1%。而3种排布下的插入损耗值分别为垂直型-2.1 dB、水平型-3.7 dB和错开型-3.5 dB。垂直型相比于水平型和错开型在标准频率点下传输性能更好,相比于后两者插入损耗分别降低了20.6%和18.5%。最后近端串扰值分别为垂直型-71.2 dB、水平型-46.4 dB和错开型-45.9 dB,三者的串扰值相较于传输值占比不到0.5%,对于信号完整性影响忽略不计。

为了研究空间布局在其他常见频段的S参数情况,以4K视频分辨率进行计算分析,分辨率频率为3 840×2 160×24×60÷3=3.7 GHz,垂直型、水平型、错开型排布回波损耗分别为-17.3 dB、-9.8 dB、-11.9 dB,垂直型排布相较于另外两种排布回波损耗分别降低了238%、186%。而3种排布的插入损耗值分别为垂直型-4.3 dB、水平型-6.4 dB和错开型-5.1 dB,垂直型的插入损耗相较于后两者分别降低了27%、10%。最后垂直型的串扰值仅占比传输值的4%,而其他两种布局不足1%。相较于回波损耗对信号完整性的影响,串扰值对信号完整性的影响可忽略不计。

将从Sigrity平台得到的三种空间布局S参数导入ADS进行联合仿真,以主流2K视频传输的标准频率2.78 GHz为例,得到对应三种空间布局的眼图。从图10所示的三种不同的空间排布眼图可以看到,错开型排布的眼图电压噪声的信噪比达到了6.2 dB,另外两者基本没有噪声。垂直、水平、错开三种排布的眼宽和眼高分别是175 ps、159 ps、164 ps和1.92 V、1.90 V、1.85 V,可以看出垂直型排布下的眼图展开更大且眼图跳变沿的交叉点更为集中,占空比上下区域比例更为对称,最终呈现的传输效果最好。

3" 结" 语

为了解决HDMI使用TVS进行静电保护时会对信号完整性产生破坏的问题,本文考虑了TVS高频特性影响,搭建了TVS高频电路模型并对其ESD抑制性能进行了验证。再从TVS高频模型的空间布局层次进行研究分析,以旋转角度和错开距离为变量,设计了29种不同的空间布局进行S参数仿真,从中选取了3种最具有代表性的TVS空间布局,并对其S参数和眼图进行仿真分析。仿真结果表明,在该高频模型下3种空间布局以垂直型排布信号参数性能最好,相较于其他两种布局,回波损耗降低了248.1%,插入损耗降低了20.6%和18.5%;也表明垂直型排布眼图的信噪比、眼宽、眼高也优于另外两种布局。表明在设计HDMI的TVS静电放电保护电路时,采用垂直型空间布局可以有效减少对高速差分信号的完整性破坏,为TVS静电保护电路研究提供了可靠的高频模型,改善了HDMI差分信号完整性思路,在静电放电和差分信号完整性研究领域具一定的应用价值。

参考文献

[1] 桑健,赵阳,高翔,等.基于结构处理的电子设备ESD防护方法研究[J].南京师范大学学报(工程技术版),2017,17(4):1⁃6.

[2]" 段乐妮.用于存储器接口的ESD研究与设计[D].西安:西安电子科技大学,2020.

[3] PANDEY A K. SI⁃PI analysis and compliance test of HDMI 1.4 b serial channel with IBIS⁃AMI [C]// 2016 IEEE 25th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS). [S.l.]: IEEE, 2016: 71⁃74.

[4] LIN H N, HUANG J Y, HUANG Y C, et al. Analysis of PCB return path configuration effect on Transient ESD Suppression [C]// 2019 Joint International Symposium on Electromagnetic Compatibility, Sapporo and Asia⁃Pacific International Symposium on Electromagnetic Compatibility. [S.l.]: IEEE, 2019: 214⁃217.

[5] KUZNETSOV V, KECHIEV L. Charged board model ESD simulation for PCB mounted MOS transistors [J]. IEEE transactions on electromagnetic compatibility, 2015, 57(5): 947⁃954.

[6] HUANG Y C, WU T L, CHEN C H. Investigation of signal integrity issues in multi⁃path electrostatic discharge protection device [C]// IEEE Symposium on Electromagnetic Compatibility amp; Signal Integrity. Santa Clara, CA, USA: IEEE, 2015: 187⁃192.

[7] 李搏,李健壮,干旭春,等.一种系统级封装的ESD保护技术[J].微电子学,2021,51(2):211⁃215.

[8] 耿建平,何学良.高清多媒体接口的静电放电保护设计[J].测控技术,2012,31(11):127⁃130.

[9] 周智勇.用于确保信号完整性的ESD保护器件新结构[J].电子产品世界,2009,16(12):58⁃60.

[10] 黄庆敏,罗键.HDMI接口标准及应用设计[J].电视技术,2007(2):32⁃34.

[11] 潘廷哲,张国钢,徐由档,等.多路高速同步数据采集系统的信号完整性仿真与优化设计[J].电测与仪表,2020,57(1):136⁃140.

[12] 吕卫民,胡冬,马静华,等.考虑寄生参数的集成电路ESD损伤仿真方法[J].北京航空航天大学学报,2011,37(9):1100⁃1104.

[13] 陈强,徐可,陈真真,等.基于TLP建模的系统级静电放电效应仿真[J].强激光与粒子束,2019,31(10):51⁃54.

[14] 刘素玲,段平光,李霞,等.静电放电模拟器电路建模分析[J].电波科学学报,2009,24(6):1172⁃1176.

[15] WONG S, HU C, CHAN S. SPICE" macro model for the simulation of zener" diode" current⁃voltage characteristics [J]. IEEE circuits and devices magazine, 1991, 7(4): 9⁃12.

[16] 罗广孝,崔翔,张卫东,等.TVS静电抑制器等效电路参数估算及应用[J].中国电机工程学报,2013,33(16):204⁃211.

[17] KER M D, HSIAO Y W. On⁃chip ESD protection strategies for RF circuits in CMOS technology [C]// 2006 8th International Conference on Solid⁃State and Integrated Circuit Technology Proceedings. Shanghai: IEEE, 2023: 17⁃21.

[18] LIN L, WANG X, TANG H, et al. Whole⁃chip ESD protection design verification by CAD [C]// 2015 28th IEEE International System⁃on⁃Chip Conference (SOCC). Beijing: IEEE, 2009: 1680⁃1683.

[19] 舒晓榕,徐晓英,刘鹏宇,等.ESD模拟器全波模型的仿真与验证[J].自动化与仪表,2019,34(7):73⁃79.

[20] 芦俊.静电发生器电路级仿真模型的建立及验证[D].湘潭:湘潭大学,2020.

[21] 严传高,张乘浩,刘马良,等.HDMI高速显示数据接口技术[J].微纳电子与智能制造,2020,2(2):105⁃111.

[22] 王楚哲,苏成悦,李增,等.基于Sigrity在SDIO板级信号完整性仿真分析与优化[J].计算机测量与控制,2022,30(3):204⁃210.

[23] 李俊杰,曹旭东,梁华庆,等.HDMI高清音视频系统的高速PCB的研究及实现[J].电视技术,2016,40(12):34⁃39.

作者简介:王" 淼(1999—),女,江苏徐州人,硕士研究生,研究方向为电子与信息器件、电路信号完整性分析。

李嘉豪(1999—),男,湖南人,硕士研究生,研究方向为植物表型设备研发。

汤" 浩(1995—),男,贵州遵义人,博士研究生,研究方向为生物传感器研发及生物特征信息提取。

郭" 亚(1977—),男,安徽人,博士,教授,博士生导师,研究方向为系统建模与控制、大数据分析、传感器与仪器。