基于FPGA的信号调制方式识别和参数估计设计

摘 要:调制是各种通信系统的重要基础,广泛应用于广播、电视、雷达、测量仪等领域,在频谱搬移的过程当中起着重要作用。文章基于STM32F407单片机和FPGA芯片的信号处理方式进行研究,设计一款高性能、高精度、低成本、运算速度快的信号调制方式识别和参数估计装置。根据实验测试,该装置可测量信号频率为1~30 kHz,幅度为30~100 mV,解调显示调制系数误差约为0.01,调制信号频率约为50 Hz,最大频偏在200 Hz左右。该信号装置能够精确获得测量结果,提高了信息传输速率和正确率。

关键词:STM32F407;信号调制解调;AD模数转换

中图分类号:TN911.7;TN79+2 文献标识码:A 文章编号:2096-4706(2024)13-0019-06

Design of Signal Modulation Method Identification and Parameter Estimation Based on FPGA

NIE Chen, YU Jiangnan, PAN Xiaoqin

(School of Information and Electromechanical Engineering, Shaoxing University Yuanpei College, Shaoxing 312000, China)

Abstract: Modulation is an important foundation of various communication systems and is widely used in fields such as broadcasting, television, radar, and measuring instruments. It plays an important role in the process of spectrum shifting. This paper studies the signal processing method based on STM32F407 single-chip microcomputer and FPGA chip, and designs a high-performance, high-precision, low-cost, and fast computing speed signal modulation method identification and parameter estimation device. According to experimental testing, the device can measure signal frequencies ranging from 1 to 30 kHz and amplitudes ranging from 30 to 100 mV. The demodulation display modulation coefficient of about 0.01, a modulation signal frequency of about 0.05, and a maximum frequency deviation of about 200 Hz. This signal device can accurately obtain measurement results, improving information transmission rate and accuracy.

Keywords: STM32F407; signal modulation and demodulation; AD analog-to-digital conversion

0 引 言

利用传统的模拟电路来识别多种调制信号和调制参数,以及对不同类型的调制信号进行实时解调且解决解调信号不固定问题,实现的可能性比较小。因而本文基于STM32F407单片机、FPGA芯片、ARM板,以及高速AD与DA设计一种混合系统,可有效地实现对所传信号的类型进行判断、解调以及相应的参数运算。其中,FPGA信号处理器主要完成信号采集、抽取滤波、模拟数字调制信号解调(包括载波同步)等;嵌入式处理器(STM32F407)主要完成调制类型识别和调制参数计算,结果在串口液晶上显示;ARM板作为STM32F407的运行环境;高速AD与DA用于信号采集和模拟解调信号恢复,数字解调信号直接从FPGA的IO口输出。通过连接Wi-Fi模块和串口屏实现人机交互,相较于传统模拟电路设计,该装置更具有高效性和实用性。

1 系统设计分析

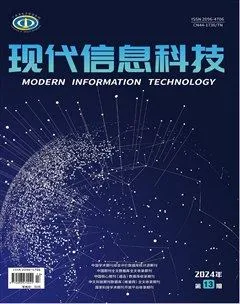

本系统主要由硬件电路和软件设计两部分组成。硬件电路包括LMH6643运算放大器、ADC08200模数转换器、FPGA信号处理模块和数模转换电路。硬件电路主要将输入信号经过处理采集,送入FPGA信号处理器后判断信号类型并计算信号调制度及解调原波形。软件设计通过对信号进行下变频、降采样、滤波等数字信号处理,将数据送到ARM单元进行算法处理,根据判断的信号类型和参数,将结果输出到显示单元(液晶显示屏)进行显示。系统整体框架如图1所示。

本系统原理过程:将外界的输入信号送入调理电路,由LMH6643运算放大器将输入小信号进行放大(频率范围:1~30 kHz,幅度范围:30~100 mV)。由于ADC08200要求模拟输入必须是直流信号,因此需在调理电路当中进行交直流变换。使其符合AD采集的动态范围要求,以进行数据采集。将AD采集后的信号送入FPGA,由于载波频率为2 MHz,对后续的数字信号处理要求较高(如FFT等),因此先对信号进行下变频、降采样、滤波等数字信号处理。降采样后,信号整体频段搬移到低频段,采样率降低到512 kHz后将数据送到ARM单元进行算法处理,再送到后续的解调单元等待解调。ARM单元根据算法计算的结果,结合经优化的零中心归一化瞬时幅度谱密度算法以及其他频谱特征,分析当前信号类型(AM、FM、CW、ASK、FSK或PSK),将结果送给FPGA的解调单元,STM32F407接收FPGA发来的测量数据和解调数据,判断信号类型并进行模拟或数字解调,用STM32F407的片内DA输出解调数据,数字解调信号直接从FPGA的IO口输出。ARM单元根据信号处理结果、分析得到的信号类型,以及解调的信号幅度、电平等结果,计算得到AM的调制度或者FM的调频度及最大频偏,以及ASK、FSK、PSK的解调基带速率等参数;根据判断的信号类型和参数,将结果输出到显示单元(液晶显示屏)进行显示。

交直流变换放大的选择:若采用整流器和放大器,只会得到幅度而失去相位信息;若使用三极管和放大器,由于信号经过检波,只有正交变波,也会丢失一半相位信息;而采用运放,则先通过放大器,通过在另一端加直流电压源,将信号的幅值抬高加入负反馈,使其整体信号幅值都大于0,同时完成交直流转换和放大任务。使其满足A/D转换模块的输入要求和分辨率要求。此方法不会造成信号的相位信息丢失,但对于放大器的转换速率需求较高。

2 硬件电路分析

2.1 调理电路设计

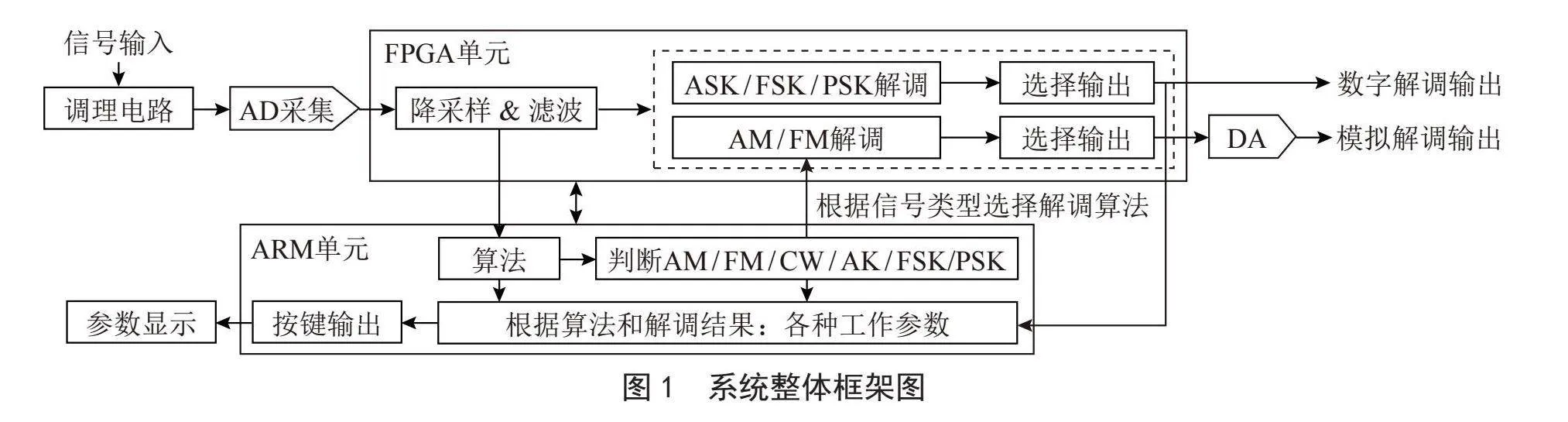

该电路使用LMH6643MA作为运放,其最小转化速率为90 V/μs,不仅满足题目要求,同时增益带宽也得到了放大。本单元为单电源供电,因此将输入信号增加一个直流电平使其成为直流信号。如图2所示。

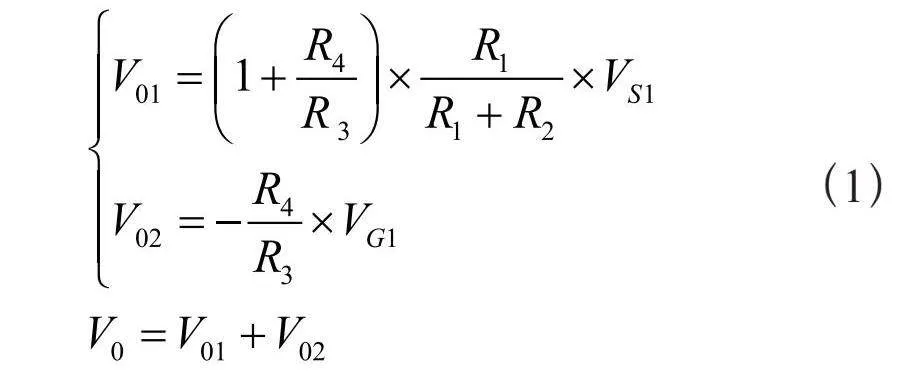

由于电压抬高需将其变成直流信号,整合后反相放大负反馈运算放大器的放大计算式[1]如下:

式中,VS1表示用于抬高的直流电压,VG1表示输入信号的电压;对于二级放大同理。由于信号放大后接入AD模块ADC08200,为了满足ADC08200的输入规格和分辨率要求,对其放大的倍数有所要求,V0要在(-0.3 V,3.8 V)之间调整放大倍数和抬高电压[2]。

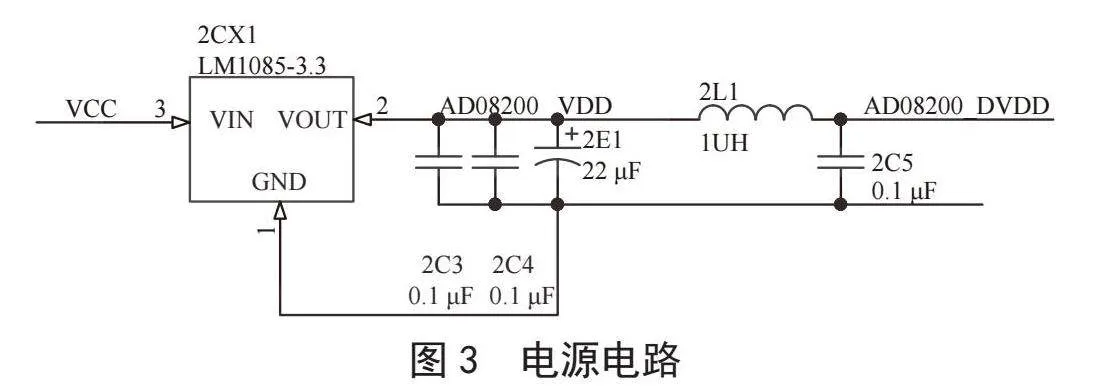

2.2 ADC08200模数转换电路

该电路为电源电路,其中LM1085将5 V电压转换为3.3 V,给ADC08200的模拟部分提供电源,经过电感隔离后给其数字部分提供电源。其中电感隔离是模拟电源和数字电源之间隔离,防止数字电源对模拟电源干扰,该电路提高了系统的稳定性。为提高信号的准确性,加入电容进行滤波去除多余的噪声,经过整形后方便频率采集,电路如图3所示。

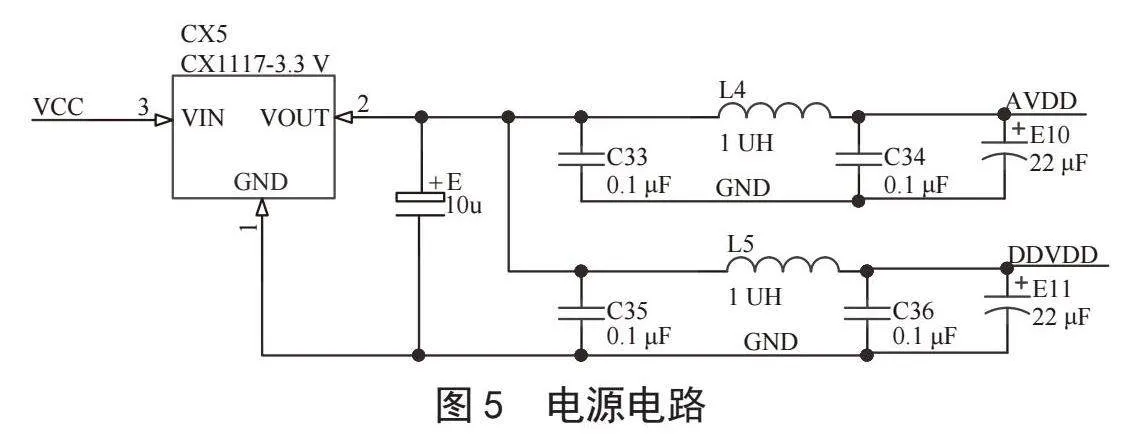

选用ADC08200模数转换芯片将输入模拟信号转换为数字信号供FPGA作信号处理,此设计是在载波频率为2 MHz的情况下,确保有足够的采样率,对kHz级别的模拟信号进行读取和采样。其中VIN+为输入的模拟信号,在0~2.5 V范围,会被转换为8 bit。转换结果通过DA0~DA7输出。ADCCLK脚为转换器时钟控制脚,由FPGA控制转换速率,如图4所示。

2.3 FPGA信号处理模块

首先需对输入信号进行频域变换,去除原高频载波对信号的影响,进而得到调制信号。由于对后续的数字信号处理要求较高(如FFT等),故得到ADC08200输出转化的信号数据后,先对信号进行下变频、降采样、滤波等数字信号处理。通过FPGA计算信号频率,根据频率计结果产生适合的本地载波与采集到的数据混频,混频后整体信号搬移至低频段,降低信号采样率至512 kHz。得到相近的频率的本地载波为2 MHz,再将输入信号和本地载波经过一个乘法电路进行运算,正弦波的公式为[3-4]:

过低通滤波器过滤掉高频的cos(X + Y)后,剩下的cos(X - Y)相较于原信号是进行了降频处理,得到了低频信号。后续可进行降采样处理,将采样频率降低到512 kHz [5]。

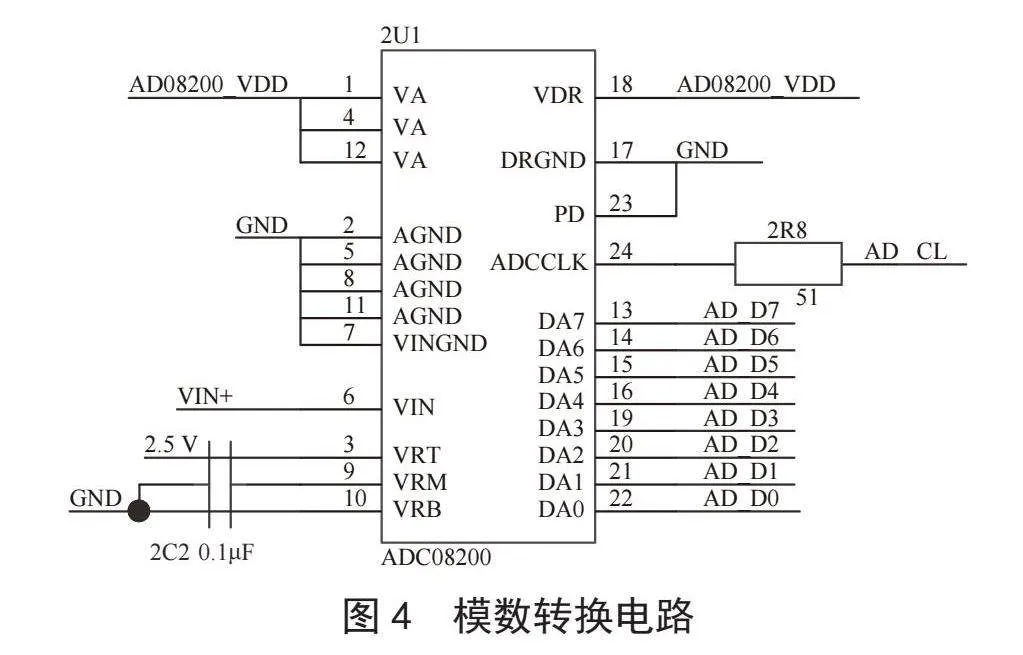

2.4 数模转换电路

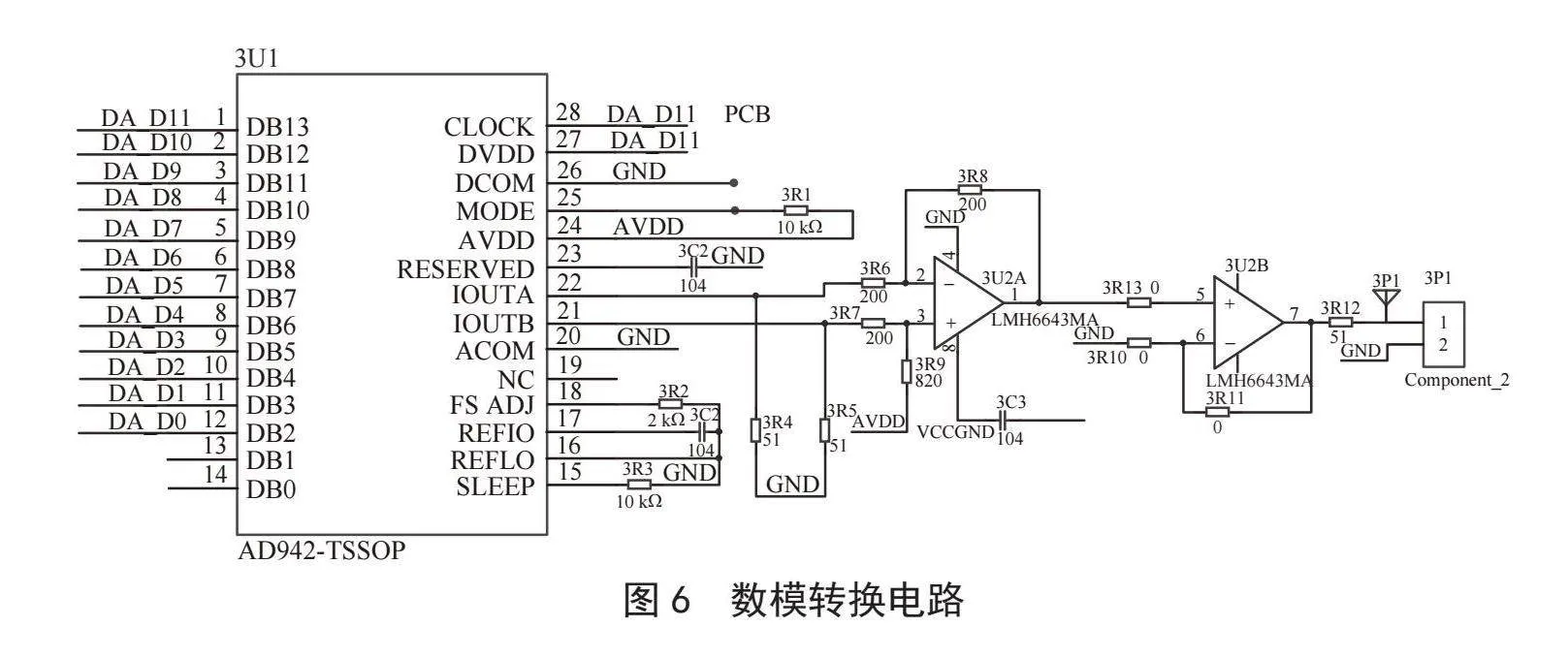

电源电路中CX1117将5 V电压转为3.3 V,给AD9742芯片的数字部分提供电源,通过电感隔离后给AD9742的模拟部分提供电源,如图5所示。

本装置选用AD9742(12位分辨率)芯片接收解调数据,其转换速率都高达210 MS/s,完全满足分离模拟信号的带宽要求。DACLK脚为转换器时钟控制脚,由FPGA控制其转换速率。将模拟到的数字信号通过该芯片转为模拟信号,经过后部分由LMH6643比例放大器放大,得到所需的模拟信号,如图6所示。

采用STM32F407芯片接收FPGA发来的测量数据和解调数据,STM32进行频谱分析判断其类型。时域上,AM信号在时域上具有直流信号的特点,而FM信号和CW信号的波形无明显的特点,均为正弦波导致不易区分。频域上,AM信号的波形仅在中心频率和两个边带上有峰值;CW信号的波形仅在中心频率上有峰值;由于FM调频相当于将中心频率的峰值分散给多个边带,故FM信号的波形在多个边带上有峰值。最后通过IO口输出,在液晶显示屏上显示信号调制类型及其调制参数[6]。

基于上述特性,降频后的测试信号可以被主控芯片处理,将得到的信号数据经过FFT运算结合优化的零中心归一化瞬时幅度之谱密度算法,则可判断信号的类型并将结果送给FPGA的解调单元,让其根据信号类型进行解调,解调后将数据传输给主控芯片进行DA转换,进而输出解调波形。同时主控芯片根据得到的解调信息如信号幅值、电平等结合FFT结果,计算得到对应信号种类的调制度和参数。再将其与调制类型一并输给显示模块进行显示。

3 软件设计分析

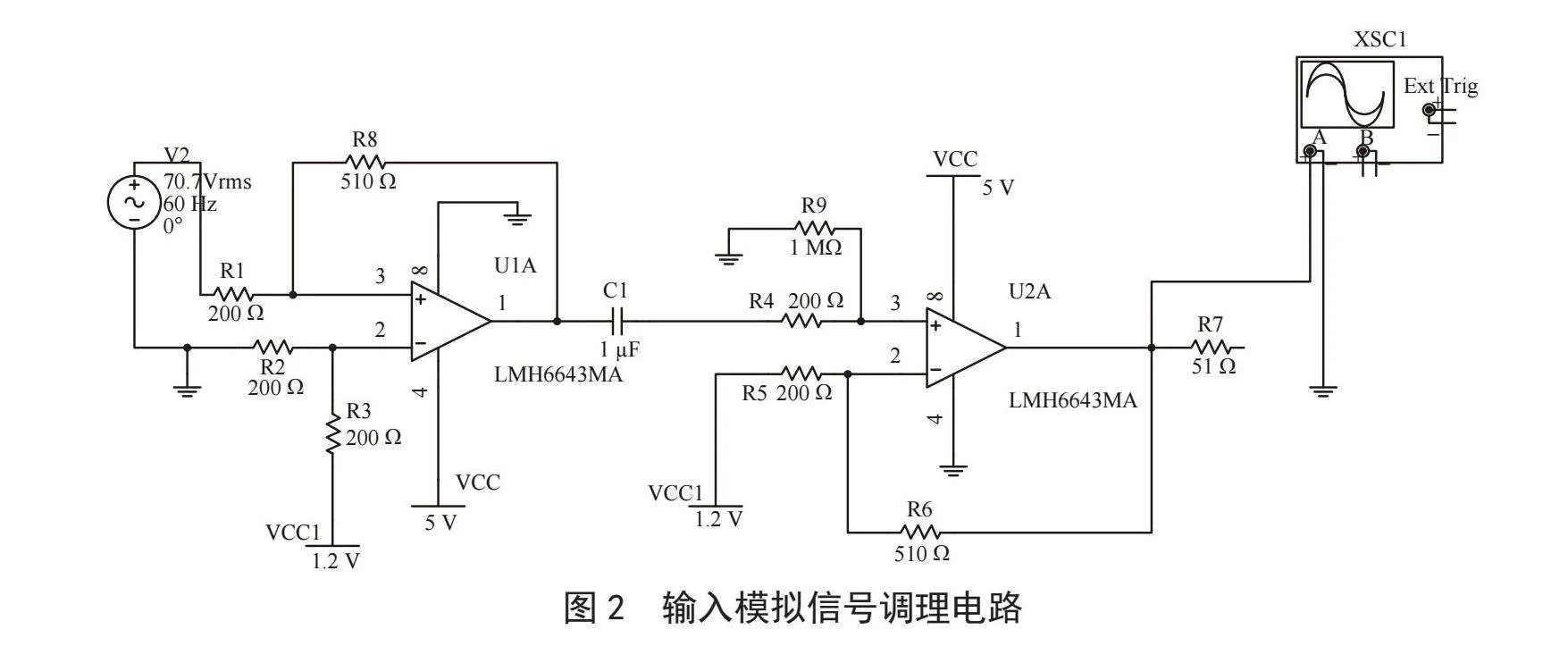

软件设计部分是将在硬件电路中采样、滤波后的信号做算法处理,过软件算法完成调制信号识别、调制度测量、信号解调与参数计算等功能。具体流程如图7所示。

3.1 调制信号识别

将AD采集后的信号送入FPGA后计算信号频率,根据频率计控制NCO产生本地载波,经过混频后,信号整体搬移到载波至低频段,降低了信号的采样率后滤波,送到ARM单元作FFT运算。

3.2 调制度测量

ARM单元根据FFT结果,分析得到的信号类型,解调的信号幅度、电平等结果,计算得到AM的调制度或者FM的调频度及最大频偏,以及ASK、FSK、PSK的解调基带速率等参数。

3.3 信号解调与参数计算

STM32通过FFT运算结果和零中心归一化瞬时幅度之谱密度算法[7]并判断信号类型后,将信号类型记录下并反馈给FPGA,使其进行相应信号的相干解调。解调完成后,通过FPGA传输解调数据至STM32。再以DA方式进行转换,将解调波输出;同时对信息进行计算,得到对应的调制度和参数[8],再与信号类型一同输出给显示模块显示。

3.4 显示屏部分

采用STM32F407芯片来接收FPGA发来的测量数据和解调数据,用STM32进行频谱分析判断其类型,通过IO口输出,在液晶显示屏上显示信号调制类型及其调制参数[9],同时AD9742芯片接收解调数据,进行数模转换后在示波器上显示解调波形。

4 测试结果与分析

4.1 实际电路对比分析

载波频率为2 MHz,电压峰峰值为100 mV,要求:1)AM调制频率为1 kHz,调制深度为30%;

2)FM调制频率为5 kHz,偏移程度为5 kHz;3)未知调制方式下,自主识别;4)ASK/PSK二进制码速率Rc设为3 kHz;5)FSK二进制码速率设为5 kHz。

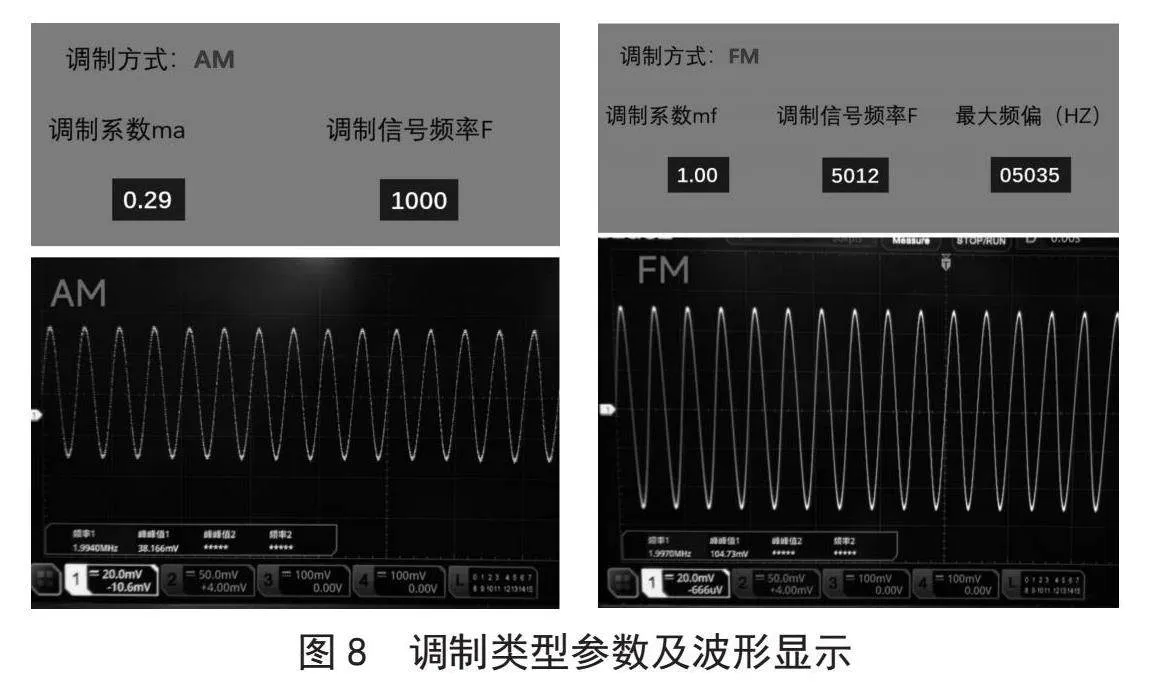

在实验操作过程当中,已有多组实验结果验证了本系统的可行性。按照研究要求,设置载频为2 MHz,峰峰值为100 mV。AM调制频率为1 kHz、调制深度为30%;其显示结果为1 kHz,调幅系数0.29,误差绝对值小于0.1,满足测量要求[10]。FM调制频率为5 kHz、偏移程度为5 kHz;其显示结果为调幅系数1.00,调制信号频率5 012 Hz,误差小于50 Hz,最大频偏5 035 Hz,误差小于300 Hz,调制类型参数及波形显示如图8所示。

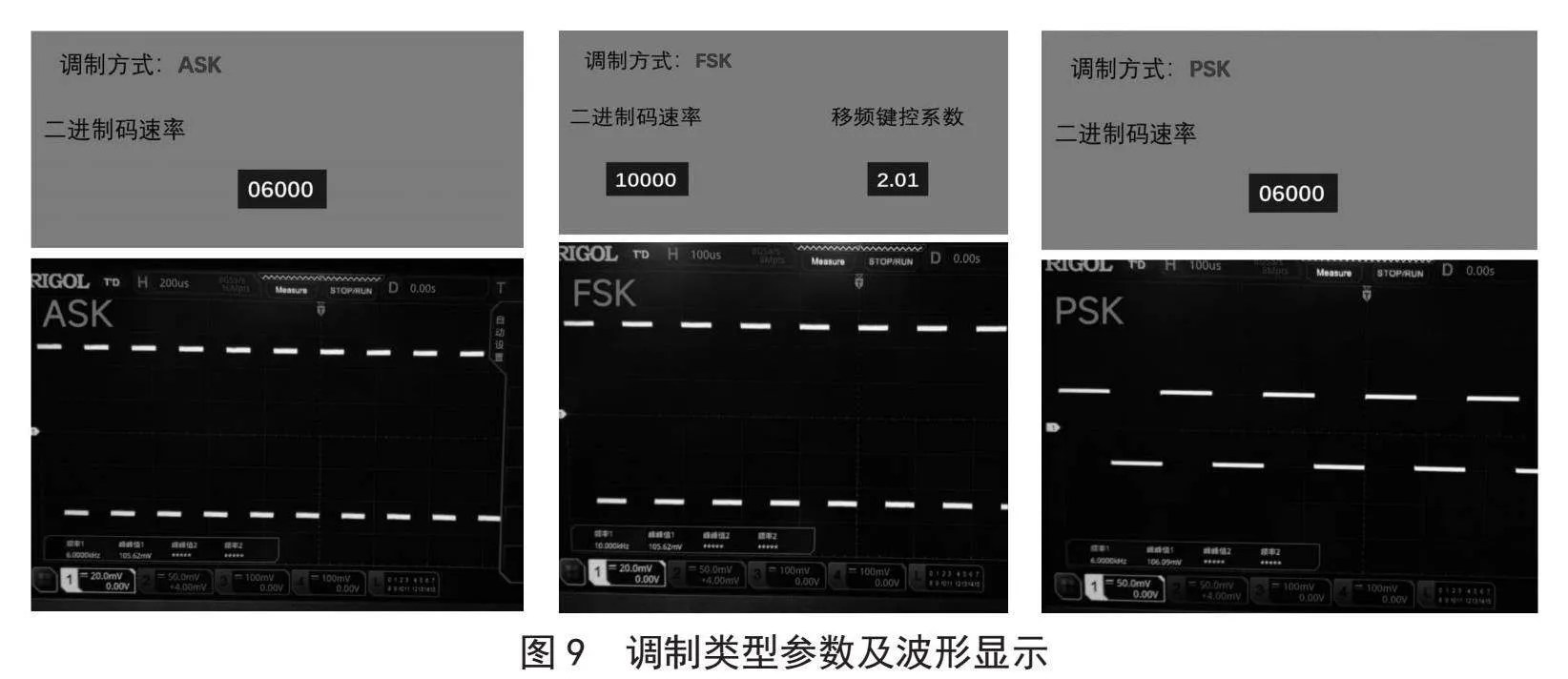

ASK/PSK调制频率为3 kHz [11],其显示结果二进制码速率为6 kHz并显示方波[12];FSK二进制码速率设为5 kHz,其显示结果二进制码速率为10 kHz并显示方波,如图9所示。

4.2 测量数据分析

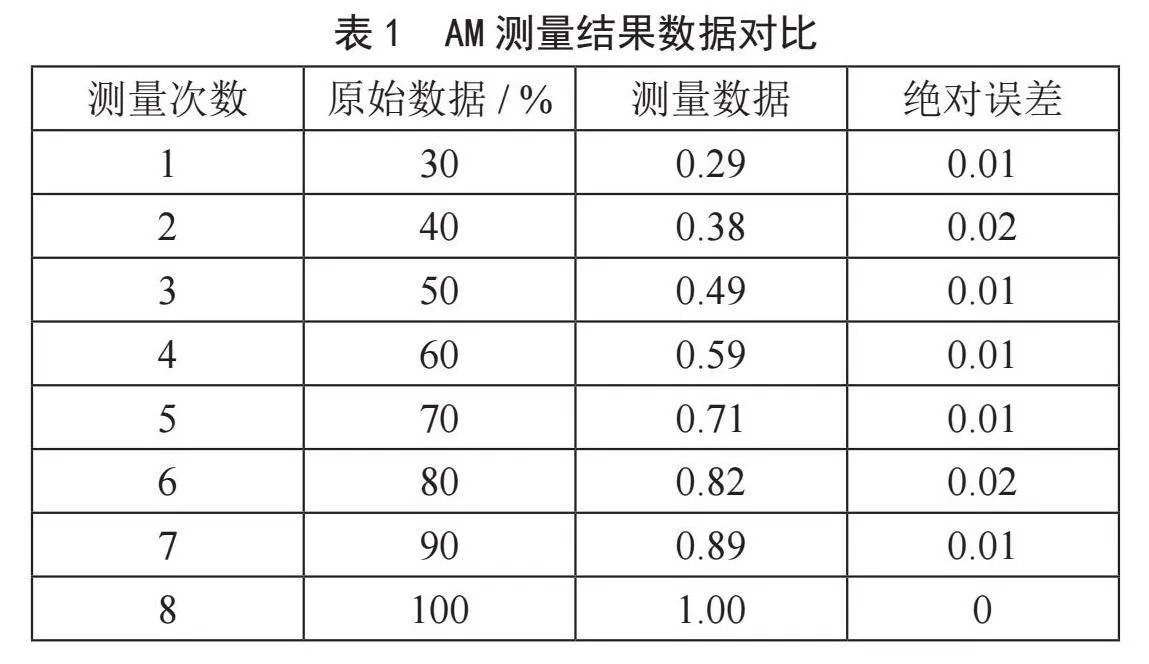

4.2.1 AM测量数据

AM信号(含载频分量的双边带调幅信号),载波电压峰峰值Vpp = 100 mV,载频fc = 2 MHz,其正弦调制信号频率F = 1 kHz,调制深度为30%~100%。根据测量结果表明,其显示值与信号发生器设置值的误差的绝对值小于0.1,可正确显示AM正弦波形图,测量数据正确,符合设计要求,如表1所示。

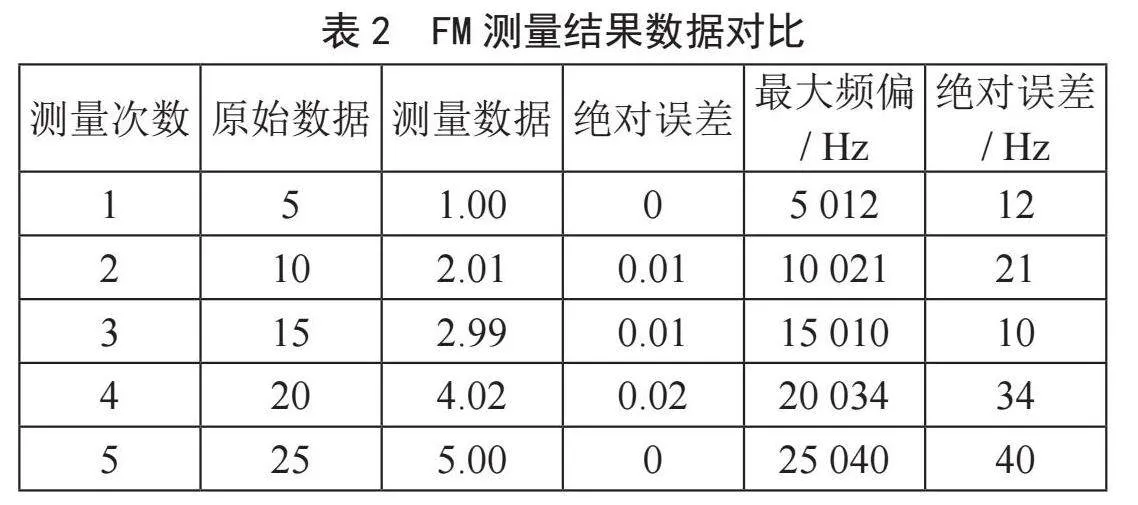

4.2.2 FM测量数据

FM信号,调制频率为5 kHz,偏移程度为5 kHz。载波电压峰峰值Vpp = 100 mV,载频fc = 2 MHz,其正弦调制信号频率F = 5 kHz,调频系数为1~5。测量结果表明,调频系数显示值与信号发生器设置值的误差的绝对值小于0.3;调制信号频率显示值与信号发生器设置值的误差的绝对值小于50 Hz;最大频偏显示值与信号发生器设置值的误差的绝对值小于300 Hz,可正确显示FM正弦波形图,测量数据正确,符合设计要求,如表2所示。

4.2.3 CW测量

未知调制方式下,自主识别为CW,符合设计要求。

4.2.4 ASK、FSK、PSK测量数据

由信号发生器产生的信号AS、FSK、PSK,设二进制码速率Rc为3、4、5 kHz时,产生的速率Rc分别为6、8、10 kbit/s,对比表3的测量数据,设置值与显示值之间的误差在±0.02左右,FSK二进制码速率设为5 kHz,由于移频键控系数h ∈ [2,5],因此设为2,根据相关公式h = (| fc1 - fc0 |) / Rc,可设跳跃频率fc1为2.01。显示二进制码速率为10 kHz,移频键控系数为2.01,可正确显示ASK、FSK、PSK方波,测量数据正确,符合设计要求。不同码数率如表3所示。

通过以上实验数据可知,该装置虽存在一定的误差,但误差范围都只在0.02%左右,实验结果表明测量装置可高精度地任意计算测量值及输出波形。该装置操作简单、精确度高、高性能等优势,可广泛应用于信号调制方式识别和参数估计等方面,具有较强的实用价值[13]。同时为测量仪器提供商业应用。

5 结 论

本文设计了基于STM32F407单片机和EP4CE22E22A7系FPGA的信号调制方式识别和参数估计装置,经过测试表明,该装置各项参数指标测试模块均表现出了优秀性能。相较于传统模拟电路,该装置不仅具高性能、高精度、运算速度快的优势,还实现了人机交互,能更好地满足信号调试需求。

参考文献:

[1] 王瑞.调频信号调制识别与参数估计算法研究 [D].西安:西安电子科技大学,2019.

[2] 王永志.数字调制信号的参数估计与调制识别技术的研究 [D].哈尔滨:哈尔滨工程大学,2019.

[3] 李伟.数字通信信号的自动识别与参数估计算法研究 [J].西安文理学院学报:自然科学版,2018,21(5):58-63.

[4] 张玉静.通信信号调制方式识别及参数估计 [D].北京:北京邮电大学,2016.

[5] 宋军,刘渝,王旭东.FSK/BPSK复合调制信号识别与参数估计 [J].电子与信息学报,2013,35(12):2868-2873.

[6] 张春杰,李娜.PSK信号的调制参数估计与识别 [J].应用科技,2013,40(5):40-43+47.

[7] 于显耀.数字调制信号调制识别及参数估计问题研究 [D].大连:大连理工大学,2013.

[8] 芦跃.数字信号调制识别及参数估计研究 [D].苏州:苏州大学,2013.

[9] 安金坤.通信信号调制方式识别与参数估计研究 [D].西安:西安电子科技大学,2011.

[10] 布刚刚.一种FM信号调制解调数字化实现方法研究 [J].现代导航,2021,12(4):306-309.

[11] 周志法,艾文,张尧琴.基于FPGA的2FSK数字信号调制解调 [J].电子科技,2012,25(3):121-123.

[12] 赵春.基于ARM-FPGA的BPSK调制解调无线通信系统设计与实现 [D].合肥:安徽大学,2021.

[13] 尹吉伦.基于FPGA的短波数字信号调制解调的应用 [D].大连:大连海事大学,2007.

作者简介:聂晨(2004.02—),女,汉族,四川南充人,本科在读,研究方向:信息的调制与解调。