0.8~2 GHz单比特接收机的设计

王玉红 秦睢睢 李兵

收稿日期:2023-08-29

DOI:10.19850/j.cnki.2096-4706.2024.06.013

摘 要:文章设计的单比特接收机能在0.8~2 GHz频率范围内对侦收的雷达信号进行快速测频,并输出频率、保宽脉冲等相关信息,从而快速引导干扰设备进行干扰。该单比特接收机将测频结果用于引导干扰源,具有频率测量和频率码连续输出、连续波判别、保宽脉冲输出和BIT自检等功能。单比特接收机的组成架构在满足瞬时宽带宽、高灵敏度和实时处理等主要性能指标的前提下,还具备各组成模块功能明确、控制独立、调试方便等优点。

关键词:0.8~2 GHz;单比特接收机;快速测频

中图分类号:TN851 文献标识码:A 文章编号:2096-4706(2024)06-0058-04

Design of 0.8~2 GHz Single Bit Receiver

WANG Yuhong, QIN Suisui, LI Bing

(Nanjing Aerospace Industry Technology Co., Ltd., Nanjing 210001, China)

Abstract: The single-bit receiver designed in this paper can quickly measure the frequency of the detected radar signal in the frequency range of 0.8 ~ 2 GHz, and output the frequency, wide pulse and other related information, so as to quickly guide interfering devices to interfere. This single-bit receiver uses the frequency measurement results to guide the interference source, and has functions such as frequency measurement and continuous output of frequency codes, continuous wave discrimination, wide pulse output, and BIT self-check. The composition architecture of a single-bit receiver not only meets the main performance indicators of instantaneous broadband, high sensitivity, and real-time processing, but also has the advantages of clear functions of each component module, independent control, and convenient debugging.

Keywords: 0.8~2 GHz; single-bit receiver; fast frequency measurement

0 引 言

傳统的IFM接收机组成简单、技术成熟、模块化程度高、体积小、成本较低廉,但工作灵敏度不高,同时到达信号适应能力较差,延迟线精度易受温度变化影响,带来通道出错或测频精度下降[1-3]。模拟信道化接收机具有与IFM接收机相同的截获概率和同等的测频精度,但工作灵敏度高于IFM接收机,其最大的优点是能测出同时到达信号的载频[4-6]。然而本文研究需要较大的瞬时带宽0.8~2 GHz,对于模拟信道化接收机来说,无论其设备量、体积、重量、造价都无法承受。单比特接收机最早由美国军方空军实验室AFRL提出,后来其他公司开发了各种类型的单比特接收机作为数字瞬时频率测量接收机[7],单比特接收机具有以下主要特点:测频精度高、瞬时带宽高、体积功耗小、全数字实现[8]。故本文设计的接收机选用单比特接收机体制实现。

1 单比特接收机的工作原理

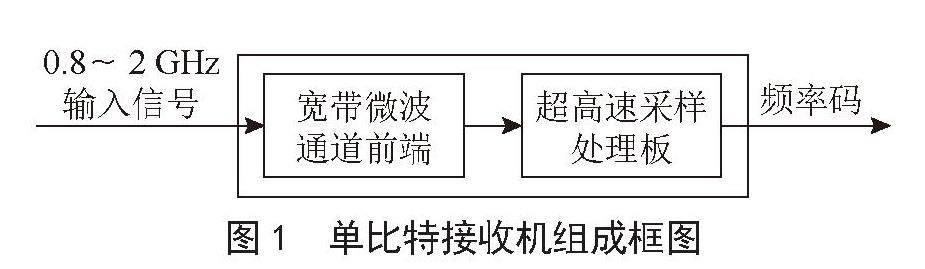

单比特接收机原理及实物组成框图如图1所示。

图1 单比特接收机组成框图

单比特接收机接收外部输入的0.8~2 GHz带宽的雷达射频信号,雷达射频信号进入单比特接收机后首先进入宽带微波通道前端,宽带微波通道前端的主要功能是实现将接收到的大动态范围的射频信号变换到超高速采样处理板采样模块所需要的量程范围。超高速采样处理板的主要功能是通过高效快速的数字信号处理算法和高速实时信号处理硬件平台,实现对射频信号的直接采样,完成对信号的快速实时测量,产生频率码和保宽脉冲等相关信息给后续引导设备[9]。

整个系统组成架构设计在满足瞬时宽带宽、高灵敏度和实时处理等主要性能指标的前提下,尽量做到各组成模块功能明确,控制独立,调试方便。

2 单比特接收机的设计

2.1 宽带微波通道前端

宽带微波通道前端设计的技术难点主要有两点。一是将大动态的射频信号压缩到一个恒定的电平范围内同时还要保证通道内信号杂散、交调没有明显恶化和低噪声。

为了保证系统的灵敏度和接收性能,必然要求整个微波接收前端内具有良好的幅频一致性、较低的杂散电平和较低的噪声系数[10]。对于超高速采样模块,其输入信号要求功率电平在-15~-5 dBm。而单比特接收机输入信号具有较大的动态范围,并且要达到较高的灵敏度,因此则需要输入信号压缩到一个恒定的电平范围内,还要保证小信号和大信号不失真,需要在较大增益前提下对大信号输入在宽带微波通道的性能进行详细设计。

在通道内采用多级放大的方式,通过合理分配各级放大器的增益和必要的衰减器来实现高性能的微波接收前端。

微波通道前端由多级放大器级联组成,在各级放大器间级联衰减芯片,增加电路稳定性,通过器件本身性能保证在高低温下的增益起伏,使输出功率在数字采样板的最佳工作范围内。

2.2 超高速采样处理板

本超高速采样处理板采用采样率为10 GS/s的超高速采样电路,输入射频信号通过高速ADC进行单比特量化后,得到数字量化信号输入到高速处理FPGA中进行信号检测和频率计算,得到结果通过接口芯片转换为TTL电平后输出。

本方案主要关键点在高速单比特量化、高速采样时钟产生和高速信号布局设计上,下面主要对这四个方面进行说明。

2.2.1 高速单比特量化

所选芯片采用GaAs工艺,可将1路高频模拟信号以1:16降速比输出16路LVDS低速数字信号。输出提供8分频及16分频时钟供数据同步。采样率可达14 GS/s,数据信号输入动态范围达34dBc适合高速数据信号的降速处理和数字化接收前端。

2.2.2 时钟芯片

时钟芯片的主要功能是根据输入的160 MHz晶振信号产生高速单比特ADC所需要的采样时钟,单比特ADC所需要的单比特采样时钟信号的频率是

5.12 GHz,设计采用的高速锁相环PLL芯片ADF4355。

VCO相位噪声性能对整体系统性能起着关键作用,它可以提供稳定的高精度的频率信号,故选择合适的PLL频率合成器是系统设计的重要考虑。ADI公司的ADF4355宽带PLLVCO频率合成器完全满足应用中对压控振荡器相位噪声的严格要求,可以确保相位噪声尽可能低,扩展频率范围,缩小尺寸,扩大工作温度范围,从而降低风险。

2.2.3 电源设计

电源部分主要包括FPGA和高速ADC芯片的供电。

FPGA的供电主要包括FP_VCC_1P0V 、FP_VCC_1P8V、FP_VCC_2P5V、FP_VCC_3P3V四种电压,采用2片LT4630A供电。LT4630A每一路电源的最大输出电流为18 A,输出电压可调,足够保证FPGA的正常工作。

2.2.4 高速信号布局与设计

10 GS/s的采样率使得时钟和信号分布路径的走线不能再按照集总参数电路的方法来处理,而应该考虑到其传输线效应、时钟和信号分布电路相互之间的干扰以及其与其他片上关键信号路径之间的干扰,即信号完整性问题。超高速采样技术必须在有效的电磁仿真和实测数据联合仿真分析的前提下进行。

超高速采样处理板采取了对高速数据线“加扰”的方式,来避免数据线的长“1”、长“0”状态,进而压缩数据线带宽,保证数据眼图张开。产生与采样时钟同源且固定在某一速率范围内的伪随机信号,和ADC高速率数据进行异或,经高速异或门电路后的信号进入处理器,达到“加扰”的目的。电路设计时,充分考虑信号间的串扰、开关电源噪声的污染、以及信号链路的信号完整性等,并进行了前仿真加后仿真的联合设计。对成板电路进行实物介电常数、阻抗、插损等测试,再由這些实测参数指导进一步的仿真过程,设计出符合要求的超高速采样电路。

高速信号仿真主要包括过孔优化仿真、通过频域仿真分析和时域仿真分析。整个系统为点对点通信,单个通道信号速率为10 GS/s。

2.3 FPGA软件设计

FPGA处理软件是实现单比特接收机功能的核心,决定着灵敏度、测频精度等指标,根据本项目技术指标,FPGA处理算法进行针对性的设计。

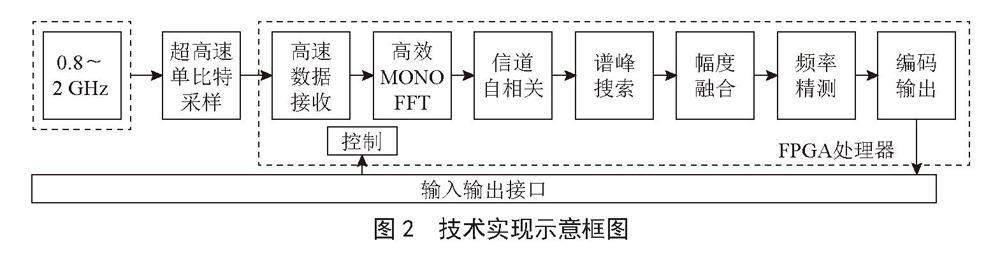

FPGA处理算法的实现示意框图如图2所示。

软件算法按照功能分为以下步骤:

1)高速数据接收。超高速采样电路工作在10 Gbit/s,完成对输入信号的采样量化,量化后的数字信号通过高速串行收发器传输。接收端采用FPGA内嵌的高速串行收发器GTH配对接收,收发器的参考时钟由超高速采样电路的随路时钟分频产生,这样保证了数据能够稳定的被GTH接收且不会产生累计误差。FPGA内部控制逻辑首先对接收完成的数据对齐保证采样数据的同步;其次完成数据的顺序切换,因为采样时钟相位的随机性会影响ADC的DeMax输出顺序的变化;最后对调整好的数据按照算法所需的顺序完成排序并整合。在完成时钟域同步后送入高效超快速傅氏变换模块进行运算。

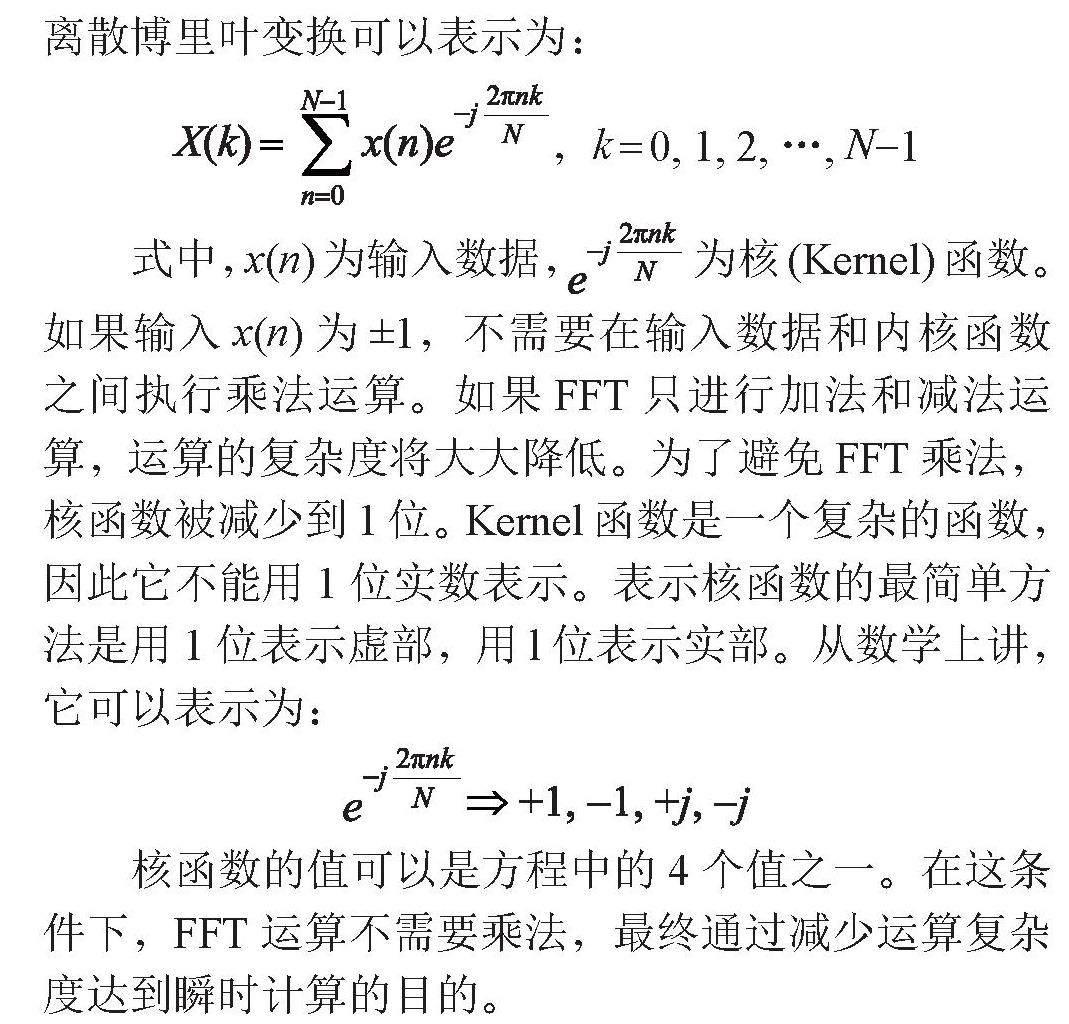

2)超快速傅氏变换。超快速傅氏变换算法的是离散傅氏变换的快速算法,对离散傅里叶变换的算法进行改进获得的,通过消除FFT过程中的乘法运算来减小FFT的复杂性。一个模拟信号,经过ADC采样之后,就变成了数字信号,数字信号就可以做FFT变换了。N个采样点,就可以得到N个点的FFT结果。离散博里叶变换可以表示为:

,k = 0, 1, 2, …, N-1

式中,x(n)为输入数据, 为核(Kernel)函数。如果输入x(n)为±1,不需要在输入数据和内核函数之间执行乘法运算。如果FFT只进行加法和减法运算,运算的复杂度将大大降低。为了避免FFT乘法,核函数被减少到1位。Kernel函数是一个复杂的函数,因此它不能用1位实数表示。表示核函数的最简单方法是用1位表示虚部,用l位表示实部。从数学上讲,它可以表示为:

核函数的值可以是方程中的4个值之一。在这条件下,FFT运算不需要乘法,最终通过减少运算复杂度达到瞬时计算的目的。

3)谱峰搜索。接着在高效MonibitFFT模块的自相关输出结果中进行最大频谱搜索,即首先对自相关输出结果进行取模运算,再在各信道中进行最大值比较。将峰值谱线的复数信息提取相位信息,并发送后续频率精度测量模块进行频率精度估计,峰值谱线的模与确定的门限做比较,得到输入信号的包络信息,用作TOA和PW计算。

采用超高速接收算法并结合滑动FFT算法,可以满足超高速采样模块输出的高速采样信号进行实时流水快速测量的需求。为了数据实时处理,不能对采样数据逐点进行滑动FFT运算,需根据数据的变化来改变滑动的点数和FFT的长度并结合系统的各项指标以及硬件特性等综合考虑。

4)频率精测。每个FFT谱线的频率精度,还不能达到设计要求的2.5 MHz检测精度,这种情况下就需要对频率进行精确测量,重心法进行频率估计与FFT变换过程中的窗函数是直接相关的,假设采用矩形窗函数,那么等效于时域上幅度为1,宽度为T的矩形窗。矩形窗的频域傅里叶变换是一个辛格函数 ,峰值位于f = 0处,第一个峰值出现在±1/T位置。

通过MATLAB仿真形式对测频精度进行仿真分析,得到结果如图3所示。从图中可以看到测频精度是可以达到设计要求的。

图3 频率测量精度(r.m.s)

从单比特数字测频的处理算法来看,通过FFT的方式划分了信道,因此即使在检测信号中存在数个功率接近的信号,经过FFT后划分到不同的信道中,不会对测频精度造成影响。

5)编码输出。根据输出结果的要求,对处理精频率码进行编码并输出。

3 单比特接收机的测频精度

测频误差fc由频率测量误差fstd和板上晶振的抖动误差fq两部分组成,且两者相互独立,故三者之间的关系如下式所示:

频率测量通过时间差分方式实现,其表达式如下:

其中fs表示内部数据率(常数),本方案中采用512点FFT,内部数据率为40 MHz,θ表示时域测量的瞬时相位值,?θ = θn - θn-1,其中θn和θn-1独立同分布。因此频率的标准差为:

当信号的信噪比优于8 dBc时,θstd ≈ 1 / SNR,因此:

其中,SNR = SNRin + G,其中G表示数字处理增益,约为15 dB,因为本项目的信号灵敏度要求不高,SNRin约为+40 dBc。因此SNR约为55 dBc,项目中fs = 40 MHz,计算得到fstd = 0.25 MHz。

本文选用的晶振是一款稳定度为±20×10-6的频率为160 MHz的差分晶振,能保证在工作温度范围内稳定度为160 M×20×10-6 = 3.2 kHz,通过锁相环倍频到5.12 GHz后对测频精度的影响fq = 0.1 MHz。因此根据上面公式可算出最终的测频精度fc为0.27 MHz。

4 单比特接收机的接收灵敏度

接收灵敏度是单比特接收机解调微弱信号并从中获取信息的能力。单比特接收的信号质量是通过计算接收的错误的比特数与接收的总比特数之比来衡量的,将采样量化后的信号进行FFT运算,信号从时域变换到频域进行处理,获得信号的频率和幅度等信息。由于雷达信号在频域具有能量集中的特点,利用FFT运算进行频域检测,可有效提高检测灵敏度。

接收机灵敏度描述的是能夠获得有用信息的最低信号功率,这是接收机的最重要技术指标之一。接收机灵敏度计算式如下:

S = -174 dBm/Hz + NF + 101 gBW + SNR

对于本超宽带数字接收机,接收机的处理能力SNR为+4 dB,暂定系统前级噪声系数NF = 10 dB,BW取2 GHz,将上述参数代入下式:

S = -174 dBm/Hz + NF + 101 gBW + SNR

可估算出本设备接收机的灵敏度为:

S = -174 dBm/Hz + 10 dB + 63 dB+4 dB = -67 dBm

5 单比特接收机的测频时间

单比特接收机的测频时间优于200 ns。具体测频时间计算如表1所示。

表1 测频时间表

序号 过程 时间/ ns

1 射频通道 2

2 单比特采样 30

3 高速数据接收 40

4 MonoFFT计算 64

6 谱峰搜索 32

7 频率精测 25

8 编码输出 5

合计 198

6 实现的技术指标

单比特接收机实现的技术指标如表2所示。

表2 实现的技术指标

序号 指标项 实现的技术指标

1 工作频率范围 0.8~2 GHz

2 射频输入动态范围 -55~-5 dBm

3 灵敏度 ≤-65 dBm

4 测频精度 ≤1 MHz(r.m.s)

6 测频时间 ≤200 ns

7 适应信号脉宽 0.1 μs~CW

8 适应周期范围 2 μs~CW

9 适应信号形式 常规脉冲、脉冲压缩、脉冲多普勒、频率捷变、连续波等;同时存在脉冲及连续波时,出连续波信号标志,出大信号的频率和保宽脉冲

7 结 论

本文设计研制的0.8~2 GHz单比特接收机,经过对该接收机认真详细的设计工作,主要包括0.8~

2 GHz单比特接收机的宽带微波通道前端、超高速采样处理板以及FPGA软件的设计,同时对主要技术指标进行了分析,实现了频率范围为0.8~2 GHz、测频精度小、灵敏度低、测频时间快,功耗小的单比特接收机,并在测频系统中得到应用,实际使用效果较好。

参考文献:

[1] 李秀萍.微波技术基础:第2版 [M].北京:电子工业出版社,2017.

[2] 李兆龙、王贵.射频与微波电路 [M].北京:电子工业出版社.2022.

[3 ]何鹏,韩俊辉.同时到达信号数字信道化检测技术研究 [J].现代电子技术,2023,46(5):20-24.

[4] 马月红,张伟涛,惠蕙,等.基于单比特接收机的高检测率测频方法设计与实现 [J].北京理工大学学报,2021,41(7):774-780.

[5] WANG X Q,XU J P,LU S ,et al. Single-Receiver Multioutput Inductive Power Transfer System With Independent Regulation and Unity Power Factor [J].IEEE Transactions on Power Electronics,2022,37(1):1159-1171.

[6] 冷从阳.基于PFGA的相位检测系统设计 [J].现代信息科技,2021,5(19):60-62+66.

[7] 石荣,阎剑,张聪.基于随机抖动的单比特量化理论分析与仿真研究 [J].现代电子技术,2013,36(3):63-66.

[8] 肖吉阳.一种大带宽单比特数字接收机设计方法 [D].长沙:国防科学技术大学,2012.

[9] 陈鑫,户昐鹤,苏晓龙,等.单比特量化下宽带辐射源信号参数估计性能研究 [J].现代雷达,2022,44(8):25-30.

[10] 董晓,张云华.基于单比特量化的噪声雷达系统与处理方法 [J].现代雷达,2022,44(8):8-13.

作者简介:王玉红(1984—),女,汉族,江苏徐州人,高级工程师,本科,研究方向:电子对抗工作;秦睢睢(1985—),男,汉族,河南新乡人,高级工程师,硕士研究生,研究方向:电子对抗工作;李兵(1981—)男,汉族,江苏南通人,高级工程师,本科,研究方向:雷达干扰与模拟工作。