基于比例积分和二分法控制的全数字锁相环研究

蒋小军,蒋小伟

(湖南铁道职业技术学院,湖南 株洲 412001)

0 引言

锁定时间是全数字锁相环的重要性能指标之一,为了使锁定时间尽可能小,采用自适应带宽技术的锁相环根据输入信号与输出信号的相位或者频率信号来改变滤波器的带宽[1]。采用调频字估计和预置技术的锁相环改变数控振荡器的频率预设字[2-3],使之更接近目标频率,从而减少锁定时间,但他们的频率分辨率不高。以上传统锁相环的锁定时间与输出频率范围、滤波器带宽、目标频率和频率分辨率有关,锁相环输出频率范围越大,滤波器的带宽越小,数控振荡器输出频率离锁定的目标频率越远,数控振荡器的频率分辨率越高,导致锁定时间越长。

为了解决上述问题,本文提出了一种基于比例积分(PI)和二分法控制的全数字锁环结构。该锁相环根据输入信号和输出信号之间的相位和频率误差信号,通过比例积分和二分法对数控振荡器频率控制字进行调整,从而实现目标频率的快速锁定。

1 电路结构与工作原理

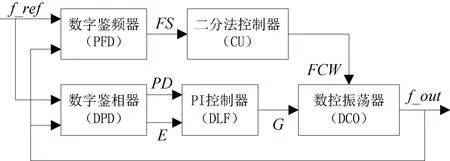

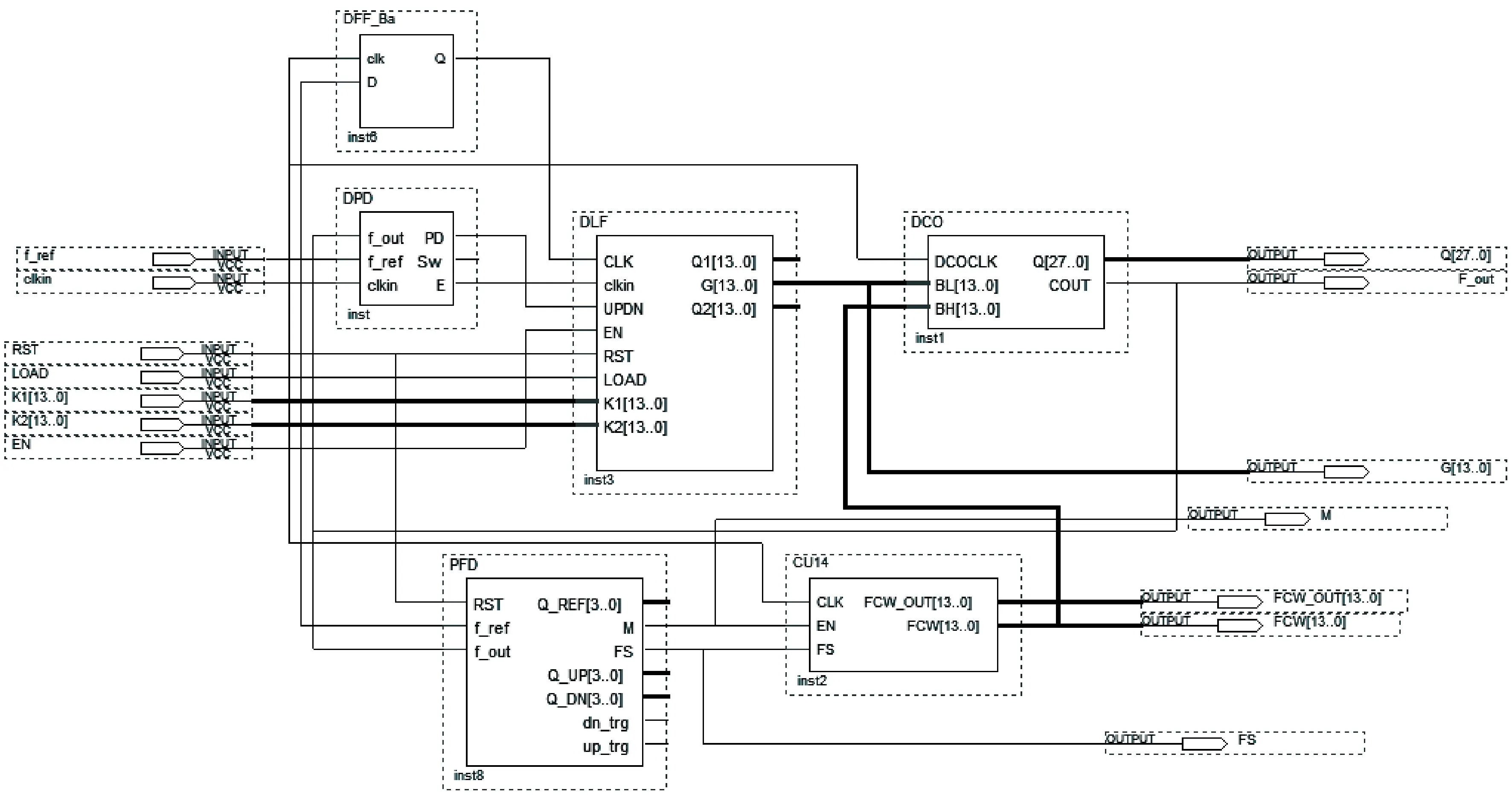

本文提出的全数字锁相环结构如图1所示,由数字鉴频器(PFD)、数字鉴相器(DPD)、二分法控制器(CU)、PI控制器(DLF)和数控振荡器(DCO)组成。数字鉴相器(DPD)由触发器和与非门电路组成,数字鉴频器(PFD)由计数器和比较器组成[3]。DCO的频率控制字由二分法控制器(CU)产生的高位频率控制字(FCW)和PI控制器(DLF)产生的低位频率控制字(G)组成。数字鉴频器根据输入参考信号与输出信号的频率快慢关系,生成快慢信号FS,二分法控制器根据快慢信号FS,对数控振荡器的高位频率控制字FCW进行粗略估算,将频率缩小在一定的频率范围内。数字鉴相器根据输入参考信号与输出信号的频率和相位误差生成相位超前或滞后信号PD和误差大小信号E,PI控制器根据相位信号PD和误差大小E,对DCO的低位频率控制字G进行细微调节,实现频率和相位的快速锁定。

图1 全数字锁相环结构

2 电路设计和仿真分析

2.1 二分法控制器的设计

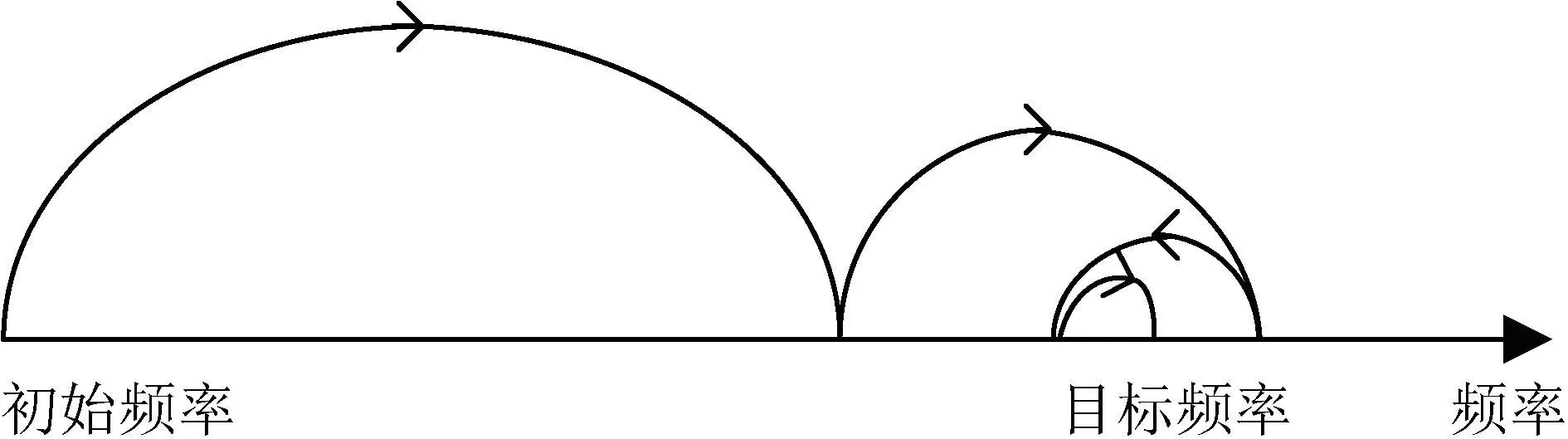

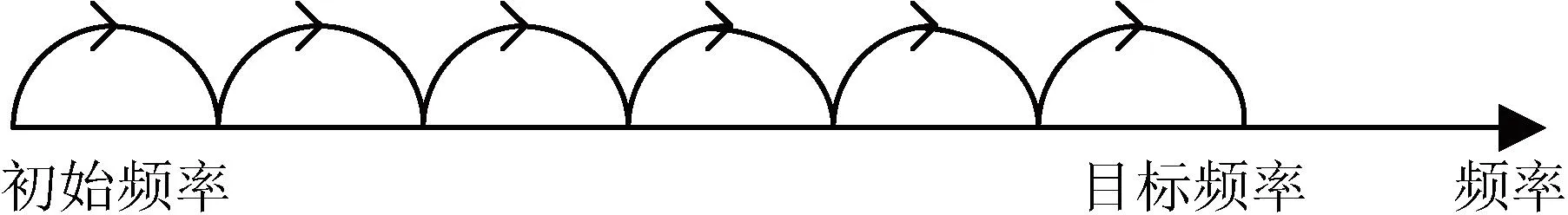

二分法是一种快速搜索算法,频率搜索过程如图2所示。与图3所示的渐进频率搜索方案相比,ADPLL中的二分法搜索能更快地锁定目标频率。二分法控制器(CU)根据PFD输出的“快”或“慢”的信号FS调节DCO的频率控制字FCW来快速锁定DOC目标频率[4-5]。

图2 二分法频率搜索

图3 渐进频率搜索

在CU设计中,FCW计算使用二分方案进行调整,这是一个迭代过程,从给定的值范围内确定估计的值。为了实现二分方案的运行,二分法控制器需要对DCO最大和最小频率进行初始化。二分法计算公式如下。

当f_ref频率大于f_out频率时:

(1)

当f_ref频率小于f_out频率时:

(2)

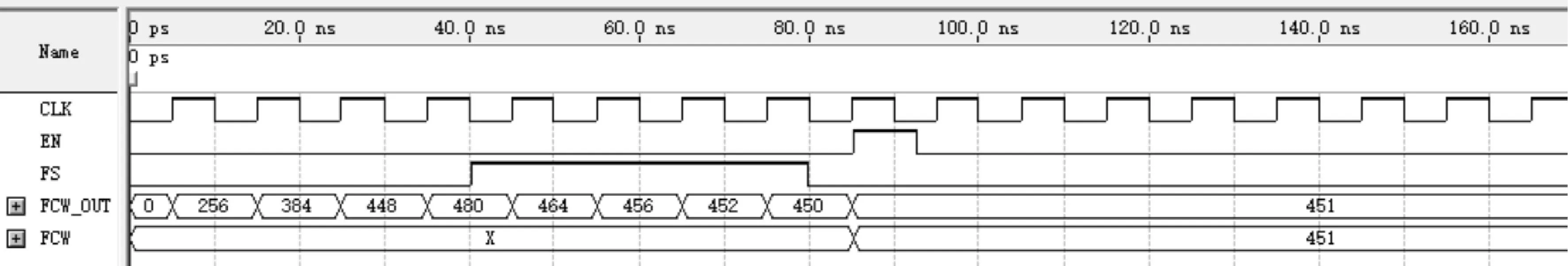

图4 FCW仿真时序

2.2 整体电路设计

根据图1锁相环系统的结构,利用Altera公司的QuartusⅡ设计软件,对全数字锁相环进行了设计和仿真,仿真电路如图5所示。该系统由数字鉴频器(PFD)、数字鉴相器(DPD)、二分法控制器(CU)、PI控制器(DLP)和数控振荡器(DCO)等组成。

图5 锁相环的仿真电路

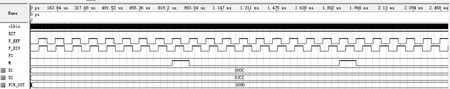

锁相环的仿真波形如图6所示,当输入参考频率f_ref为10 kHz时,二分法控制器根据数字鉴频器输出的“快”或“慢”信号FS,对数控振荡器DCO的频率控制字FCW进行粗略计算,大概经过9个周期,锁相环就实现了DCO目标频率的快速锁定。

图6 仿真波形

3 结语

为了缩短锁相环的锁定时间,快速搜索DCO的目标频率,锁相环采用了一种二分法频率搜索方案来计算DCO频率控制字FCW。仿真结果表明,基于PI和二分法控制的全数字锁相环,实现了相位和频率的快速锁定。