HBM、CDM 静电放电模型及其失效特征研究

刘信,罗晓羽,万永康,江徽,汪小青

(1.中国电子科技集团公司第五十八研究所,无锡 214000; 2.中国电子技术标准化研究院,北京 100007)

引言

随着集成电路工艺的发展,芯片的性能不断增强、集成度越来越高、特征尺寸不断减小,对静电敏感度越来越高,静电放电(ESD)问题日益严重并已成为行业挑战。过去二三十年的研究表明,70 %的芯片产品失效与静电放电有关[1]。据美国静电协会统计,全世界每年由于ESD 导致芯片失效产生的经济损失高达450 亿美元[2]。

芯片静电放电过程复杂多变,为了研究芯片静电放电原理及失效特征,科研人员根据放电源和放电形式的差异,建立了多种静电放电模型,其中最具有代表性的三种模型分别为人体模型(HBM)、机器模型(MM)和带电器件模型(CDM)[3]。机器模型与人体模型具有相同的电路结构,不同之处在于机器模型的放电电容高、电阻低,可以将机器模型看作是最极端条件下的人体模型。因此,本文不对机器模型进行研究。

本文首先对人体模型、带电器件模型原理进行介绍,从原理角度分析HBM 与CDM 的差异,然后选用两款不同芯片进行HBM ESD、CDM ESD 极限测试,获取芯片HBM ESD、CDM ESD 测试失效电压及其失效特征,并对两种静电放电模型失效特征进行对比分析。

1 HBM 与CDM 的区别

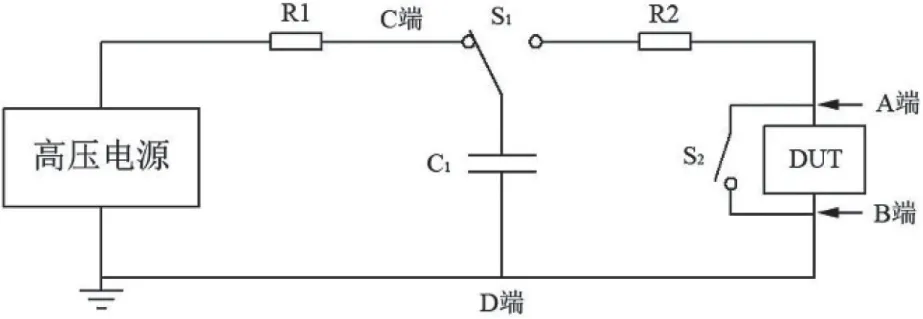

HBM 是指由于某些原因携带了静电电荷的人体接触了芯片,人体上的静电电荷会经芯片引脚传递到芯片内部,再从芯片内部经引脚放电到大地。HBM 静电放电过程时间短,可在几百纳秒内产生数安培的电流烧毁芯片[4]。图1 是参照GJB 548B-2005 方法3015 静电放电敏感度分级试验的电路图(人体模型),图中C1 是人体的等效电容,通常为100 pF,R2 是人体的等效电阻,通常为1 500 Ω[5]。

图1 HBM 测试等效电路

进入二十一世纪以来,集成电路技术飞速发展,芯片制造、封装及测试的自动化程度越来越高,芯片厂家对于防静电要求不断提高,由于人体接触导致的芯片静电放电失效事件逐渐减少。而CDM 静电放电造成的芯片失效比例不断增加,其重要性已引起人们的重视[6]。

CDM 是指芯片由于摩擦或电场感应等原因,在芯片内部积累了大量的静电电荷,由于没有导电通路,电荷均匀的分布在芯片中,没有造成芯片损伤。此时,当带有大量电荷的芯片接触地面或接地良好物体时会形成导电通路,芯片内部电荷会经芯片引脚向外流出,产生放电现象。芯片的面积越大,积累的电荷越多,释放的电流就越大。

相较于人体模型,带电器件模型的放电速度快,在实际测试中很难被模拟,芯片的放置方式、封装形式也会对放电电流产生影响。图2 为带电器件模型场感应装置示意图[7]。

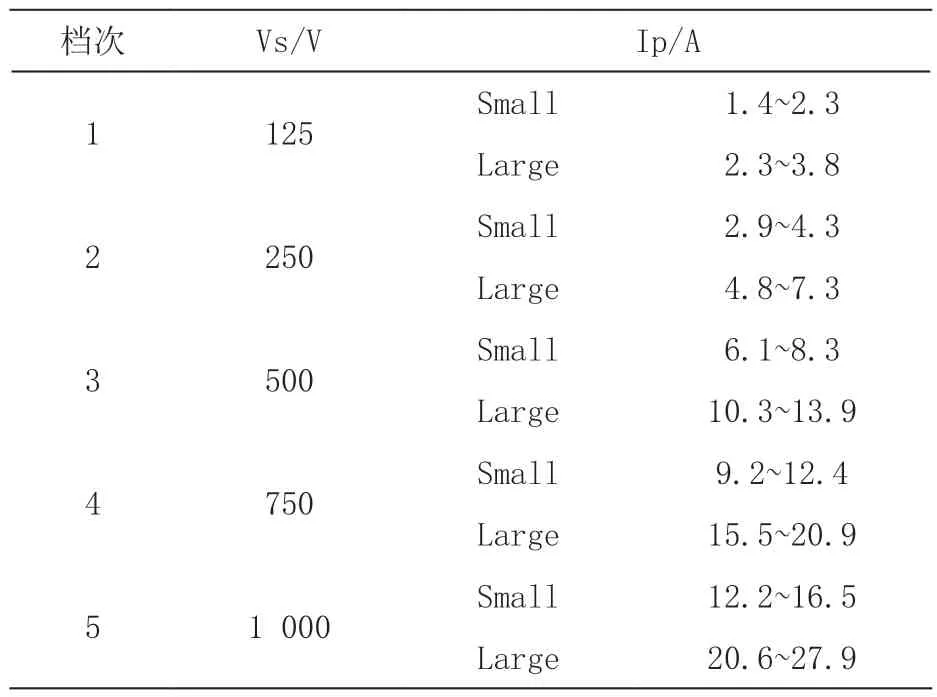

GJB 548B-2005 和JS-002-2018 标准 对HBM ESD、CDM ESD 试验的峰值电流有相关说明[7,8]。从表1、表2中可以看出,相同测试电压下,CDM 峰值电流要比HBM峰值电流高的多。

表1 HBM ESD 充电电压(Vs)和峰值电流(Ip)

表2 带宽(≥6 GHz)示波器下CDM ESD 充电电压(Vs)和峰值电流(Ip)

2 静电放电失效机理

芯片静电损伤失效机理分为电流型损伤机理和电压型损伤机理。电流型损伤机理失效现象包括接触孔合金钉、栅氧化层和PN 结损伤等;电压型损伤机理失效现象包括多晶硅、栅氧化层击穿等。

静电放电会造成芯片局部温度过高,多晶硅(硅的熔点1 415 ℃)上消耗的高功率会造成多晶硅温度上升并熔化形成导电丝状物(铝-硅共晶的熔点577 ℃),导致电阻下降几十倍,流过该区域的电流增大、产热量增加,可能导致晶体管的栅氧化层击穿、PN 结损坏、金属互连线熔化等现象。

当具有极短上升时间的ESD 脉冲打击芯片时,芯片内部的ESD 保护管不能起到防静电的作用,ESD 电压会直接加到芯片某一个MOS 管的栅极上,导致晶体管栅氧化层损伤。此外,相比于热氧化层,铜互连线与多晶电阻之间的介质击穿强度较低,当有静电放电事件发生时,可能导致铜互连线与多晶电阻之间介质击穿短路[9]。

3 HBM、CDM 测试

本文选用两款不同芯片依据GJB 548B-2005、JS-002-2018 标准分别进行HBM ESD、CDM ESD 测试,测试方案为起始电压500 V,步进电压500 V,每个电压正负脉冲各打三次,直至芯片失效为止。

经HBM ESD、CDM ESD 步进电压极限测试,芯片1 HBM ESD 测试失效电压为3 000 V、CDM ESD 测试失效电压为1 500 V,芯片2 HBM ESD 测试失效电压为4 000 V、CDM ESD 测试失效电压为1 000 V。从试验结果可以看出,芯片2 HBM ESD 测试失效电压高于芯片1,CDM ESD 测试失效电压却小于芯片1。芯片抵抗HBM ESD 与CDM ESD 能力没有直接关系,并不是抗HBM ESD 的能力强,耐CDM ESD 的能力就高。

4 HBM、CDM 失效特征

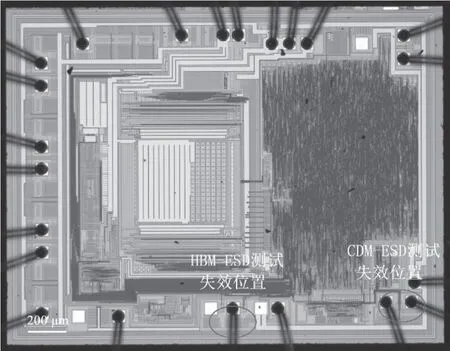

芯片1 具有多层结构,包括多晶层、金属层M1、金属层M2、金属层M3、介质层、钝化层。芯片1 内部目检照片如图3 所示,图中标注了HBM ESD 测试与CDM ESD 测试芯片失效位置。

图3 芯片1 内部目检图片

从图3 中可以看出,HBM ESD、CDM ESD 试验后芯片损伤位置不同。HBM ESD 试验后,芯片损伤位置在ESD 保护管;CDM ESD 试验后,芯片损伤位置在第一个输入缓冲级,不在临近键合焊盘的HBM 和MM 保护电路里。这是由于HBM 与CDM 静电放电的电流路径不同造成的,HBM 的ESD 电流是从芯片引脚流入芯片内部,CDM 的ESD 电流是从芯片内部向外流出。

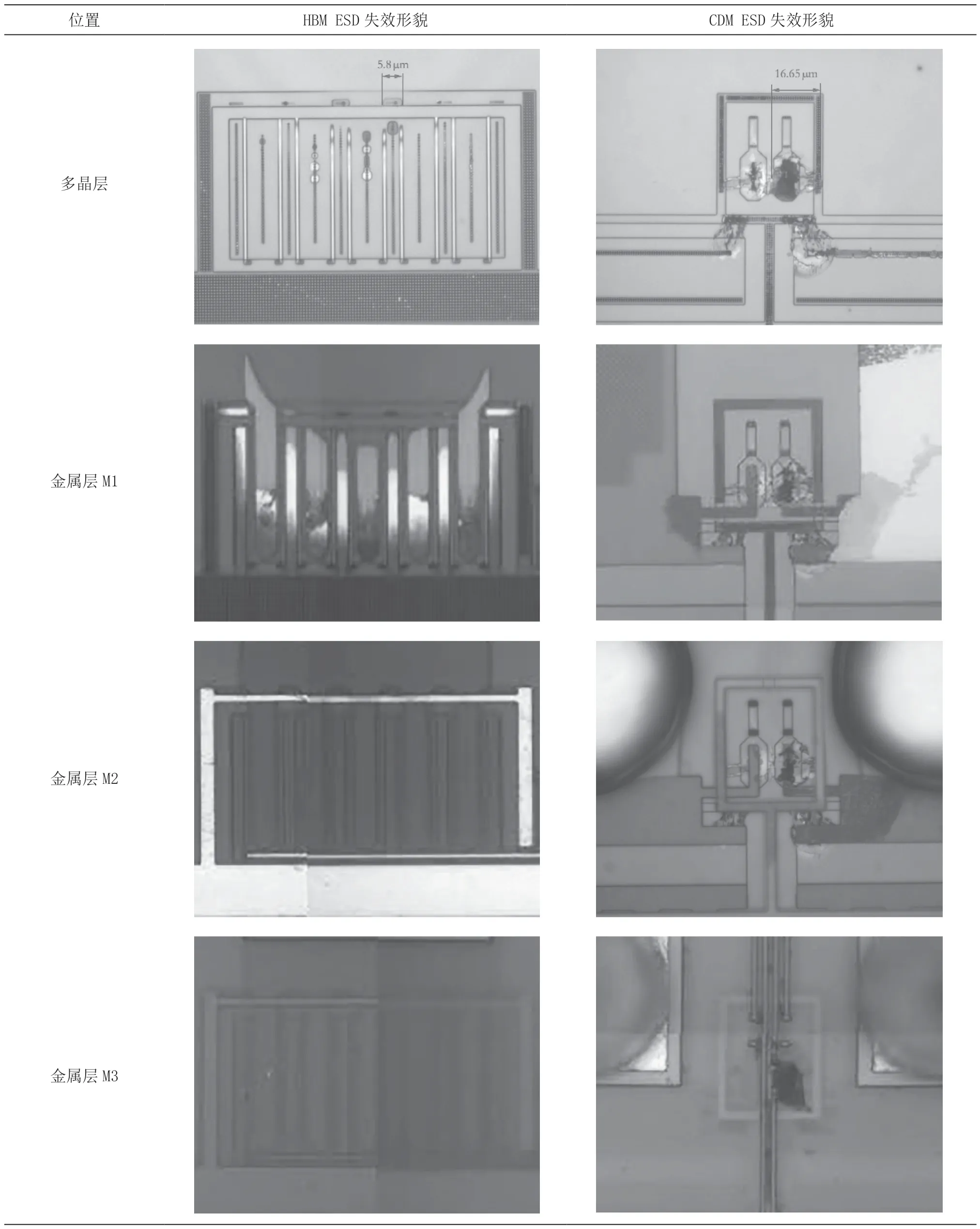

对HBM ESD、CDM ESD 测试失效后芯片1 样品进行去层分析,得到不同芯片层失效形貌,具体情况如表3所示。

表3 芯片1 ESD 失效形貌

从表3 中可以看出,HBM ESD、CDM ESD 试验后芯片损伤形貌存在差异,HBM ESD 试验后在芯片多晶层、金属层M1 可发现损伤形貌,金属层M2、M3 未见异常;CDM ESD 试验后在芯片多晶层、金属层M1、M2、M3 皆可发现损伤形貌(铜互连线熔化),且CDM ESD 试验后芯片损伤区域明显大于HBM ESD 试验后芯片损伤区域。在多晶层,HBM ESD 试验后芯片损伤形貌长度为5.80 μm,CDM ESD 试验后芯片损伤形貌长度为16.65 μm,两者相差187 %。

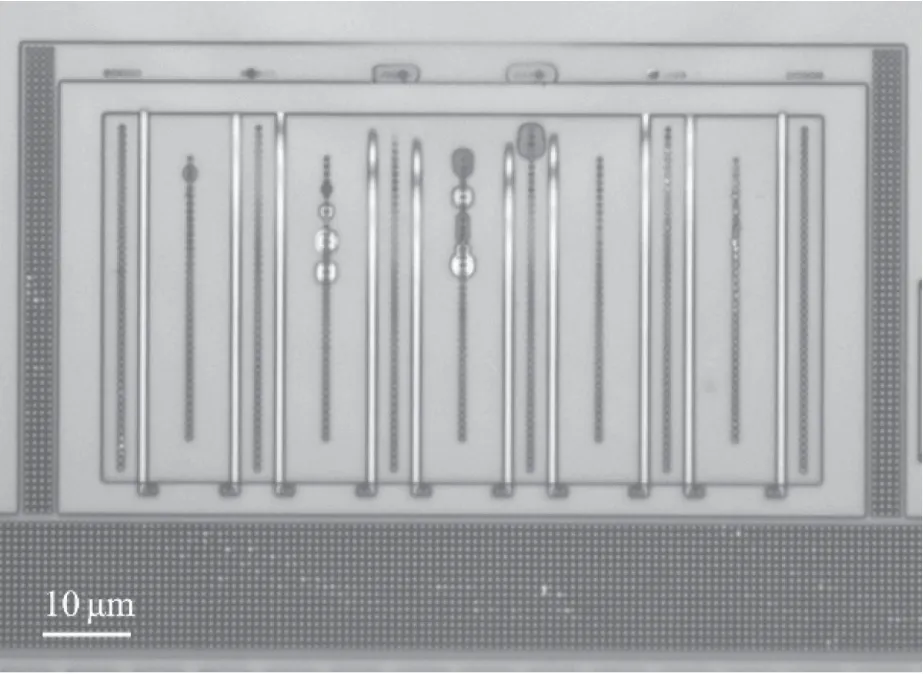

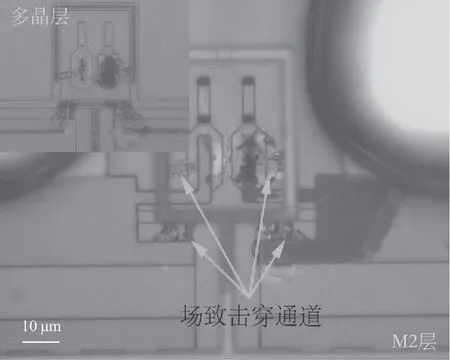

图4 为HBM ESD 试验后芯片失效图片,HBM ESD试验后MOS 晶体管栅氧化层被击穿,从失效机理角度分析属于电流型损伤。图5 为CDM ESD 试验后芯片失效图片,从图中可以发现在两个不同的金属电极之间有明显的场致击穿路径,从失效机理角度分析属于电压型损伤。

图4 芯片1 HBM ESD 后失效图片

图5 芯片1 CDM ESD 后失效图片

5 结论

本文主要结论如下:

1)芯片抵抗HBM ESD 与CDM ESD 能力没有直接关系,并不是抗HBM ESD 的能力强,耐CDM ESD 的能力就高。

2)HBM ESD 与CDM ESD 静电放电测试后芯片损伤位置不同,HBM 静电失效位置主要位于输入/输出管脚的ESD 保护电路里,CDM 静电损伤常发生于第一个输入缓冲级。

3)HBM ESD 与CDM ESD 能量存在较大差异,CDM ESD 对芯片的损伤更严重,CDM ESD 试验后芯片损伤面积明显大于HBM ESD 试验后芯片。