基于FPGA 的LocalLink/AXI4-S 总线协议转换模块设计

张秀清,王金晓,王晓君

(河北科技大学 信息科学与工程学院,河北石家庄,050000)

0 引言

在数据通信过程中,LocalLink 和AXI4-S 是两种不同的协议标准,LocalLink 主要应用在Xilinx 的FPGA 芯片内部,AXI4-S 是一种外部系统总线标准,两者之间无法直接进行通信。与此同时,数字信号常常因为时序问题需要进行打拍处理,由于AXI4-S 协议太复杂,有很多通道和信号,而且valid 信号和ready 信号的传递方向还是相反的,直接打拍会陷入时序混乱的漩涡。本文设计了一种基于register slice 配合逻辑电路的模块,能够实现两协议之间相互转换的功能,运用register slice 实现AXI4-S 信号在master和slave 之间传递时打拍并解决时序问题。LocalLink 和AXI4-S 总线之间数据稳定且高效传输,提高设备之间的兼容性,占用FPGA 资源较少,效率更高,降低系统成本和复杂度的同时还具备了很好的移植性[1]。

1 协议概述

LocalLink[2]协议是Xilinx FPGA 内部使用的一种片内通信协议,用于芯片内可配置逻辑之间的数据传输和通信。该协议是一种高性能的点对点同步传输协议,它能在传输时采用流水线方式。LocalLink 协议具有以下特征:任意字节宽度的用户接口、任意长度的数据帧、同步点对点通信、上下游流量控制、渠道支持、高效的带宽利用率、支持奇偶校验和错误报告[3]。LocalLink 通信方式保证了芯片内各模块间的同步性和互操作性。本协议设计简单、硬件结构清晰且易于实现,能够满足高性能、低时延以及可靠性等多方面需求,成为Xilinx FPGA 内部通信的主要标准方案。

每一个LocalLink 接口由一个源接口和一个目的接口组成,可实现两台设备之间的全双工操作以及数据的单向传输。LocalLink 接口框图如图1 所示。

图1 LocalLink 接口框图

在LocalLink 传输协议中,数据以帧为单位进行传输,一帧数据包括负载数据,帧头和帧尾。在实际工程应用中,LocalLink 接口信号有很多,并且都是成对出现的。本设计中,采用的接口信号见表1。

表1 LocalLink接口信号表

LocalLink 接口的传输机制如下,当源接口检测到目的准备好信号时,产生帧开始信号和源准备好信号,数据传输开始。当源接口产生帧结束信号时,目的接口驱动目的准备好信号无效,传输过程结束。LocalLink 接口信号时序图如图2 所示。

图2 LocalLink 接口信号时序图

AXI4-S[4]是基于流模式传输的高性能片内总线协议,主要用于大量流式数据的传输,支持多数据流使用同一数据通路,并且可以支持数据位宽的转换[5]。使用AXI4-S 总线协议进行数据传输时,不需要提供数据流地址以及其他控制信息,因此AXI4-S 总线协议经常在高带宽、低消耗以及低延迟的单向数据传输场景中使用。本协议设计简单,易于实现,已成为业界广泛采用的标准之一[6]。

在AXI4-S 总线协议中,每个数据流由一组可配置的信号描述。本设计中,采用的AXI4-S 接口信号见表2。

表2 AXI4-S接口信号表

AXI4-S 总线协议是一种双向流控传输机制,收发双方通过VALID/READY 信号控制传输速率。为确保数据能够进行正确传输,在数据发送之前,需要确认收发双方已经完成握手操作。当主模块tvalid 信号和从模块的tready 信号都有效时,表示握手操作完成,开始数据传输过程。AXI4-S接口信号时序如图3 所示。

图3 AXI4-S 传输时序图

2 模块设计

模块采用Xilinx 公司K7 系列的FPGA 芯片作为核心芯片,通过对LocalLink/AXI4-Stream 总线协议各接口信号进行逻辑处理和时序调整,完成了两协议转换功能。根据模块功能需求模块分为LocalLink 转AXI4-S 模块和AXI4-S 转LocalLink 模块两部分。

2.1 LocalLink 转AXI4-S 模块

LocalLink 转AXI4-S 模块负责将LocalLink 协议数据转换成AXI4-S 总线协议格式,并将数据发送到AXI4-S 总线上。在其结构上可以分为以下两个部分:一个逻辑电路和一个register slice,其结构框图,如图4 所示。

图4 LocalLink 转AXI4-S 模块结构框图

由图4 可知,逻辑电路将LocalLink 数据流转换为AXI4-S数据流,register slice 完成对AXI4-S 数据流打拍实现时序处理。逻辑电路与register slice 功能具体详述如下:逻辑电路中,对于输入的LocalLink 信号,在源准备好和目的准备好置起时,收发双方成功握手,数据传输开始。数据线在整个传输过程中均为直连,不对其进行逻辑操作;EOF 信号对应LAST 信号;SRC_RDY 信号对应VALID 信号;REM 信号分全字节有效/部分字节有效情况输出对应的KEEP 信号,READY 信号对应输出给上级的准备好信号。此时信号转换为AXI4-S 数据流形式。Slice 包括四部分:逻辑功能产生器,存储单元,多路复用器以及进位逻辑。使用register slice 的数据切片以及隔离主从之间时钟路径功能,将AXI4-S 总线数据流中的数据切片并存储到寄存器内,高效且稳定输出符合预期频率的AXI4-S 总线数据流。因register slice 中信号均为低电平有效,在逻辑电路中进行相应的取反操作。

部分信号赋值语句如下:

2.2 AXI4-S 转LocalLink 模块

AXI4-S 转LocalLink 模块将从AXI4-S 总线上接收到的数据转换成LocalLink 协议形式的数据发送出去。在其结构上可以分为以下四个部分:两个逻辑电路和两个register slice,其结构框图,如图5 所示。

图5 AXI 转LocalLink 模块结构框图

由图5 可知,AXI4-S 转LocalLink 模块实现方式与LocalLink 转AXI4-S 模块有所区别,其通过两个逻辑电路和两个register slice 实现。逻辑电路与register slice 功能具体详述如下:对于输入的AXI4-S 总线数据流,在tready信号和tvalid 信号同时置起时,收发双方成功握手,数据传输开始。输入的AXI4-S 总线数据流,输入至register slice 进行切片处理并缓存在寄存器中,输出至逻辑电路,模块中主要的时序逻辑转换由此模块完成。其中,tdata、tready、tvalid 均为直连;tuser 信号为s_rem、s_sof 和s_tlast 的一个组合信号,在输入信号m_axi_tkeep 中搜索第一个零值,循环遍历信号的位,检查每位是否为0,当找到第一个零值时,循环停止,输出对应的s_rem,如果没有找到零值,则s_rem 设置为全零。Tkeep、tlast、tvalid 信号是否同时为真决定s_sof 为0 或1。因此电路为时序逻辑电路,存在时序问题,将输出的AXI4-S总线数据流再次输入至register slice 切片缓存实现对时序的处理,输出稳定的AXI4-S 总线数据流;最后进入逻辑电路,进行取反与逻辑与等组合逻辑操作后,输出符合预期频率的LocalLink信号。

部分信号赋值语句如下:

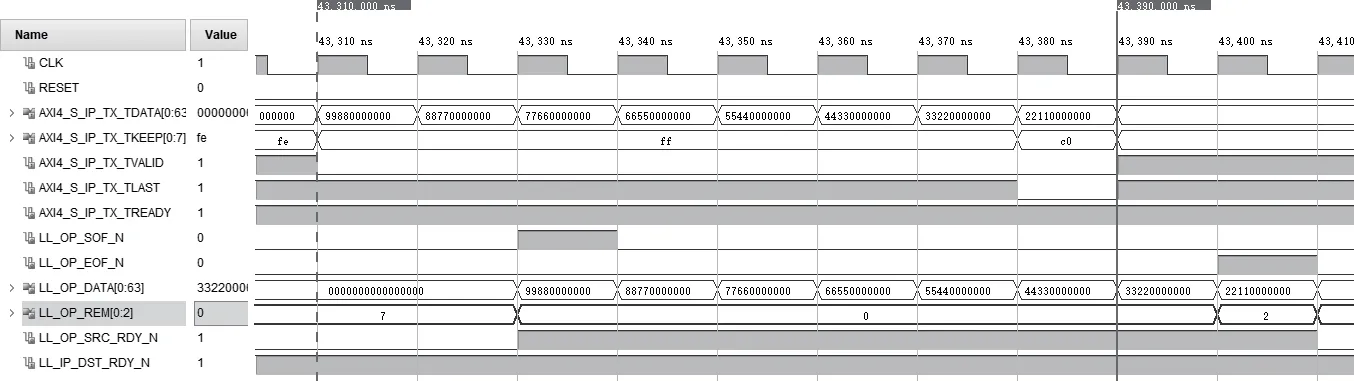

3 仿真分析

使用Xilinx 的集成开发环境Vivado 2017.4 进行逻辑功能实现以及相应的仿真测试。本次模块设计采用层次化设计思想,将复杂的设计简化为模块化设计。由于FPGA 的纵隔实现周期较长,设计使用Testbench 模型提供系统激励来进行功能仿真测试。使用自定义的数据源,在上行输出处与下行输入处做自环连接,根据SOF 信号与EOF 信号同时/不同时置起两种情况,对回路中各个模块进行仿真实验。系统时钟设置为100M,复位时间为3250ns,一帧数据为64Byte。Testbench 给入LocalLink 格式数据流。

当SOF 信号与EOF 信号同时置起时,上行仿真图如图6 所示。其中,CLK 是时钟信号,RESET 是系统复位信号,O_LK_SOF、O_LK_EOF、O_LK_DATA、O_SDL_REM、O_LK_SRC_RDY、I_LK_DST_RDY 为输入的LocalLink 信号。LocalLink 信号经过处理后输出一组AXI4-S 信号。下行仿真图如图7 所示,从上行来的AXI4-S 信号经过处理后输出一组LocalLink 信号。

图6 上行仿真结果

图7 下行仿真结果

当SOF 信号与EOF 信号不同时置起时,上行仿真图如图8 所示。LocalLink 信号经过处理后输出一组AXI4-S 信号。下行仿真图如图9 所示,从上行来的AXI4-S 信号经过处理后输出一组LocalLink 信号。

图8 上行仿真结果

图9 下行仿真结果

由图可以看出,两种情况下上行和下行接口信号的时序完全正确,上行模块输入的数据与经过本模块行输出的数据流完全相同,可充分验证本模块数据传输的正确性。

4 结语

本模块设计在基于FPGA 的环境下,采用VHDL 和Verilog 硬件描述语言进行编程设计。对LocalLink 协议和AXI4-S 总线协议的概念、特性以及接口信号等进行了详细介绍,将register slice 运用到系统中,给出模块设计方案。对模块功能进行仿真验证,实现LocalLink/AXI4-S 总线协议转换,具有很实用的参考和工程价值。