高性能数据记录仪的设计与实现

蒋炯炜,查婕,雷志军

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

在弹药的制导化改造过程中,所有的改造措施都必须通过靶场的实弹测试完成验证[1]。为了最大限度发挥实弹测试的验证效果,离线式弹载采集存储设备在实弹测试的过程中发挥着重要作用[2]。在测试中需要通过数据回读对数据解析后得到相关飞行参数,以便进行后续试验[3]。当今弹载数据记录仪的功能越来越丰富,记录数据的类型越来越多,飞控、舵机、雷达乃至图像信息都在需要记录的数据范围内[4]。这使得记录仪存储速度不仅要快,容量还要大,而且数据回读时间也要尽可能短。如果导弹飞行数据从记录仪中导出太慢,靶场试验时现场人员无法及时地对相关参数进行统计和分析,并根据分析结果作出下一步的试验调整,将会影响整体的试验质量[5]。

随着电子技术的不断发展,数据记录仪在存取数据灵活性、存储速率和可靠性等方面不断提高[6]。本文设计了一款高性能数据记录仪,选用大容量、传输速度快的嵌入式多媒体卡(eMMC)芯片作为存储介质,通过TI 公司的DSP 处理器与Xinlix 公司的FPGA 相互配套协作,最终实现了3 路CAN 和1 路RS485 数据的采集及压缩、32 GB 容量双备份循环存储,并可以用USB 接口快速将eMMC 中的存储数据上传给上位机以进行进一步分析,从而对导弹飞行模拟系统的关键性能参数进行评估。

2 硬件平台设计

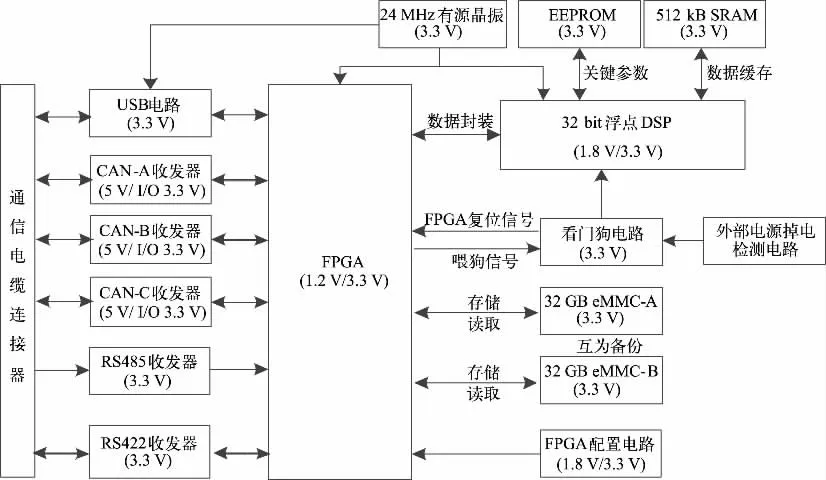

图1 为记录仪的硬件平台设计框图,采用了Spartan6 系列FPGA 搭配C2000 系列DSP,实现数据的接收、存储和回读功能。通信接口主要包括:3 路CAN 接口、1 路RS485 接口,用于接收飞行时传输的关键信息;1 路USB2.0 接口,用于对记录仪的数据回读和FPGA 程序升级;1 路RS422 接口,用于设备调试时信息反馈和DSP 程序升级。存储接口主要包括1 片256×16 bit 的SRAM 和2 片32 GB 的eMMC。在一些对存储容量和速度有较高要求的场合,可以使用eMMC 这种大容量存储芯片[7],其内部自带的错误检查和纠正(ECC)算法会自动计算出对应数据的ECC值[8],可靠性高。硬件平台中FPGA 主要完成CAN 控制器IP 核集成、CAN 数据缓存、RS485 数据缓存及eMMC 的读写驱动。DSP 主要对所有需要存储的数据进行加工和封装,并按照特定格式存于eMMC 芯片中。

图1 记录仪的硬件平台设计框图

2.1 电源网络设计

记录仪外部的电源电压输入范围为16~36 V,可以转换为多级电源供电。外部输入电源经瞬态电压抑制器(TVS)、浪涌抑制器、电磁干扰(EMI)滤波器到电容网络进一步处理后,输入给掉电检测电路,便于系统掉电时通知记录仪完成最后的数据处理和存储工作;同时也通过隔离的DC/DC 电源,降压转换为5 V二级电源给法拉电容充电,系统掉电时记录仪还可以继续工作一段时间。通过LDO 生成三级电源,如1.2 V FPGA 内核电源、1.9 V DSP 内核电源和3.3 V I/O 电源。实际评测28 V 电源输入时,记录仪整体电流约为150 mA,功耗小于5 W。

2.2 接口速率设计

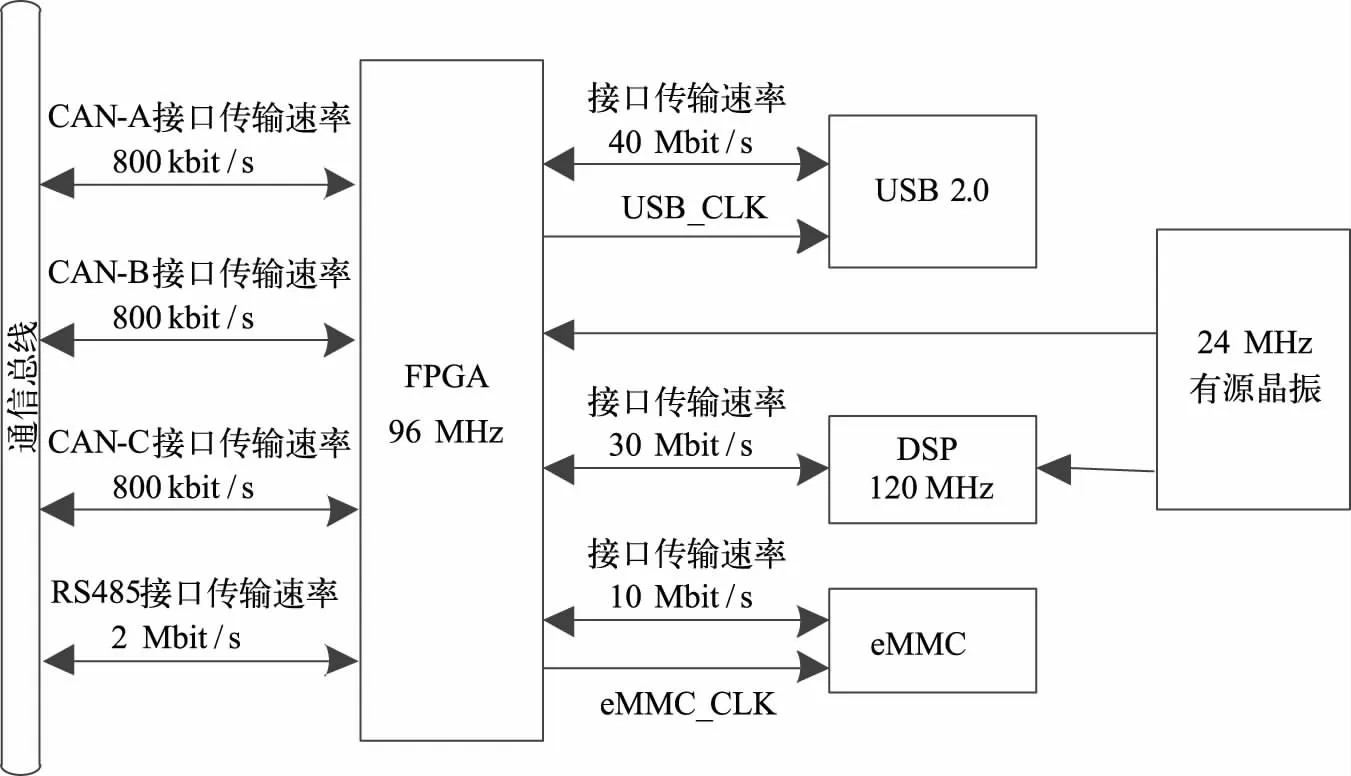

记录仪上各接口的数据传输速率如图2 所示。外部24 MHz 的有源晶振同时向DSP 和FPGA 提供时钟。DSP 和FPGA 分别通过内部锁相环(PLL)将主频倍至120MHz 和96MHz,其中FPGA 还向USB 芯片和eMMC 存储芯片提供工作所需的时钟信号。数据存储时,FPGA 与eMMC 的接口传输速率可达10 Mbit/s。数据回读时,FPGA 与USB 的接口传输速率可达40Mbit/s。

图2 数据传输速率示意图

通信总线上所有的数据都由FPGA 进行接收,其内部给CAN 通信开设的FIFO 能缓存1 kB 的数据,给RS485 通信开设的FIFO 能缓存4 kB 的数据。RS485 数据以2 Mbit/s 的速率发送,而CAN 总线上的数据以800 kbit/s 的速率发送,速率比为2.5∶1,而对应的FIFO 缓存比为4∶1,等效于总线100%负载的条件下,数据填满缓存RS485 的FIFO 和缓存CAN 的FIFO 的时间比为1.6∶1。按照理论计算,填满缓存CAN数据的FIFO 时间为[(1×1 024×8)/800]ms=10.24 ms,填满缓存RS485 数据的FIFO 时间为(10.24×1.6)ms=16.38 ms。实际应用环境中,CAN 帧的格式主要为扩展帧,一共为13 个字节(1 字节帧信息+4 字节报文识别码+8 字节实际数据)。RS485 帧格式为4 字节帧头+508 字节数据。对应当前FPGA 所开设的FIFO 大小,能分别最大缓存78 帧CAN 数据和8 帧RS485 数据。在满负载率条件下,DSP 需要在(10.24/78)ms=0.13 ms内取完CAN 数据、在(16.38/8)ms=2.0 ms 内取完RS485 数据才不会丢数据,因此对FPGA 与DSP 之间的数据交互速率要求很高,两者通过XINTF 接口进行数据交换,设计时将XINTF 接口速率配置成30 Mbit/s可以满足实际要求。

3 软件架构设计

记录仪软件主要分为DSP 软件、FPGA 软件和上位机软件。对数据存储时,DSP 软件先读取eMMC 存储的地址信息,判断需要存储数据的起始地址。FPGA软件按照CAN 总线协议和RS485 协议从外部接口接收对应的数据后,将其存入内部CAN/RS485 FIFO。DSP 软件通过XINTF 协议查询FPGA 内CAN/RS485 FIFO 是否有数据,若有数据则从FPGA 将数据取走,完成封装处理后回传给FPGA 内的eMMC FIFO 完成存储。同时DSP 软件会判断CAN 数据每帧的ID 号,确认该帧是否为指令帧。若为指令帧,DSP 软件将根据指令要求进行对应的操作(读取数据存储器状态或者进行eMMC 擦除),指令执行完成响应后,再将响应帧数据通过FPGA 发送至通信总线上。数据回读时,上位机先通过USB 接口向记录仪发送回读指令,FPGA 软件解析指令后,根据JEDEC 协议将数据从eMMC 芯片中读出,再通过USB 协议将数据上传至PC 端的上位机。

3.1 DSP 软件设计

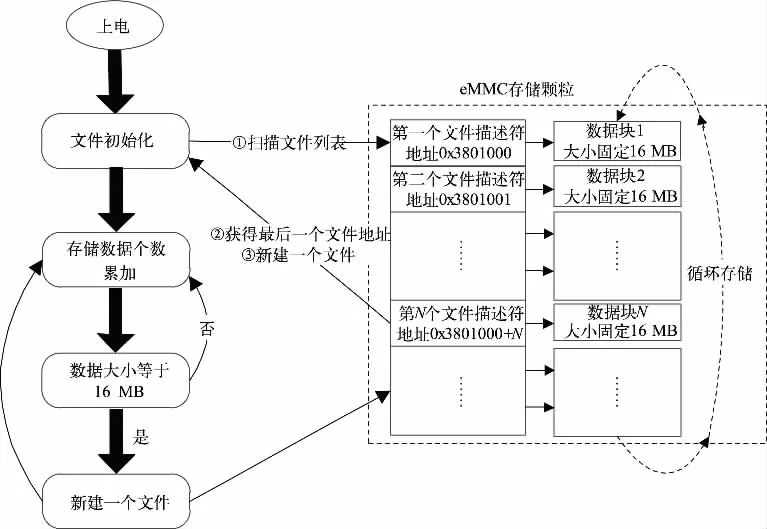

DSP 软件完成数据存储的过程如图3 所示,文件列表和数据块分离,分别存储在eMMC 内两块连续的地址空间。每个文件的存储地址固定,且每个文件对应的数据块大小也均固定为16 MB,顺序存储。记录仪上电后,DSP 先从eMMC 的固定地址0x3801000 开始扫描文件个数,找出当前最后一个文件描述符所在地址后,文件列表地址加1 新建一个文件。数据存储累计满16 MB 后会再新建一个文件,且文件列表地址加1。以此类推,直至数据存满整个eMMC 芯片后自动循环覆盖第一个文件,重新开始存储。

图3 DSP 软件存储数据过程

3.2 FPGA 软件设计

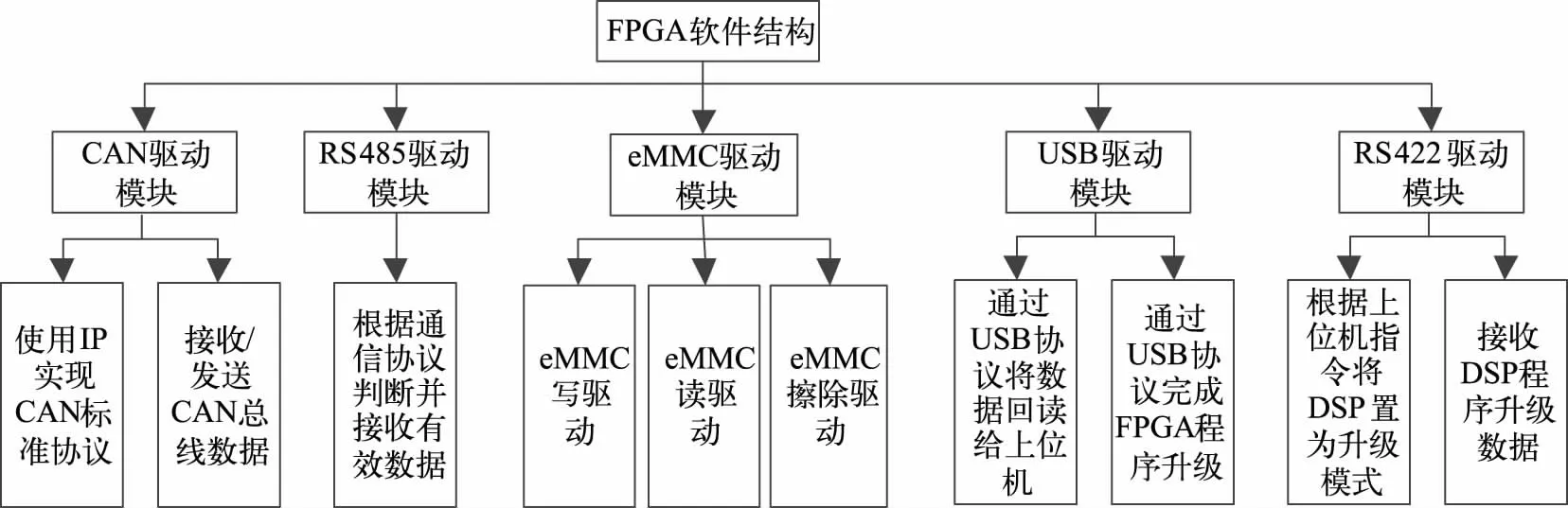

FPGA 软件实现的主要功能及模块组成包括:CAN 驱动模块,使用成熟的IP 实现CAN 总线通信的标准协议后,完成通信数据的接收和发送;RS485 驱动模块,具备自适应波特率的功能,并根据约定的通信协议判断数据的有效性,只接收不发送;eMMC 驱动模块,根据标准的JEDEC 协议,实现对eMMC 存储芯片的访问,主要包括读、写和擦除功能;USB 驱动模块,通过标准的USB2.0 协议与上位机进行通信,根据指令要求将指定的数据块从eMMC 存储芯片中回读出来,同时也可以根据特定指令完成FPGA 程序的在线升级;RS422 驱动模块,作为上位机和DSP 之间的桥梁,可以实现记录仪状态信息的上传打印,也可以根据上位机指令要求,将DSP 从工作模式切换成串口升级的模式,不需要使用仿真器与JTAG 相连[9],就能将上位机发送的升级代码烧写到DSP 中,完成程序的更新。

FPGA 软件驱动模块如图4 所示。

图4 FPGA 软件驱动模块

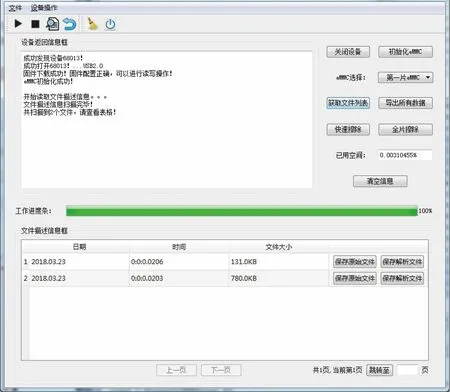

3.3 上位机软件设计

上位机开发环境为Visual Studio 2010,数据记录仪的上位机有如下功能:固件驱动自动加载功能、显示剩余存储容量和剩余存储容量百分比、显示文件名称、显示文件大小、记录开始时间、记录结束时间、支持保存原始数据功能、支持保存解析数据功能、支持快速擦除和全片擦除功能,数据记录仪上位机界面如图5 所示。

图5 数据记录仪上位机界面

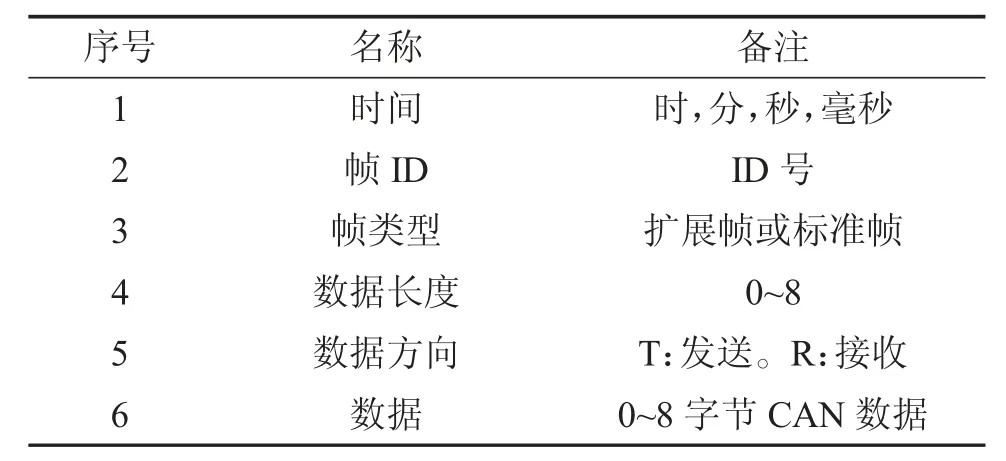

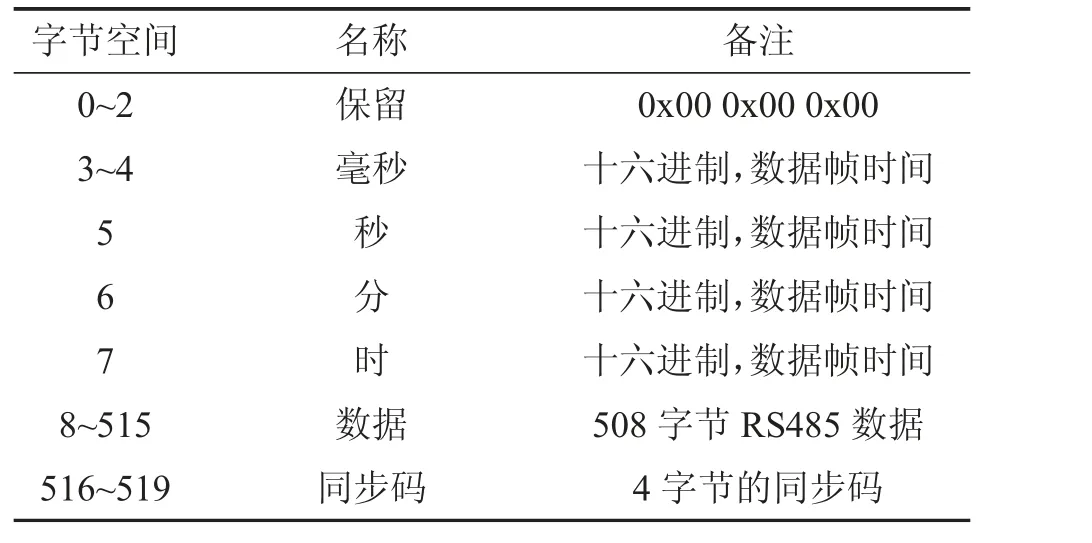

点击“保存原始文件”可以保存数据记录仪存储的原始数据为.dat 的十六进制文件,CAN 数据和RS485 数据混合,可读性较差。点击“保存解析文件”,是在原始文件的基础上,保存上位机根据通信数据帧格式进行格式整理后生成.txt 的文件,方便用户查看分析。表1 为CAN 数据帧的格式,表2 为RS485 数据帧的格式。

表1 CAN 数据帧格式

表2 RS485 数据帧格式

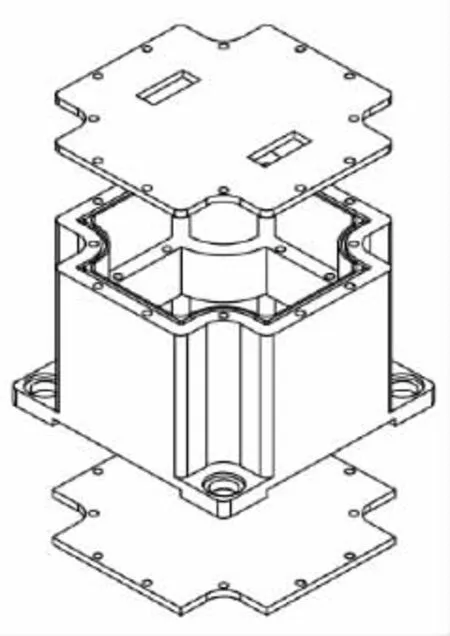

4 机械结构设计

记录仪的机械结构如图6 所示,数据记录仪的外壳长为100 mm,宽为100 mm,高度为70 mm,壳体材质选用了铝合金,整体质量约为0.9 kg。内部腔体从上往下依次放置通信板、控制板和电源板。固定板子的台阶采用探出式结构,在保证连接可靠性的前提下,可以有效减少外壳重量,也为电路板尺寸留出了更多的裕量。

图6 记录仪的机械结构

壳体设计时在电磁兼容方面也做了充分考虑。由于电源板上的电源模块开关频率较高,会通过辐射和传导这两条路径对控制板和通信板造成一定的电磁干扰,为提升EMC 性能,采取下列措施:在壳体盖板上将外部供电线缆和信号线缆分开,分别使用单独的连接器,减小电源和信号线之间的相互耦合;在PCB布局时,将电源模块、EMI 电源滤波器和浪涌抑制器均放置在电源板上,安装在壳体底部并设置了隔层进行屏蔽和散热,隔绝电源模块EMI 辐射耦合路径;为了避免电源线缆从壳体顶部接插件贯穿通信板和控制板才能至底部的电源板,专门在壳体内壁上设计了一个封闭式的通道,使电源线缆经过顶部接插件后直接连接至壳体底部的电源板,减少了电源模块EMI 传导耦合路径。电源线传导发射(CE102)检测(10 kHz~10 MHz 电源线传导发射测试)结果表明,数据记录仪的EMC 性能良好,满足指标要求。

5 结论

本文提出了一种高性能弹载数据记录仪的设计方法,采用了擅长数据处理的DSP 作为主控器,灵活性高的FPGA 配合完成通信数据收发和存储,大容量、高可靠的eMMC 颗粒作为存储介质,进一步提高了数据记录仪的整体性能。实现了通信总线在速率4.4 Mbit/s 满载条件下不丢帧接收,完成32 GB 大容量的双备份循环存储。数据导出采取USB 方式,导出速率可达5 MB/s。产品还通过了CE102 电磁兼容试验,整体性能优于同类产品。