基于FPGA 的高速串行收发器TLK2711全双工通信协议设计

杜建鹏

(甘肃电器科学研究院,甘肃兰州 730900)

随着计算机技术和通信技术的发展,系统级的互联已达到Gbps 的传输速率。并行传输技术可以提高芯片与芯片之间、背板与背板之间的数据吞吐量,但总线数呈的增多及传输速率的加快会使PCB 布线的难度提高,并且增加了信号的延时和偏移[1-2]。而串行传输技术充分利用传输媒体的信道容量,可减少所需的连接器引脚数目、降低芯片外围引脚数、设备及电缆布线更为简单、系统抗干扰能力更强[3],因此串行传输技术重新返回到高速传输领域并迅速取代了传统的并行传输技术[4]。8b/10b编码SerDes 是目前许多高速串行总线采用的编码机制和结构,如PCI Express、光纤通道、TLK2711等。其中TLK2711 作为高速串行总线的物理层,被广泛用于空间遥感以及卫星图像的数据传输系统中[5-7]。系统之间的数据传输必须制定相应的协议。虽然符合规范的标准协议(如XILINX 公司为自己FPGA 内嵌的Rocket IO 制定的AURORA 协议)传输速度和精度非常高,但是这些标准协议具有大量通信冗余数据和格式定义弊端,会导致通信延时和系统资源浪费。因此,为了提高系统的可靠性和节约系统资源,本文基于FPGA+TLK2711 平台设计了一种轻量级的高速串行全双工通信协议,该协议为点对点链路层串行协议,经测试可实现1.6Gbps~2.7Gbps 的可靠串行数据传输。

1 TLK2711 芯片简介

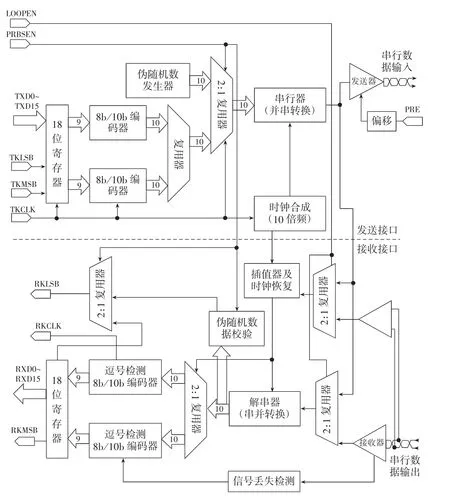

TLK2711 是千兆高速收发器,可用于高速点对点的双向数据传输系统。TLK2711 在发送端将并行信号转换为高速串行信号,在接收端高速串行信号被转换为并行信号,也被称为SerDes(SERializer/DESerializer)收发器,其工作原理如图1 所示。在发送端,TLK2711 将输入的16 位数据(TXD0~TXD15)分为两个字节,在TKLSB 和TKMSB 信号的配合下送入两个8b/10b 编码器进行编码,产生的10 位数据经多路复用器进入串行器,最后通过具有预加重功能的发送器以差分信号的方式输出。在接收端,TLK2711 接收到串行差分信号,首先通过恢复时钟对数据进行同步,其次通过解串器进行串并转换,利用两个独立的逗点检测(Comma Detect)和8b/10b 解码器完成数据解码和字对齐,最后输出16 位并行数据(RXD0~RXD15)以及RKLSB 和RKMSB 信号。图中LOOPEN为环回使能信号,使能后可以进行环回测试;PRBSEN 为伪随机测试使能信号,可利用芯片中的伪随机数发生器产生伪随机信号,进行测试;PRE 为预加重使能信号。

图1 TLK2711 原理框图

2 高速串行数据传输接口设计

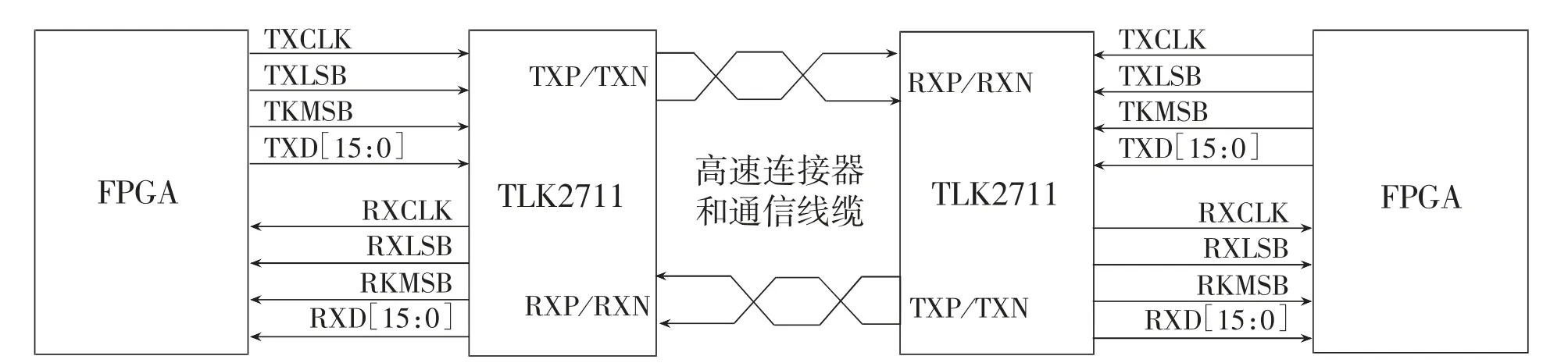

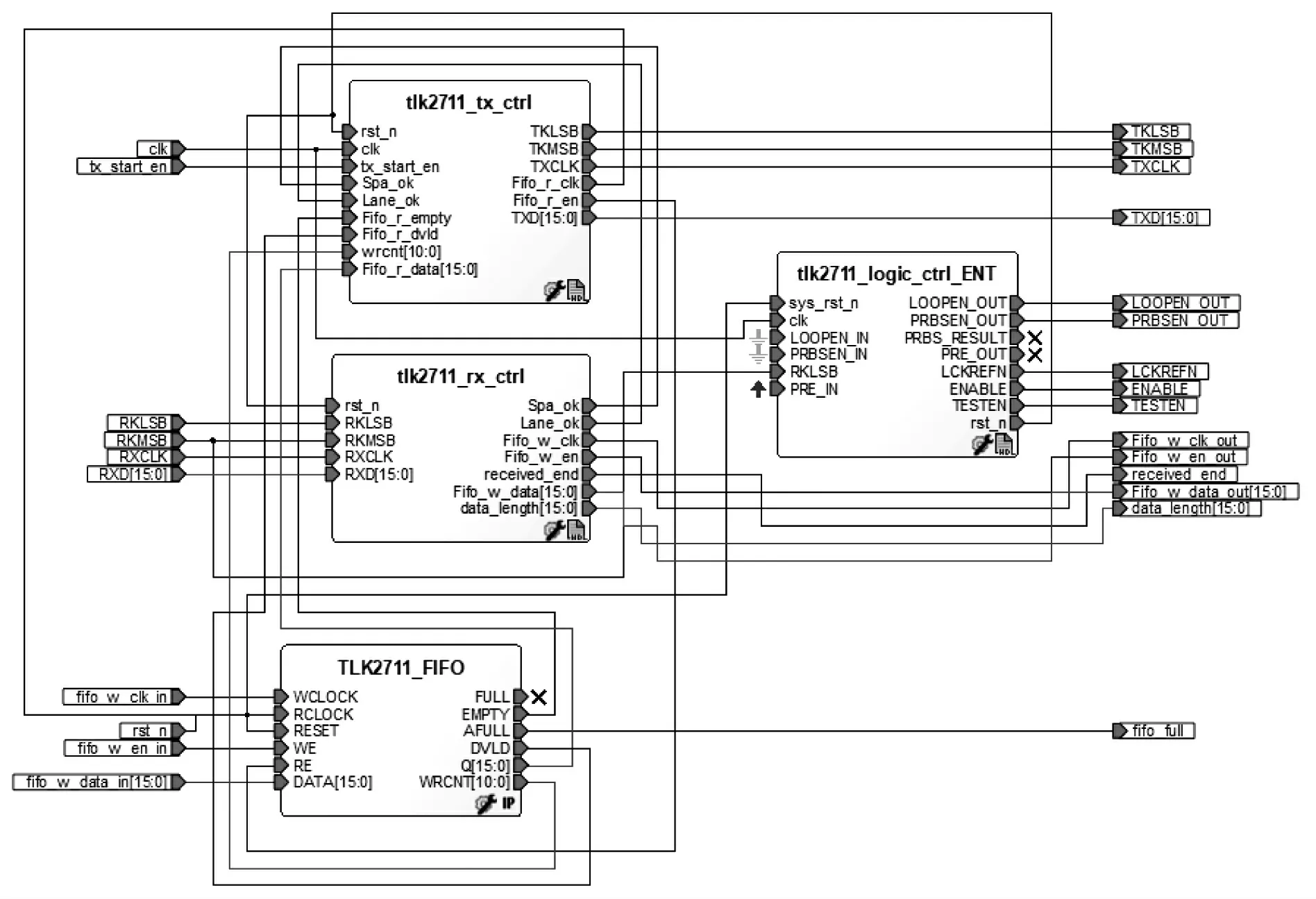

高速串行数据传输接口如图2 所示,TLK2711与高速连接器构成通信协议的物理层,实现收发数据的编解码与串并转换。FPGA 则实现数据链路层功能,完成通道的初始化、发送数据的帧封装、接收数据的解封装,同时为上层用户提供简单的通信接口。

图2 高速串行数据传输接口

3 全双工通信协议设计

3.1 高速串行通信协议模型

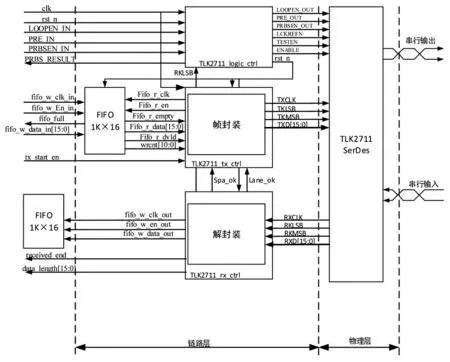

本文设计的是在FPGA 中实现的全双工点对点链路层串行通信协议,不存在寻址交换和复杂的上层应用,主要功能为链路初始化和同步、数据帧传输和链路管理。图3 为高速串行通信协议的模型。模型包括TLK2711_logic_ctrl 模块、TLK2711_tx_ctrl模块、TLK2711_rx_ctrl 模块和FIFO 数据缓存模块。TLK2711_logic_ctrl 模块主要为上层用户提供环回测试、伪随机测试及预加重功能接口,为了简化应用,可将这些信号设置为芯片正常工作时的状态。数据发送功能主要由TLK2711_tx_ctrl 模块和发送端FIFO 实现,上层应用将发送数据写入FIFO,当写完一帧数据后,使能tx_start_en 信号,TLK2711_tx_ctrl模块将FIFO 中的数据读出组帧后发送出去,数据帧长由wrcnt[10:0]信号给定。数据接收功能主要由TLK2711_rx_ctrl 模块实现,当接收到有效数据,TLK2711_rx_ctrl 模块对数据进行解帧,将解帧后的数据写入接收端FIFO,供上层应用读取,每当接收完一个完整的数据帧,TLK2711_rx_ctrl 模块给出数据帧接收完毕信号(received_end 信号)通知上层应用,并给出接收数据帧长。

图3 高速串行通信协议模型

3.2 协议原语及状态切换

3.2.1 协议原语

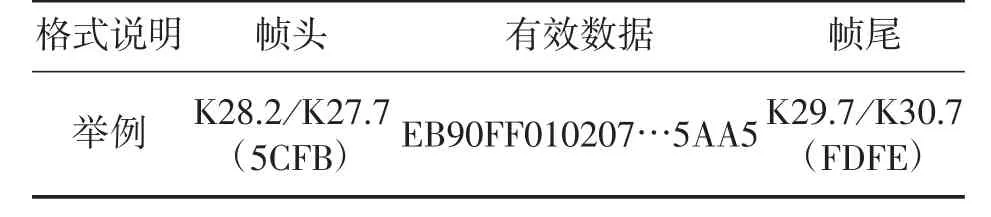

为了保证数据的正确传输,需要传输一些控制信息,这些定义的控制信息称为协议原语。本协议采用8b/10b 中的K 字符和D 字符组合实现数据发送与接收的控制功能。SerDes 通过扫描搜寻cmoma 字符序列实现数据对齐功能。根据技术手册,TLK2711仅识别包含字符特征序列b0011111 或b1100000的控制字符作为识别数据边界的comma 码。在8b/10b中仅有K28.1、K28.5 和K28.7 包含这些字符特征序列,因此定义D5.6/K28.5 为同步字符,D12.1/K28.5 为同 步应 答 字 符,D10.2/K28.5 为 空 闲 字 符,K28.2/K27.7 为帧头标识,K29.7/K30.7 为帧尾标识。

3.2.2 状态切换

系统上电后需要对SerDes 进行初始化和同步来建立一个有效链路,这样SerDes 才能进行正确的数据收发。链路同步由TLK2711_tx_ctrl 模块和TLK2711_rx_ctrl 模块共同完成,最终链路应答标志Spa_ok 和链路同步标志Lane_ok 均为高电平,表示链路同步, 可以进行数据的收发。TLK2711_tx_ctrl 模块和TLK2711_rx_ctrl 模块功能均由状态机实现,具体的状态切换如下:

(1)链路初始化状态

系统上电、复位或数据在传输过程中发生链路中断都会使链路重新初始化。首先发送端会不断发送同步字符D5.6/K28.5,当接收端连续收到32 个同步字符时,会置链路应答标志位Spa_OK为高。

(2)链路同步状态

发送端再次发送80 个连续的同步应答字符D12.1/K28.5 与176 个 连 续 的 同 步 字 符D5.6/K28.5,以保证接收端能够有效的收到32 个同步字符D5.6/K28.5 或16 个同步应答字符D12.1/K28.5。当 接收端在应答状态下收到了连续的16个同步应答字符D12.1/K28.5,则链路同步标志Lane_OK 置高,链路进入同步状态。

(3)收发数据状态

在同步状态下,发送数据首先发送帧头K28.2/K27.7,接下来发送数据,发送数据结束后发送帧尾K29.7/K30.7,之后进入空闲(IDEL)状态。

(4)空闲状态

在空闲状态下,发送端不断发送空闲字符D10.2/K28.5,以保持链路的建立。 当需要发送数据时,转入收发数据状态。

(5)链路检测状态

如果链路在一定时间内没有收到帧头、帧尾、空闲字符、同步字符和同步应答字符,说明收发链路必有一条没有建立,重新进入链路初始化状态。如果链路收到无效字符k0.0 和K31.7(即0x0000或0xFFFF),且RKLSB 与RKMSB 均为高,连续三次,链路即重新进入初始化状态。

3.3 全双工串行通信协议实现

协议的FPGA 逻辑实现采用VHDL 硬件描述语言,由tlk2711_logic_ctrl_ENT 模块、tlk2711_tx_ctrl模块、tlk2711_rx_ctrl 模块和内置发送端TLK2711_FIFO组成,如图4 所示。

图4 全双工串行通信协议

tlk2711_logic_ctrl_ENT 模块主要对TLK2711的控制信号进行了统一管理,包括LCKREFN 信号、TESTEN 信号、LOOPEN 信号、PRBSEN 信号和PRE 信号。该模块接收系统复位信号(rst_n),并产生整个逻辑的复位信号(rst_n),同时将ENABLE置为低电平,延时100ms,使TLK2711 芯片复位。

tlk2711_tx_ctrl 模块主要实现数据的发送和对TLK2711 芯片发送端口的控制。当接收到tx_start_en信号的上升沿,只要发送FIFO 不为空,就读取FIFO 中的数据组帧后进行发送,发送数据长度由tx_start_en 信号的上升沿时,wrcnt[10:0]的值决定。发送数据必须保证链路在初始化后同步的状态下进行,数据帧格式如表1 所示。可以看到帧头和帧尾只占用整个数据帧中的4 个字节,因此该协议属于轻量级的串行数据传输协议。

表1 数据帧格式

tlk2711_rx_ctrl 模块主要实现数据的接收和解帧,将解帧后的数据写入外置接收FIFO。接收数据前需进行链路的初始化和同步。同时,接收端实现链路的检测功能,当判断链路失效后,重新进入复位模式,进行链路的初始化和同步。Spa_ok和Lane_ok 为链路应答标志和链路同步标志,传输至tlk2711_tx_ctrl 模块,作为链路初始化和同步的标志信号。

4 测试与验证

4.1 仿真测试

利用ModelSim 工具对高速串行通信协议进行仿真测试,上电后发送端通过先后发送同步字符和同步应答字符,接收端连续收到相应字符后,最终置链路应答标志位Spa_OK 和链路同步标志Lane_OK 为高电平,链路进入同步状态。

在链路同步状态下,当接收到tx_start_en 信号,发送模块将FIFO 中的数据读出,并增加帧头0x5CFB 和帧尾0xFCFE 后进行发送。

当接收到帧头0x5CFB,将后续接收数据写入FIFO,直到接收到帧尾0xFCFE,发出接收完毕信号received_end 信号。接收数据期间计数接收到的数据个数,接收数据完毕将数据长度通过data_length输出。

4.2 实物测试

利用Microsemi 公司的SmartFusion2 SOC 平台构建多通道数据获取系统,采集到的数据通过由TLK2711 构建的串行数据通道输出。系统有两路TLK2711 构建的串行数据通道和一路千兆以太网接口,测试时将两路串行数据通道的收发接口通过同轴线缆互联,即采集数据由一路串行数据通道发送,再由另一路串行数据通道接收,最后数据通过千兆以太网上传至上位机。通过测试系统能够实现高速可靠数据全双工传输,设置系统时钟为80MHz~135MHz 的范围,系统数据传输速率能够达到1.6Gbps~2.7Gbps。在FPGA 中进行了误码计数设计,通过接收端进行监控收到的数据是否为所发送的数据。测试时发送时钟为135MHz,串行数据率为2.7Gbps,发送数据量为1000Gb,将数据分为10000 个数据帧,发送完毕没有出现误码。所以误码率BER=出错位数/总传输位数<1/1012=10-12。

5 结论

本文以SerDes 器件TLK2711 作为串行数据传输的物理层,在FPGA 中设计串行数据通信协议的链路层,实现了一种轻量级的高速高可靠串行数据通信协议。进行了功能仿真和实物测试,经测试该通信协议在TLK2711 硬件的基础上能够实现最高2.7Gbps 的数据传输速率,误码率小于10-12。本设计将为高速数据系统的设计和验证提供重要参考。