“EDA技术”课程案例化教学改革探索

朱 栋 冯成涛

(常州大学 微电子与控制工程学院, 常州 213159)

电子设计自动化(EDA)技术及其课程设计通常为电子类专业本科学生的必修专业课程,该课程旨在让学生掌握基本的硬件描述语言(HDL)的编程和FPGA应用技术。相比于C语言类的高级语言编程,对于学生来说HDL编程入门较为困难,要求学生有逻辑门电路的编程思维和波形时序的概念。

FPGA在通信领域应用广泛,引入通信类的应用案例,有利于激发学生的学习兴趣,使学生快速掌握FPGA的开发方式,并使学生加深对“数字信号处理”和“通信原理”等其他课程中重要知识点的理解。包秀荣[1]提出将EDA技术应用在“数字电路”课程设计中,引导学生利用EDA工具设计数字电路系统。倪德克等[2]将ModelSim仿真工具应用于数字电路设计中。覃永新等[3]将QDPSK调制系统的设计作为实例引入“EDA技术”的教学中,使学生在掌握EDA技术的同时加深对通信系统工作原理的理解。朱栋等[4]将以FPGA为核心处理器的数字式超声波发生器作为案例,改革电子技术课程设计的案例化教学方式。吴迪等[5]将问题驱动教学法引入“EDA技术”实验,以综合设计作为核心问题反向设计基础实验。丁家峰[6]基于DE2-115口袋实验室构建了全新的培养模式,验证了新培养模式的有效性。本文中设计的基于无线光通信的网络数据透传实验涵盖了网络通信、光通信、数字通信等多种通信技术,是一个多课程综合化的应用案例。

1 实验系统设计

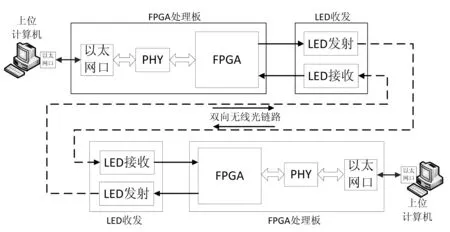

基于无线光通信链路的网络数据实时透传实验系统主要由上位计算机、FPGA处理板、LED收发模块、光链路等单元组成,实验系统框图如图1所示。其中,FPGA是实现网络数据实时透传的核心处理器,实验的主要内容是在FPGA上实现相关功能。FPGA可选用Altera公司的Cyclone IV系列的EP4CE6E22C8低成本器件。FPGA接收来自PHY芯片MII接口的4-bit并行网络数据,该数据为上位计算机通过以太网口发送的包含底层协议包头的16进制数据,FPGA首先将4-bit并行数据转成1-bit串行数据。其次,串行数据作为调制码元加以适当的数字调制驱动LED发射模块,实现光信号的发射。光信号经过无线光链路传播至LED接收模块,LED接收端将光信号转变成电信号并进行放大、滤波、电平比较等处理,整形成TTL电平数字信号并送至对端FPGA。对端FPGA再对数字信号进行调解、串转并等处理后还原成MII接口的4-bit并行网络数据并发送至PHY芯片,最终送至对端上位计算机,从而实现网络数据包的透传。对端上位计算机以同样方式发送网络数据至本端上位计算机,以实现全双工的网络数据透传实验。

图1 实验系统组成框图

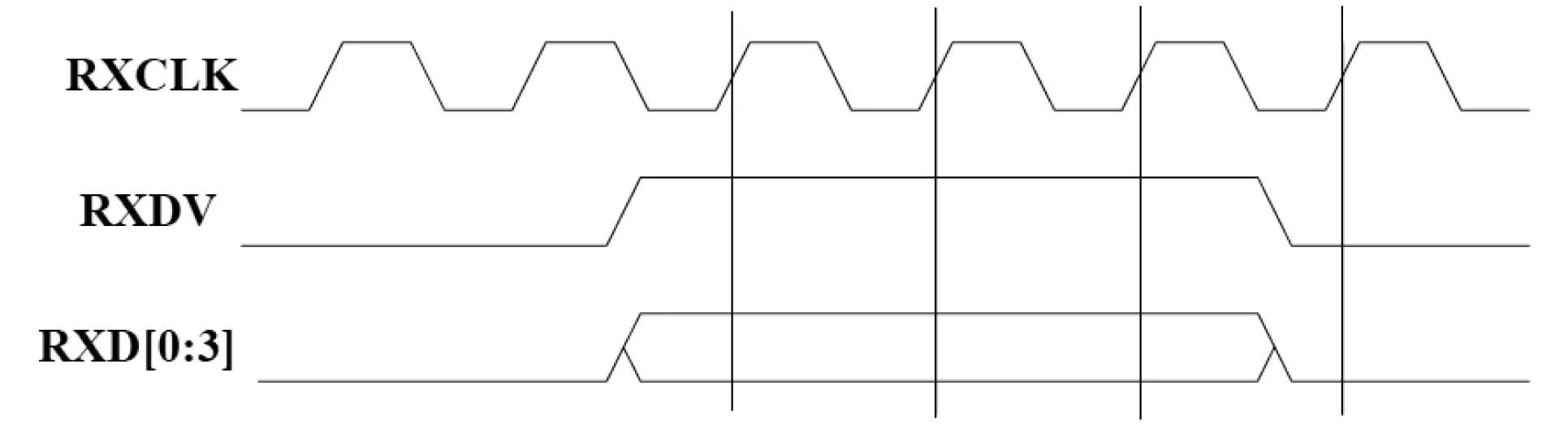

上位计算机通过以太网口与FPGA处理板进行网络数据交互,上位机使用网络调试助手等工具软件实现UDP数据包的收发。普通的以太网口有10 M、100 M、1000 M三种连接速度,千兆PHY芯片可实现10 M/100 M/1000 M自适应连接。PHY芯片是模数混合芯片,当网络连接为10 M/100 M时,PHY芯片的模拟端通过两对差分线TPTX+/ 和TPRX+/ 与网口连接,PHY芯片数字端(即MII接口)与FPGA的普通IO连接。MII接口包括一组用于接收数据的端口(RXCLK、RXD[3:0]、RXDV)和一组用于发送数据的端口(TXCLK、TXD[3:0]、TXEN),以及一组用于配置PHY芯片内部寄存器的双线同步串行总线(MDC和MDIO)。RXCLK和TXCLK分别是数据RXD和TXD的同步时钟,RXDV是接收数据有效的标志信号,TXEN是发送数据有效信号,两者都必须在发送/接收数据期间的第一个时钟前沿之前置为高电平,如图2所示。

(a)PHY芯片数据接收时序图

(b)PHY芯片数据发送时序图图2 PHY芯片数据收发时序图

本实验使用10 M/100 M/1000 M自适应连接且具有RGMII标准接口的PHY芯片,如REALTEK公司的RTL8211F。当网络连接为10 M时,网络数据无需进行缓存,而直接将当前的网络数据进行调制和发射,发射数据的数据率也为10 M,与网络连接速率保持一致,从而实现基于数字逻辑电路的实时数据透传。当网络连接为100 M/1000 M时,数据速率较高,此时要实现数据透传必须使用响应速度更高的激光收发模块以替换LED收发模块。而考虑到激光对人眼的危害,保证实验的安全性,此实验的光链路使用LED收发模块,网络连接设定为10 M速率。

针对光通信链路,调制解调方式有开关键控(OOK)、脉冲位置调制(PPM)、数字脉冲间隔调制(DPIM)等开/关类方式可选,其中DPIM方式的数据帧时长与原始数据帧时长不同,需先对一整包网络数据进行完整缓存后再调制发送,无法实现严格意义上的实时数据透传。DPIM的实现难度也更大,推荐学生主要使用OOK和PPM两种调制方式。LED发射和接收采用红外850 nm或940 nm波段的二极管作为传感器,实验时应尽量减小周围环境可见光干扰。

2 FPGA程序设计

FPGA是实现网络数据实时透传的核心处理器,FPGA收发网络数据并控制光链路发射/接收光信号的处理过程如图3所示。FPGA接收来自PHY芯片RGMII接口的4位并行数据时,先对并行数据进行并转串处理,串行码可实现对光模块发射的控制。以10 M网络连接为例,10 M的串行网络数据利用LED光链路的通断实现信号的传输。

图3 FPGA处理PHY数据的逻辑框图

对RXD数据进行并转串时需要10 MHz时钟,而10 MHz必须与2.5 MHz的并行数据时钟相参,因此,RXD数据进入FPGA后首先要进行数据时钟转换,将来自PHY的数据时钟RXCLK转换成FPGA内部的2.5 MHz。时钟转换的方法是使用FPGA片上双端口RAM,RAM写入时钟使用RXCLK,而读出时钟使用FPGA内部的2.5 MHz时钟。

时钟转换、并转串、数字调制所需的不同频率时钟,均统一由时钟模块FPGA片上PLL产生,以此保持各时钟之间严格相参。数字信号处理中经常会遇到多时钟域的问题,不同频率的时钟由同一时钟源输出才不会引起多时钟域信号处理过程中的竞争与冒险。片上PLL的输入参考时钟则一般由FPGA处理板上的50 MHz晶振提供,而不能采用2.5 MHz的TXCLK,因为用于PLL内部的鉴相时钟至少为10 MHz频率的时钟。

数字调制部分需考虑用于同步的帧头波形、帧结束(空闲)波形、数据段调制方式等三个阶段。由于网络数据具有空闲期间,而LED发射单元通常需在空闲期间也需发射脉冲以维持其稳定状态。针对LED收发模块,可考虑的调制方式为OOK、PPM等开关键控类方式。OOK调制方式相对实现简单,直接将0/1串行数据作为码元即可,但OOK调制的帧头波形可能会与数据波形完全相同,从而引起帧头的误检。针对网络数据而言,此问题可忽略,因为PHY层的UDP数据包均以连续6个0x50作为起始标志。但在信号信噪比较低时,解调时仍然有可能将OOK的数据段判断为帧头波形。而PPM调制则不会出现这样的问题,但实现PPM调制有一定难度。PPM调制是在一个码元周期内,前低后高代表码元为0,前高后低代表码元为1。因此,本实验在数字调制部分的难度分为高低两档:OOK为低难度,PPM为高难度。若采用PPM调制方式,帧头设计为一长脉冲(如350 ns)用于解调时数据位同步,帧结束或空闲期间波形为一短脉冲(如脉宽50 ns),即可实现帧头波形、数据段波形、帧结束波形无任何冲突。假定空闲期间短脉冲的重复周期为400 ns,发射波形三个阶段信号脉冲占空比对比如下:①帧头波形占空比为87.5%;②PPM数据段占空比恒定为50%;③帧结束波形占空比为12.5%。这样设计波形,可使三种波形两两之间特征差别最大,帧头误检率最低。

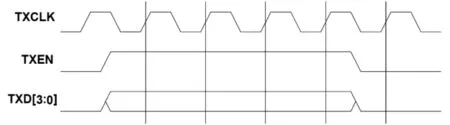

在Quartus II 13开发环境中创建工程并完成编译,Cyclone IV器件的片上资源使用情况如下:①逻辑单元(LEs)使用1429个;②寄存器(registers)使用1092个;③引脚(pins)使用18个;④锁相环(PLL)使用1个;⑤为调试方便,在SignalTap调试工具中添加了多个关键信号,使得片上存储器使用量为221,440 b。在采样时钟80 MHz情况下,几个关键信号的SignalTap采集波形如图4所示。其中,发射波形(ppm_out)采用PPM调制。

图4 SignalTap工具中关键信号采集波形

3 实验要求与达成度评价

由于本实验涉及信号的发射与接收,以及光链路的调试等工作,实验工作量较大,需学生组队协作完成。实验室为每个学生团队提供2台计算机、2块Altera的Cyclone IV FPGA实验板(含下载器)、2套LED收发模块(含放大器)、以及电源等辅助设备。计算机安装Quartus开发工具、ModelSim仿真工具、网络调试助手等软件。作为实验的必选项,每个团队应完成信号并串与串并转换、信号的调制与发射、光信号的接收与解调、以及各模块的ModelSim或Waveform Editor仿真、SignalTap在线调试等基础工作。SignalTap在线调试时需对网络数据包格式进行解析,获取UDP数据包中的帧头标志、目标IP地址和MAC地址、源IP地址和MAC地址等。发挥部分为实现串行数据的PPM调制与解调,作为加分项。实验演示时使用网络调试助手循环发送UDP数据包,查看接收端是否完整接收到数据包并且检查发/收数据包个数是否一致。每个团队由3~4名学生组成,每队在规定时间内完成并撰写实验报告,指导教师根据实验完成项、完成质量、实验报告质量给学生团队打分,发挥部分占总成绩的15%~20%。

利用本实验建立达成度评价标准,分为系统构建能力、数字逻辑电路设计能力、软件开发能力、网络分析能力、文档报告制作能力等五大项目,每项各占总达成度的20%。每一大项又有很多分项,如系统构建能力大项包括系统完整性、系统可行性、调制原理、通信链路等4个子项,每个子项各占5%;数字逻辑电路设计能力大项包括HDL编程、IP调用、时序约束、层次化设计等4个子项,每个子项各占5%;软件开发能力大项包括Quartus应用、SignalTap应用、ModelSim应用、其他工具等4个子项,每个子项各占5%;网络分析能力大项包括网络模型的理解、UDP数据包帧结构、MAC地址解析、CRC校验位解析等4个子项,每个子项各占5%;文档报告制作大项包括文档的完整性、文档的规范性、汇报、现场质疑应变等4个子项,每个子项各占5%。最终,根据各个子项的得分,累计得出总达成度。另外,制作调查问卷,从学生那里得到对于本课程新案例实施过程的反馈意见,做到持续改进,使整个课程不断优化。

4 结语

为提高电子类本科学生的FPGA应用能力,设计了一套基于无线光通信的网络数据实时透传实验系统。学生可以利用该实验平台对网络数据进行调制与解调,以实现在光链路上的实时数据收发。该实验可以作为EDA技术课程的实验或者EDA课程设计的课题,可供3~4名学生协作完成,主要任务是通过编写HDL代码或编辑原理图实现基于FPGA的网络数据透传,并完成实验报告。通过该实验的实践,可加深学生对于数字通信、网络通信等课程中相关知识点的理解,同时极大地提高学生的FPGA应用能力。