面向疏浚工程的电阻层析测量系统优化设计

于 涛,罗 刚,辛长浩,岳士弘

(1.中交天津航道局有限公司,天津 300457; 2.天津大学电气自动化与信息工程学院,天津 300072)

0 引言

疏浚工程[1]主要集中在海域作业。船体时常会产生大范围的静电,并且船上有大量用于保证疏浚作业正常进行的高功率电子器件。这会导致疏浚船体上存在大量的、各种频率的电磁噪声。目前,电阻层析测量系统已经应用于疏浚工程中[2-3]。电阻层析测量系统包括3个主要部分,分别为传感器、数据采集系统和上位机。数据采集系统是电阻层析系统的核心部分,不仅通过传感器完成测量对象信号采集,还要把信号通过通信接口传到上位机进行参数检测和控制。若要保证数据采集系统对应的测量系统在疏浚船体上正常运行,则需要对当前系统进行深度优化,以提高信噪比[4-6]。在实际工况中,疏浚管道内的泥浆流速较快。然而,当前测量系统的采集信号频率较低,测量周期内的管道截面会产生较大变化,造成单组测量值与疏浚管道截面分布的一致性无法保证。为了提高系统的实时性以及信号采集的精度和稳定性,需要提升系统的信号频率。

本文主要围绕电阻层析的数据采集系统以及上位机系统进行相关优化,以提高测量的激励信号频率、采集速率和测量系统在疏浚管道上作业的精确性以及稳定性。

1 电阻层析数据采集系统

当前普遍使用的电阻层析数据采集系统的主要参数如下:采集速度为60 fps;信噪比为52 dB;系统信号频率为80 kHz。该系统具有集成度高、易于扩展、传输速度快等特点[7-8]。

数据采集系统是整个电阻层析测量系统的核心,主要由主控板和选通板组成。数据采集系统的主要功能为激励信号的产生、测量信号的捕捉、模拟到数字/数字到模拟转换、选通电路的切换、测量信号的解调及可编程放大、与上位机的通信等。

主控板的核心功能如下:核心处理单元现场可编程门阵列(field programmable gate array,FPGA)接收上位机相关命令并进行相关处理;FPGA产生的数字信号转换为模拟信号,并经过一系列的放大滤波传输至激励电极;对测量电极端的电流进行差分滤波,并将其转换为数字信号传输至核心处理单元FPGA;将接收到的测量信号进行解调放大并传输至上位机。选通板共8个。每个选通板均可以对4个电极进行选通,并分别对应了双排各16个电极。选通板主要负责对各电极进行“激励”“测量”“接地”3个状态的选通。当16个电极中的1个电极选通为“激励”状态、1个电极为“测量”状态时,其余14个电极皆为“接地”状态。数据采集系统结构如图 1所示。

图1 数据采集系统结构示意图

2 数据采集系统的优化

2.1 影响数据采集系统性能的主要因素

影响信噪比的主要因素如下[9-10]。 疏浚管道内泥浆成分复杂,并且受其他电磁元件的干扰,被测场域携带大量的电磁信号。这会导致测量回路中携带大量的高低频噪声。因此,需要在测量回路中进行频谱分析,并观察噪声的频域分布,从而增加相应的滤波器以消除相关噪声。

影响采集速率的主要因素如下[11]。数据采集系统的信号采集速率主要由系统的单个周期时间决定,即获取1组480个测量值的时间。影响系统单个周期时间的主要因素有电极状态选通的速率、FPGA释放的信号频率和通信模块的传输速率。

当前系统获取双排电极测量值的主要方式为串行选通[12],即进行第一排电极选通测量后,进行第二排电极的选通测量。这种串行方式严重降低了8个选通板电极状态选通的速率。对此,可以通过将选通方式改为并行方式,降低系统的单个工作周期时间。并行的电极选通方式需要占据FPGA双倍的输入/输出(input/output,I/O)引脚。然而,当前FPGA的剩余I/O资源不足以支撑这样的改变,所以需要更换FPGA芯片,重新进行外围电路的设计以及I/O资源的分配。

整个系统中的激励信号频率与测量信号频率相同,都来源于FPGA芯片中的直接数字式合成器(direct digital synthesizer,DDS)知识产权(intellectval property,IP)核。然而,采集系统中的信号频率不仅仅由FPGA决定。电路设计中的数模(diagtal to analog,D/A)转换模块、模数(analog to digital,A/D)转换模块、滤波器的截止频率,以及开关芯片的截止频率,都是决定信号频率的关键因素。从目前各电子元器件的最高工作频率来看,影响系统信号频率的主要因素为A/D转换芯片、开关芯片以及通信模块。对此,可以通过选择具有更高工作频率的相关芯片来提高系统高频率运行的可行性。

在整个测量周期当中,上下位机通信占据了大部分时间,所以提升通信模块的传输速率对提高系统的采集速率至关重要。

综合上述对信号干扰以及工作频率的分析,后续研究将围绕FPGA测量回路、A/D转换、选通电路这3个方面进行相关优化。

2.2 测量回路优化

测量回路主要用于接收从传感器电极上流出的电流信号,并将其传输至FPGA。测量信号携带了场域电导率分布的相关信息。然而,由于疏浚管道场域内信号冗杂,测量信号中会携带各种频率的噪声,故需要在测量回路中增添一系列的信号处理电路,从而得到高精度的测量信号。

通过示波器观察AD8129差分转单端后获得的测量信号可知,其中含有远高于80 kHz的高次谐波。经观察,此高次谐波信号大约处于4 MHz的频段。故本文选择二阶Salley-Kelly低通滤波器,并设置其截止频率为3 MHz。此时,测量信号中的大部分噪声信号已被滤除,有利于提高信噪比。

2.3 A/D转换优化

相敏解调是在FPGA得到测量值过程中的关键步骤。该步骤要求经FPGA采样得到的A/D数字信号必须与DDS IP核输出的数字信号在分辨率与信号频率上达到一致,即A/D转换模块与D/A转换模块在分辨率与采样频率上应保持一致。所以数据采集系统中的信号频率不只由DDS IP核输出端直接决定, A/D转换过程也是关键限制条件。以下对A/D转换过程涉及的分辨率、采样频率等关键参数进行分析。

①分辨率。分辨率代表数字信号量的最低有效位发生变化时所带来的模拟量变化。分辨率越高,则数字量的变化越精细。分辨率表示数字信号量的位宽,故A/D转换芯片位宽越大,输出的数字信号精度越高。

②采样频率。A/D转换输出的单周期信号量个数由A/D转换芯片的采样频率以及模拟信号的频率决定。

(1)

式中:f为模拟信号频率,Hz;fs为采样频率,Hz;N为单周期信号量个数。

不同的单周期信号量个数直接决定了A/D转换的最终效果。单周期信号量个数越多,则输出的数字信号与模拟信号的相似性越高。

根据当前对系统信号频率的需求,若要获得更高的信号频率,并且保证当前单周期信号量的个数,必须提高A/D转换模块以及D/A转换模块的采样频率。当前系统D/A转换模块与A/D转换模块的采样频率均为10 MHz,由FPGA直接提供。其中:D/A转换芯片AD9764最高采样频率为125 MHz;A/D转换芯片AD9240最高采样频率为10 MHz。当前的采样频率即AD9240的最高采样频率,所以AD9240芯片直接限制了数据采集系统的信号频率。

综合上述分析,必须通过更换A/D转换芯片才能提高数据采集系统的信号频率。目前常见的A/D转换芯片的性能参数如表1所示。

表1 常见的A/D转换芯片的性能参数

综合考虑采样频率、成本、精度等条件,本文采用14位高速A/D转换器AD9244。为了使FPGA获得完整的数据,本文需要对基于FPGA的采样时刻和AD9244的D/A转换过程进行分析。

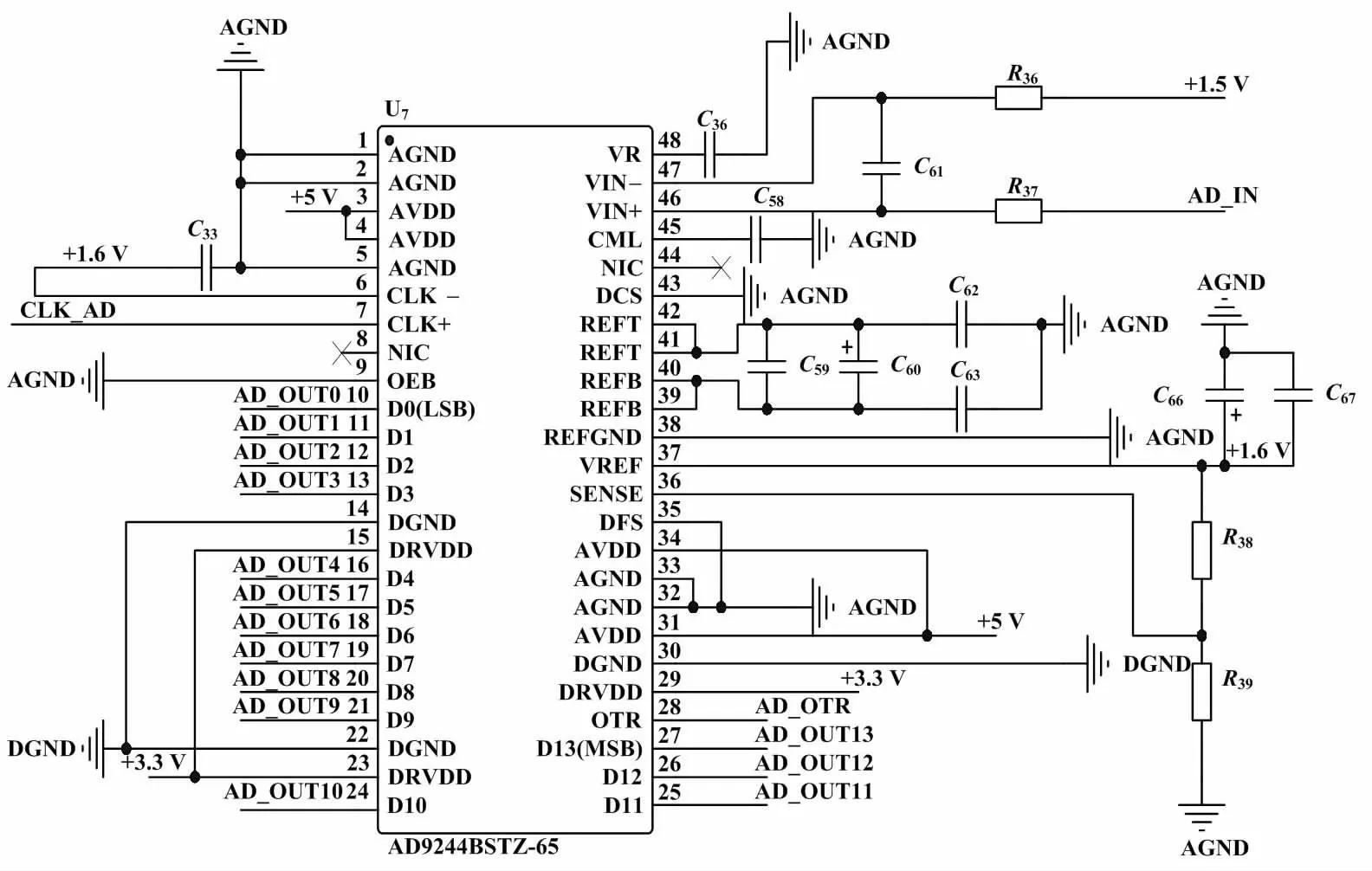

AD9244 A/D转换模块外围电路设计如图2所示。

图2 AD9244 A/D转换模块外围电路设计

AD9244 A/D转换时序如图3 所示。

图3 AD9244 A/D转换时序图

由于AD9244的转换时间tOD为4~5 ns,即AD9244在转换时间tOD范围后才可以输出稳定的数字信号。FPGA采样点应在数字信号稳定时进行采样。

AD9244的采样频率最高为65 MHz,周期为15 ns。在最高采样频率下,AD9244的下半周期数据理论稳定,所以FPGA应选择在时钟下降沿进行采样,从而保证获得稳定的数字信号。

2.4 选通电路优化

在数据采集系统中,选通电路是电极与激励测量回路建立链接的关键部分。在整体的激励测量过程以及选通过程中,若要提高信号频率并且加快开关切换速度,对开关芯片的导通时间、通路电阻、漏电流、隔离度以及通路切换时间都提出了一定的要求。对于当前使用的DG413这类隔离度较低的金属-氧化物-半导体(metal-oxide-semiconductor,MOS)开关芯片,在通路信号频率较高的情况下无法达到阻塞信号的作用。因此,要提高信号频率,必须更换当前使用的开关芯片。

目前常用模拟开关芯片的性能参数如表2所示。

表2 常用模拟开关芯片的性能参数

信号频率较高的电路除了对隔离度有较高要求外,对开关芯片中的导通电阻、通路切换时间也提出了一定的要求。常用的开关芯片中单刀单掷开关ADG1413以及单刀双掷开关ADG5433都基本满足要求。

若采用单刀单掷开关,则无需对原有的选通电路单元进行结构修改,只要将原有的DG413更改为ADG1413即可。

若采用单刀双掷开关,则可以有效减少开关数量。但这样仍需要针对漏电流问题进行电路结构调整,以消除其对测量结果的影响。

3 优化系统验证

为了验证本文方案对电阻层析数据采集系统的优化性能,测试先将FPGA的输出波形频率设置为160 kHz,再将AD9764与AD9240的采样频率设置为20 MHz,最后将RS485的波特率修改为2 Mbit/s。此时,整个系统的激励频率为160 kHz。本文利用优化后的电阻层析数据采集系统,对当前系统的信噪比进行静态试验验证。其中:静态水盆装置内径为16 cm;液相背景采用电导率为260 μs/cm的自来水。

激励大小设置为2 V。在纯液态下,试验连续采集1 000组测量值,并利用连续多组测量值数据对当前系统进行信噪比分析。

信噪比的计算式如下。

(2)

测量值序列由480个测量值组成。电阻层析测量系统的单组测量值结果如图4所示。

图4 电阻层析测量系统的单组测量值结果

若需要衡量整个电阻层析测量系统的抗干扰能力,则必须分别计算电阻层析数据采集系统对480个测量值的信噪比,再计算所有结果的期望,从而得到整个系统的信噪比。

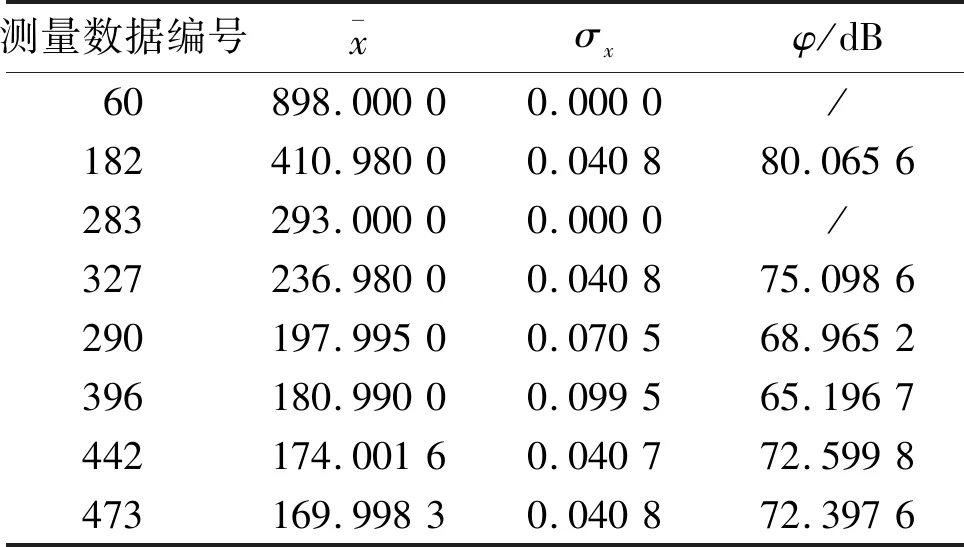

部分测量值的信噪比如表3所示。

表3 部分测量值的信噪比

由表3可知,大部分测量值的信噪比都在65 dB以上,且部分测量值在1 000组数据中没有任何波动。其标准差为0,信噪比很好。在计算所有测量值的信噪比期望时,信噪比为“/”的参数设置为100 dB,从而得到当前系统的信噪比为73 dB。综合上述分析,系统整体的信噪比相较于原有系统的52 dB得到了显著的提升。

4 结论

针对当前疏浚工程的测量要求,本文在现有电阻层析测量系统基础上,围绕电阻层析测量系统的传感器阵列、数据采集系统和上位机测量系统3个部分进行优化。首先,本文根据疏浚管道的实际工况以及电阻层析技术对传感器阵列的要求,对传感器阵列进行了耐久性、稳定性和抗干扰性方面的优化。其次,从电阻层析数据采集系统出发,分析了影响其信噪比以及采集速率的主要因素,分别从电路层面的3个方面进行了相关优化,并利用试验数据进行了采集系统性能的验证。验证结果表明,系统信噪比由原有的52 dB提升到了73 dB。最后,本文围绕当前数据采集系统的改进,分别对上位机的通信模块以及数据预处理模式作适配升级。整体优化后的电阻层析测量系统较原有系统性能得到了显著提升。