通导一体多址信号干扰源设计

李欣,马志刚

(中国电子科技集团公司第20研究所,陕西西安,710068)

0 引言

卫星导航系统由空间段、地面段和用户段组成,按照功能可将信号链路划分为下行导航信号链路、上行注入信号链路、站间时间/同步数据传输链路和RDSS出/入站信号链路,其中最后两个链路是北斗卫星导航系统特有的。卫星导航、通信系统各链路信号很多都是 CDMA 扩频信号,各路信号之间频谱重叠,引起了各路信号之间的相互干扰即多址干扰。随着全球卫星系统逐步发展完善,未来卫星总数将不断增加,此时多址干扰对卫星导航、通信性能的影响将不容忽视,尤其是当存在卫星信号功率增强时,来自强信号的多址干扰将显著影响到期望接收信号的捕获和跟踪;或者随着卫星运动多址干扰信号与期望信号的频率变化至特定关系时多址干扰形成的伪码跟踪误差非常显著。为了深入研究多址干扰对卫星导航、通信系统的影响,探索卫星导航、通信系统抗多址干扰的方法,本文基于软件无线电的思想,结合FPGA 的DDS 技术,应用动态重构技术,设计了卫星导航、通信一体化多址干扰源。为满足卫星导航、通信抗多址干扰性能验证,多址信号源主要用于卫星导航系统接收终端的抗多址干扰性能测试,最多可产生20 路多址信号,每一路的信号能够分别进行扩频调制、信道编码、载波调制、信号幅度控制,载波频率微调等信号处理,每路可产生一路可配置卫星导航、通信多址干扰信号,满足卫星导航系统导航、通信抗多址干扰性能验证的需要。

1 系统原理及整体方案

卫星系统中,导航信号和通信信号很多采用CDMA 码分多址方式,信号结构[1]大致可以分为载波、伪码、数据三个层次,卫星号为n卫星发射的标准卫星信号可以表示为:

式中:上标n表示卫星号;下标I、Q分别表示同相支路、正交支路;A表示载波振幅;C表示伪码;D表示数据码;φ 表示载波初相;f 表示载波频率;t 表示卫星发射时间。以卫星信号采用BPSK 调制方式为例,可表示为:

分解得:

其中:

多路多址信号叠加的数学模型可以表示为:

由上式可知,数字运算时先叠加后调制与先调制后叠加是相同的。在本方案采用先叠加后调制的方法,即先在FPGA 中把20 个通道的信号进行合成,得到包含20 个通道的数字基带信号,然后送到高速D/A进行转换得到模拟信号。

多址信号源由20 个并行基带处理单元、信号合路器、FIR 滤波器、数模转换(DAC)组成。基带处理单元完成对输入数据的编码、数据速率控制、扩频调制、成形滤波、BPSK 载波调制、信号功率控制等处理,信号合路器将20路基带信号合路为一路输出,FIR 对合路后的信号进行滤波,滤除载波带外的干扰,DAC 将数字信号转换成模拟信号,并将多址信号输出。多址信号源原理框图如图1 所示。

图1 多址信号源原理框图

多址信号源的20 个基带处理单元都可以独立处理,互不影响。基带处理单元采用LDPC 编码方式,来提高数传的纠错性能;直接序列扩频模块将输入数据与伪码相乘,得到新的基带数据,达到频谱展宽的目的;成形滤波是对展宽的信号做滤波处理,防止频谱内的码间干扰。载波调制模块采用BSPK 调制方式,将基带信号调制到中频信号;功率控制模块控制每一路基带信号的功率大小以及每路基带信号的输出开关控制,实现1 至20 路多址干扰信号的输出路数和输出功率控制。

2 基带硬件实现架构

多址干扰源采用单DSP 加双FPGA 为核心的硬件架构。DSP 作为核心控制中心,负责系统的运行综合控制,与上位机数据交互处理,协同FPGA 完成基带信号处理,控制LCD 显示、键控模块等;两块FPGA 各自完成10 路基带信号的编码、扩频调制、成形滤波、载波调制、功率控制等处理,最后通过信号叠加的方式将20 路中频信号合路,在FPGA1上做FIR 滤波处理;DAC 模块完成数字信号到模拟信号的转变;时钟控制单元为系统提供稳定的时钟信号;电源模块能同时产生12V、5V、3.3V、1.2V 四种电平的电压信号;LCD 和键控单元是人机友好交互的主要部分。多址信号源硬件架构如图2 所示。

图2 多址信号源硬件架构图

DSP 与FPGA 协同工作完成整个多址干扰源的数据、信号处理工作,DSP 作为数据处理和控制单元,FPGA 作为信号处理单元。DSP 将上位机的发送数据进行解包分组,根据FPGA 的处理速度给FPGA 传送数据,并执行各个基带单元编码器的控制,DSP 控制FPGA 基带信号的启动路数和功率调整以及载波频偏的调整。FPGA 根据DSP的控制指令及自身的反馈,来完成整个基带信号的核心处理,两块FPGA 并行工作,产生出测试所需的多路多址干扰信号。

3 基带信号处理设计

多址干扰源基带信号处理充分利用动态可重构的杂干扰信号产生技术,支持动态、灵活可配置的产生多种类型干扰信号、组合干扰信号产生技术研究。基带信号处理是通过DSP 和FPGA 完成,DSP 主要负责数据组帧、通道配置、码控制、载波控制等处理,FPAG 主要包含前项纠错编码、扩频调制、滤波、数字载波调制等。

针对导航、通信选择的前项纠错编码是码率1/2 LDPC码,但校验矩阵的特点差别比较大,将校验矩阵先存到FPGA 的Rom 内,DSP 调用相应的编码器时,选择相应的校验矩阵参数,完成编码。

数字载波调制主要是载波信号生成,载波信号产生模块的核心为载波NCO,用于产生主波形(载波),载波NCO[2]采用的就是DDS 技术,具有精确的频率分辨率、快速的转换时间等优点,它的结构包括相位累加器和正弦查找表两部分。载波NCO 模块接收DSP 送来的载波频率控制字、载波相位调整字,实现动态数字中频载波的产生。

伪码都是gold 码,通信类有一个专用模块产生伪随机系列,直接有DSP 控制器输出,通过调整码NCO 调整其输出状态,导航伪码的产生都通过多项式来生成,模块有GPS、北斗的伪码产生模块,由DSP 负责完成调用控制,在此以北斗为例介绍伪码的产生方式。北斗B1 频段测距码周期为1ms,码长为2046 个码片,码速率为2.046Mcps。B1 频段I 支路的测距码是由两个线性序列G1 和G2 模2 相加后截短1 个码片生成的,北斗测距码生成原理如图3 所示。G1 和G2 序列两个11 级的线性移位寄存器实现,生成多项式如下:

图3 北斗测距码生成原理

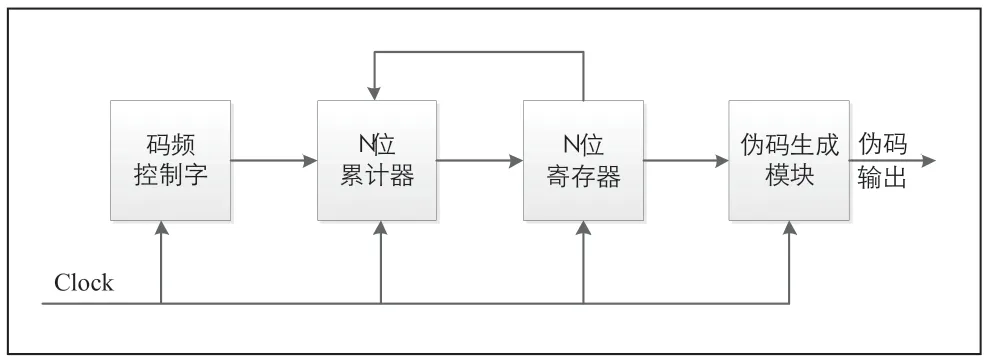

伪随机码生成模块的核心是码NCO,码NCO 能产生伪码生成所需的频率,它具有频率分辨率高、频率切换速度快等优点。码NCO 相位累加器的工作原理与载波NCO 类似。相位累加器在每一个时钟CLK 输入的时候,将输入的频率控制字与之前一个CLK 的相位累加器中的相位数据进行累加,每一次相位累加器的最高位溢出数据,就是系统所需要的码NCO 频率。相位累加器的溢出频率,驱动存有伪码信息的存储器(ROM 表),输出所产生的伪码。码NCO 不仅仅是实现简单的测距码输出,还是精确伪距实现的关键模块。码NCO 原理图如图4 所示。

图4 码NCO 原理图

码NCO 累加寄存器位宽N 与系统伪距模拟精度Δρ 的关系为,其中Tcode为伪码码元宽度。

本设计中,取码NCO 累加寄存器位宽与载波NCO 相同,为32bit,使二者在同一系统时钟下具有相同的频率分辨率,且能充分保证伪距模拟精度的要求。

4 系统测试

按照本文设计,项目中已实现该方案,并完成测试,该多址信号干扰源需要输入10MHz、1PPS 的输入信号,可通过频谱分析仪来测试其输出中频信号波形,测试原理框图如图5 所示。

图5 多址信号源测试原理框图

测试将中频输出信号接到频谱分析仪,可以看到单路单载波信号和扩频信号,如图6 所示。

图6 中频输出单载波和扩频信号

5 结束语

基于软件无线电设计思想,本文设计的多通道干扰信号产生器,每个通道均能独立进行参数重配置,产生不同样式的干扰信号,具有较强的灵活性和通用性。另外,针对不同的应用需求,对信号产生模块可方便地进行裁剪,以优化资源,集成更多的信号产生模块。