基于相位差原理的抑制3k次谐波差分N通道滤波器

陈佳佳

(常州铁道高等职业技术学校,江苏 常州 213011)

0 引言

随着CMOS和无线通信技术的快速发展,多模多频接收机对滤波器的要求也越来越高,传统滤波器具有中心频率不可调、体积大和不易集成等缺陷,导致其已不再满足射频接收机提出的高要求[1-3]。因此,N通道滤波器凭借着中心频率可调、线性度高和回波损耗少等优势[4],广泛应用于多模多频射频接收机前端。

近几十年,N通道滤波器的研究再一次获得关注,在理论和结构层面都取得了一定进展。但在具体应用中仍然存在着由时钟采样特性引起的谐波干扰问题,尤其是奇次谐波的干扰正面临重大挑战。因此,谐波抑制特性良好显得极为重要。

20世纪60年代初,N通道滤波器被首次提出,它的通道数为N,输出的传递函数显示N及N的整数倍谐波被抑制的形态,设置特定通道数则消除特定谐波[5]。

2017年,何小莲等[6]提出一种增益提高型差分N通道带通滤波器,采用差分结构使偶次谐波得到抑制,采用米勒反馈原理,使电容面积减小。此结构提高了中心频率处的电压增益,但同时也增大了不需要的谐波增益。同年,Hemati等[7]提出了带阻加带通级联的结构,在带通滤波器之前放置一个带阻滤波器,通过带阻和带通级联的方式消除N通道带通滤波器不需要的k次谐波。但此设计给采样时钟信号的产生加大了难度,同时也增加了电路的静态功耗。

2020年,Rayudu等[8]提出了一种含有双开关结构的N通道滤波器,使得导通电阻Ron不会在滤波器输出端与源电阻Rs产生分压,减小了带外信号的幅值,从而提高了滤波器的带外抑制能力。

2020年,Karami等[9]设计了一款基于多相合成技术的3路8通道带通滤波器,能够抑制3次和5次谐波,但此过程中的矢量运算过于复杂易出错,且电路结构复杂,不利于节省芯片成本。

综上所述,设计一个谐波抑制性能较好且其他综合性能较强的N通道滤波器是一个重大挑战。因此,本文提出了一款抑制3k次谐波差分6通道滤波器,该滤波器通过单端转双端的差分结构抑制偶次和3k次(k为正整数)谐波,两个跨导放大器用于电压求和与提高增益,片外变压器用于阻抗匹配,提高Q值。与近年来其他相似设计比较,该滤波器具备良好的谐波抑制特性,且具有良好的线性度和噪声抑制能力。

1 电路设计

本文设计的差分6通道滤波器由基于相位差原理的单端转双端结构、跨导放大器以及片外变压器构成,完整电路图如图1所示。图中的单端转双端6通道滤波器主要基于时钟相位差原理,时钟相位差关系如图2所示,在本振(LO)时间范围内输入所需信号和不需要3次谐波通过滤波器不同路径时所需的时间。图片顶部显示了时钟相位间隔(间隔为60°),如果两个输出具有120°或240°的相位差,则这两个输出相减,3次谐波及其整数倍在输出端将被抑制;如果将两个具有60°相位差的输出相加,3次谐波及其整数倍中的奇次谐波在输出端将被抑制。本设计依据60°相位差原理,并引入具有180°相位差的MOS管作为开关,构成差分结构来消除偶次谐波,从而保留所需信号。

图1 差分6通道滤波器完整电路图

图2 时钟相位差关系图

此滤波器与一般的单端转双端结构类似,区别在于此滤波器的每条路径用于上变频的第一组开关Si和Si+1具有60°的相位差,作为两个输出,相加用于抑制奇数3k次谐波。与第一组相位相差180°的另一组上变频开关Si+3和Si+4作为和两个输出,用于抑制偶次谐波。因此,总的输出电压为:

在6通道滤波器中,由于采用6相非重叠采样时钟信号,连续且相邻的采样开关时钟相位延迟TLO/6,因此,若已知采样开关时钟Si(t),其他采样开关表达为Si+a(t)=Si(t-aTLO/6),经傅里叶求和可得:

通过傅里叶变换推导和运算,得出该滤波器输出电压的频域表达式:

由式(3)可知,当n=3k且n为偶数时,输出电压为0,表明滤波器的3k次谐波和偶次谐波在输出端被抑制,对于所需信号即n=1时,系数的绝对值(1+e-jπn/3)(1-(-1)n)近似等于增益有所增加。

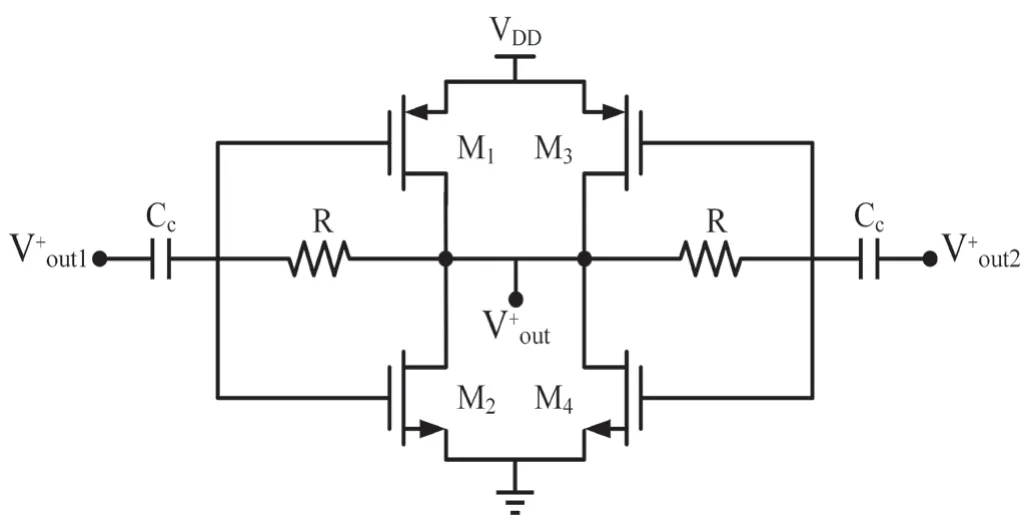

式(1)的电压求和由带有两个自偏置电阻和耦合电容的跨导放大器完成,如图3所示,单个跨导放大器的正端输出电压表达式为:

图3 跨导放大器

ɡm1和ɡm2分别是晶体管M1,3和M2,4的跨导值,ro1、ro2对应的是它们的输出电阻,输出电阻值通常由CMOS管的宽长比W/L计算求得,当自偏置电阻R远比输出电阻ro1、ro2大时,式(4)可化简为:

Rout表示晶体管总的等效输出电阻,Rout=1/2×(ro1||ro2),负端输出电压同理可得,但与正端相比,大小相同、符号相反,此结构的总输出电压由正端之和减去负端之和,有益于提高整体增益,本设计的增益达到10 dB,最后输出信号经过片外变压器达到阻抗匹配的目的,从而减小了回波损耗。

2 仿真结果和对比

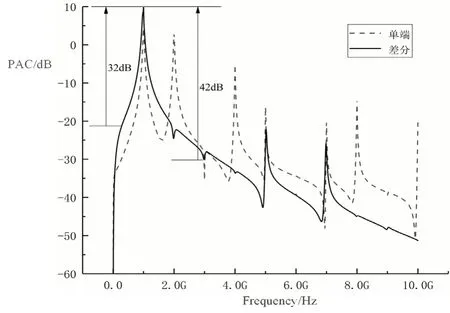

对本文设计的差分6通道滤波器电路结构进行仿真验证,图中涉及的NMOS开关管大小尺寸设定为W/L=25 μm/40 nm,每个NMOS开关采用占空比为1/6的6相非重叠时钟驱动。在TSMC 40 nm CMOS工艺和1.1 V电压下,采用Cadence Spectre RF仿真工具对该滤波器进行PSS、PAC、噪声和线性度仿真分析。中心频率fs=1 GHz对应的传递函数曲线如图4所示,由曲线图明显看出本文设计的差分6通道滤波器与单端结构相比较,较难抑制的3次和5次谐波在本设计中得到了较好的抑制。其中,3次谐波抑制高达42 dB,带外抑制达到32 dB,充分表明该滤波器的谐波抑制性能较好,由于使用含有自偏置电阻和耦合电容的跨导放大器,使得有用信号的增益高达10 dB。经过S参数仿真,如图5所示,该滤波器频率可调范围从200 MHz到1.1 GHz,具有900 MHz的调谐宽度,包含了许多无线低频段通信设备的中心频率点。如图6所示,此滤波器在频率可调范围内的噪声系数NF整体低于6 dB,表明此滤波器具有良好的噪声抑制能力。如图7所示,在频差范围50 MHz~150 MHz之间的带内IIP3都大于8 dBm,说明此滤波器的带内线性度较好。

图4 传递函数曲线(fs=1 GHz)

图5 中心频率可调范围

图6 噪声系数NF

图7 带内线性度IIP3

本文与近几年类似文献的对比数据如表1所示,从表1来看,笔者设计的这款滤波器的参数指标均符合部分无线低频段通信设备的要求,具体的突出优势表现在:3次谐波抑制高达42 dB,带外抑制达到32 dB,虽然在工艺上存在偏差,但就各项综合指数而言,整体性能较好。

表1 本文与近几年类似文献的参数对比

3 结束语

本文在TSMC 40 nm工艺、1.1 V供电电压下设计了一款基于时钟相位差原理的抑制3k次谐波差分6通道滤波器。该滤波器由单端转双端的差分6通道滤波器、两个跨导放大器和片外变压器构成。单端转双端的差分6通道滤波器抑制3k次(k为正整数)和偶次谐波,跨导放大器用于提高增益,片外变压器用于阻抗匹配以提高Q值。Cadence Spectre RF仿真结果显示,中心频率在200 MHz~1.1 GHz可调,3次谐波抑制高达42 dB,带外抑制达到32 dB,噪声系数NF小于6 dB,带内线性度IIP3大于8 dBm,与其他文献参数相比,该滤波器具备良好的谐波抑制能力,且其他综合性能也较好,在多模多频射频接收机前端有着良好的应用前景。