基于FPGA的音频数模混合AGC采集系统

郭栋梁,张晓荣,李晓飞

(山西大众电子信息产业集团有限公司技术研发中心,山西 太原030051)

0 引言

在音频采集系统中,受声音传播距离的远近、声源的稳定性以及其他声音干扰等因素的影响,接收到的声音信号往往忽大忽小,所以衡量一个音频采集系统好坏的重要指标就是是否能够对采集信道进行实时的增益控制。

一般的模拟AGC电路由可变增益放大器(VGA)、耦合器、检波器、低通滤波器(LPF)等元件组成,由检波器产生直流电压控制可变增益放大器,从而达到对外部信号进行增益控制的目的。目前模拟AGC技术较为成熟,应用广泛,对外界变化不敏感、但缺点也很明显,就是响应时间长。

数字AGC主要是通过MCU与控制算法,实现AGC系统中所需要的滤波、检波以及比较等工作[1]。当外部的输入信号存在较大的动态范围时,响应时间仅取决于算法时间开销以及数字器件的响应时间[2-3]。然而受限于ADC器件的限制,在输入电平过小时,ADC输出容易出现误码,影响AGC系统性能。

基于数字增益与模拟增益各自的优缺点,本文提出了一种数模混合增益的设计方法,首先通过模拟开环结构解决AGC收敛速度的问题,再通过数字闭环结构确保AGC输出信号的输出精度,该设计方法既有模拟增益的稳定性,又兼具有数字AGC响应速度快的优点。

1 系统硬件设计

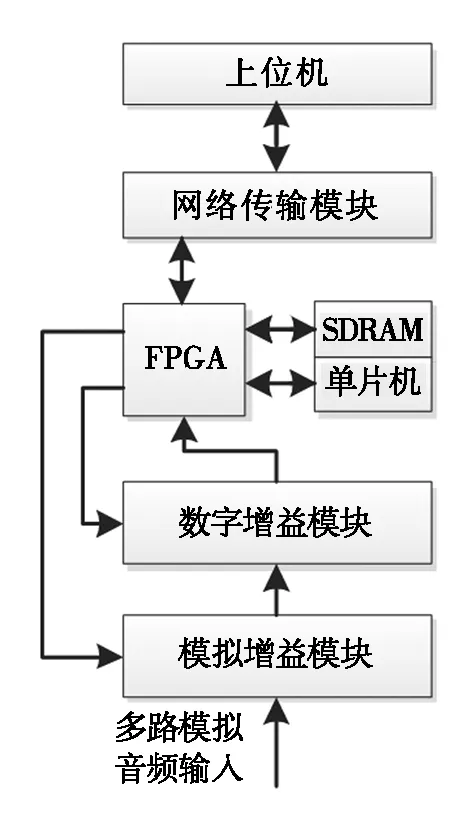

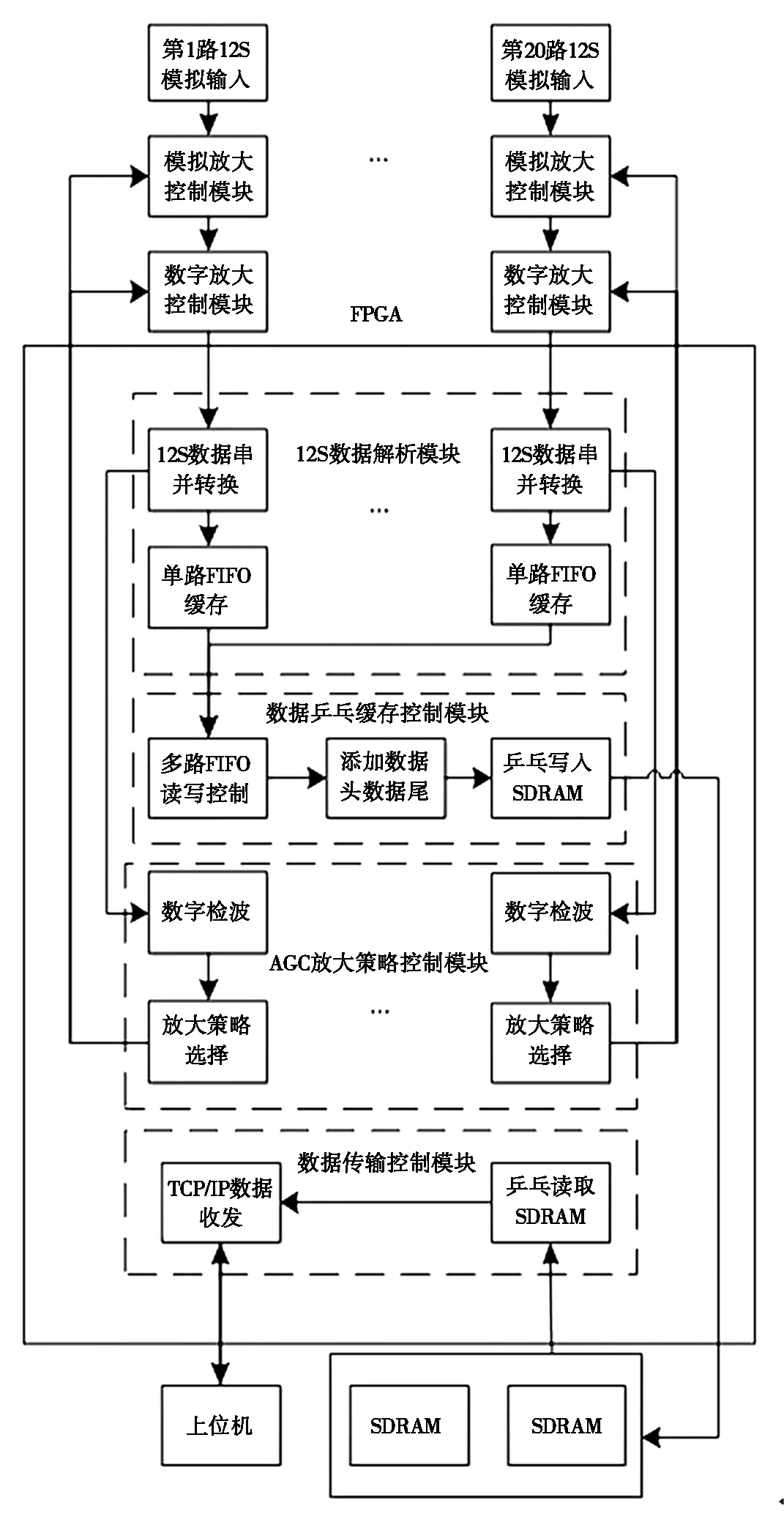

该系统的硬件主要由上位机、网络传输模块、FPGA、SDRAM、数字增益模块以及模拟增益模块组成。其系统硬件框图如图1所示。

图1 数模混合AGC采集系统硬件框图

在该系统应用中,外部微弱的模拟音频输入信号首先经过低噪声模拟增益模块进行模拟增益,之后通过高性能模数转换器ADAU1977进行模数转换,将模拟音频信号转换为串行的I2S数字信号。FPGA对I2S信号进行解析、检波、滤波后,乒乓SDRAM缓存数据,之后通过网络传输模块将数据发送给上位机,上位机将数据解析后显示出来;FPGA同时进行放大策略的选择,通过FPGA控制模拟增益模块与数字增益模块的放大系数,达到自动增益控制的目的。

1.1 模拟增益模块电路设计

模拟增益模块电路在系统中完成音频增益的粗调。模拟AGC由前端放大电路和可变增益后端放大滤波电路组成。

前端放大电路芯片采用高精度斩波稳零运算放大器TLC2652,在TLC2652内部,存在主放大器和校零放大器,从而失调电压及其漂移、工模电压、低频噪声对运算放大器的影响降到最小,使得TLC2652非常适合微弱信号的放大。

可变增益后端放大滤波电路主要有运放AD8253构成。AD8253是一款可编程增益放大器,具有低输出噪声、高共模抑制能力、低增益漂移的特性[4]。CTRL_A、CTRL_B为数字可控增益引脚,通过FPGA编程控制,可实现1/10/100/1000倍的低噪声可控模拟增益。

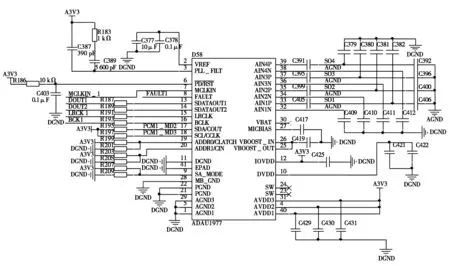

1.2 数字增益模块电路设计

模拟增益模块电路在系统中完成音频增益的粗调,数字部分采用高性能可变增益模数转换器ADAU1977来完成。数字增益模块电路设计如图2所示。

图2 数字增益模块电路设计

ADAU1977是一款高性能模数转换器,它具有输出噪声低、共模抑制比高、增益漂移低等优点。系统上电工作时,FPGA通过I2C接口配置ADAU1977的寄存器,使得ADAU1977能够同时完成8路模拟音频信号的模数转换,并且它的转换精度为24位,采样速率最高为192 kHz;内置可控数字增益通道,通过FPGA写入ADAU1977的寄存器,可实现快速可控的数字增益,数字增益的动态范围为-35.625 dB~60 dB,单次增益步长为0.375 dB。

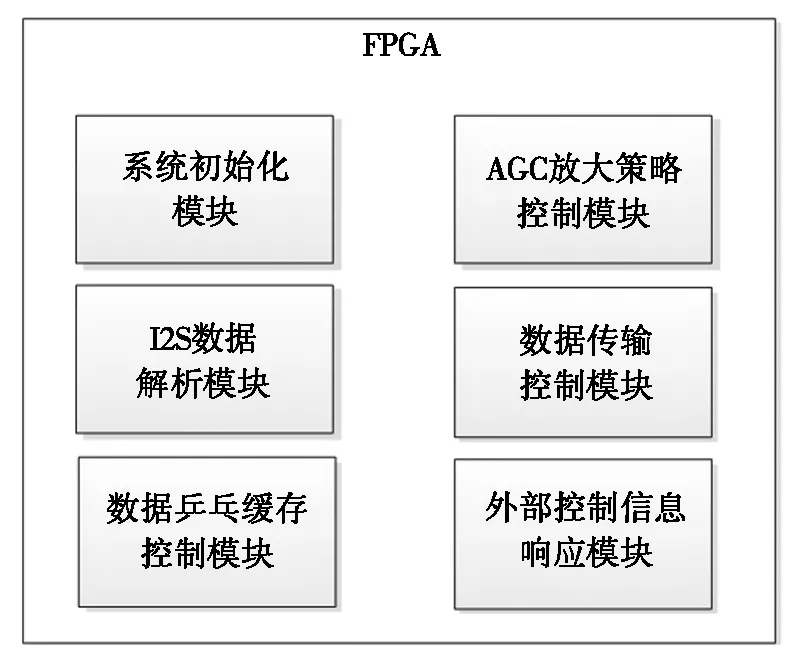

2 音频采集系统控制程序设计

音频采集系统控制程序由FPGA完成,其主要由系统初始化模块、I2S数据解析模块、数据乒乓缓存控制模块、AGC放大策略控制模块、数据传输控制模块以及外部控制信息响应模块组成。音频采集控制程序框图如图3所示。

图3 音频采集控制程序框图

系统初始化模块的功能是完成5个ADAU1977芯片的寄存器配置、完成1个网络芯片W5300的寄存器配置、复位程序内部寄存器;I2S数据解析模块的功能是完成多路音频数据串并转换、多路音频数据的FIFO缓存;数据乒乓缓存控制模块的功能是将多路缓存FIFO中的数据读出,添加每一路数据对应的数据头数据尾,并将数据通过乒乓操作的方式写入两片SDRAM中去;AGC放大策略控制模块主要负责判断I2S数据解析模块解析出来的数值,通过AGC算法来进行放大策略的选择,从而分别控制模拟增益模块和数字增益模块;数据传输控制模块主要负责将SDRAM中缓存的数据通过乒乓操作的方式将数据读出,通过网络芯片W5300将数据通过TCP/IP协议发送出去;外部控制信息响应模块主要负责响应外部按键信息以及上位机通过网络芯片发来的控制信息,将上述信息解析后下发至各个功能模块。音频采集系统程序工作流程图如图4所示。

图4 音频采集系统程序工作流程图

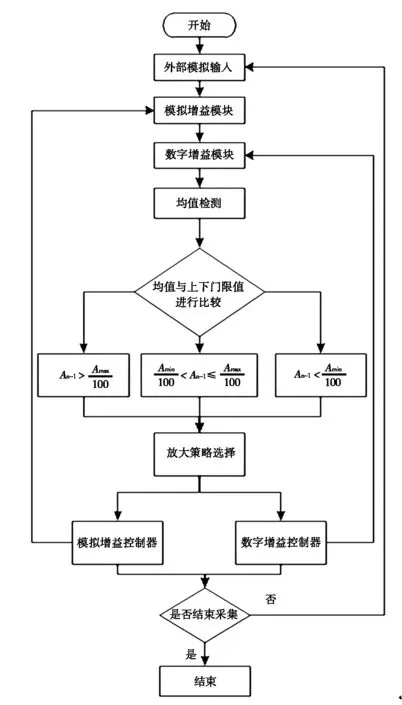

3 数模混合音频AGC控制的实现

自动增益控制(automatic gain control),即AGC,是根据输入信号的大小而自动调整放大电路的增益以达到稳定的输出。在该系统中,采用数模混合AGC完成音频AGC的控制。在传统AGC系统中,往往采取单门限来进行幅值的比较,进而确定增益倍数。这种情况下,由于输入信号可能会在单门限值附近上下震荡,引起AGC系统频繁的切换增益倍数,造成系统稳定性差,从而影响数据接收的稳定性[5]。在该算法中,采取了上下双门限的设定,上下门限值之间有一个较为合适的缓冲区区间,这就一定程度上避免了系统的震荡,提高了系统的稳定性[6-7]。在该音频采集系统中,数模混合AGC增益计算公式可表示为:

An=Ain×Ganalog×Gdigital

.

(1)

模拟增益放大倍数Ganalog的定义为:

.

(2)

上述式中,An为信号经过模拟增益、数字增益后的幅值;Ain为输入信号的幅值;Amean为上一时间段内(一般取512个点)信号的平均幅值;Amin为期望的幅值的下限;Amax为期望的幅值的上限;Ganalog为模拟增益放大倍数;Gdigital为数字增益放大倍数。

数字增益放大倍数Gdigital的定义为:

.

(3)

在该系统进行数模混合AGC增益控制时,I2S模拟输入信号首先经过模拟增益电路进行放大,模拟增益倍数的确定如式(2)所示。然后模拟信号进入ADAU1977,完成模数转换的同时,FPGA通过I2C接口配置ADAU1977内部寄存器,从而控制数字增益放大倍数。数字增益倍数的确定如式(3)所示。数模混合AGC控制流程图如图5所示。

图5 数模混合AGC控制流程图

4 上位机软件设计

该系统的上位机软件采用Qt作为开发平台,完成网络配置、增益模式配置、数据监控、数据记录及数据导出。

软件在运行时首先与设备内网络芯片完成TCP/IP协议的握手,然后将增益模式、手动放大倍数以及放大校正系数通过网口下发至FPGA中。之后监听网口数据,在收到有效数据后,将20路音频数据解析并显示在界面上,同时将20路音频数据按照采集时间进行命名,存储至设备内部的硬盘中去。

5 结论

本文基于可编程逻辑门阵列、低噪声模拟放大器与高性能模数转换器,实现了多路微弱音频信号的采集与灵活的数模混合AGC采集系统。该系统能够同时采集20路mv级的模拟音频输入,使用的数模混合AGC电路及算法,将20路音频信号放大至预期的区间中去,之后将数据通过网络发送至上位机,将音频数据进行显示与存储。经验证,该多路音频数模混合AGC采集系统具有响应时间短、收敛速度快、动态范围大、数据可靠稳定等优点,总体性能优于传统AGC。