PowerPC+FPGA视频传输设备设计方法

夏宁 连锦波 何桃桃 何明雪

摘要:文章研究的场面监视雷达回波数据用于录取终端的数据处理,通过对回波数据的处理,实现目标的识别、跟踪、显示等。该设计方法,实现场面监视雷达的视频网络化传输,将雷达数据传输至塔台中心,并配合专用显示软件实现回波数据的展示,便于操纵人员观察及数据的处理。

关键词:场面监视雷达;PowerPC系统;可编程逻辑器件

中图分类号:TN791;TP393.11 文献标志码:A

0 引言

场面监视雷达主要用于监视机场飞机、车辆等运动物体的雷达、是保障机场在低能见度及视线遮挡情况下正常运行的基础设施[1]。场面监视雷达一般安装于机场塔台,通过雷达天线发射的电磁波,其中,目标产生的二次反射被接收机接收后进行回波处理,从而发现目标。通常,场面监视雷达将回波信号发送至配备的录取终端[2],实现雷达回波的显示、目标跟踪、观察等功能。

1 视频传输设计工作流程

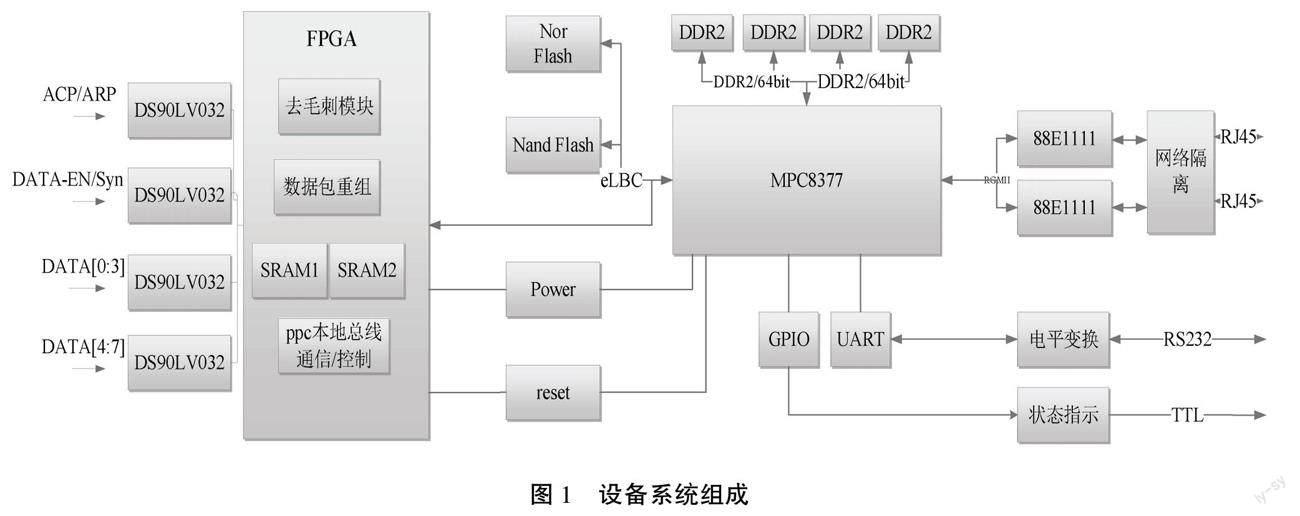

场面监视雷达视频传输设计流程如图1所示。前端雷达将方位信号(ACP\ARP)、数据使能信号(data-en)、触发脉冲信号(syn)、8 bit视频信号以及同步时钟信号接入到电平转换电路,将差分LVDS信号转换成TTL信号,TTL信号接入FPGA系统内部进行上述数据的重组。重组后的数据通过FPGA与PowerPC之间的传输总线传输至PowerPC后,进行数据的网络化处理,将其送至录取终端进行跟踪、录取、显示处理。录取终端将目标信息提供给机场高级地面活动引导控制系统,供机场交通管制使用[3]。

2 系统设计

2.1 FPGA数据包设计

为保护FPGA的IO口免受外部信号的不稳定而导致的损坏,将TERMA雷达输出的雷达方位信号(ACP\ARP)、数据使能信号,触发脉冲信号以及视频数据信号经过LVDS转TTL芯片后接入FPGA的IO端口。使用电平变换芯片DS90LV032A,该芯片可实现4路cmos差分信号接收转换为TTL电平,200 MHz转换速率,各通道间偏差小于0.1 ns,可满足要求。在实际工程应用中,雷达信号通过线缆传输至设备端可能存在干扰信号,为保障信号的有效处理,在接入FPGA内部后,需对数据使能信号、方位信号进行消除毛刺处理。消除干扰“毛刺信号”原理是将信号分别向后延迟一个时钟节拍和两个时钟节拍,将延后的两个信号与原始信号进行与操作,得到的信号作为后级数据包重组输入信号。

数据包重组,实现方位信号、触发信号、视频信号的重组,便于将前端的流数据进行缓存处理后,写入FPGA内部2个RAM空间,实现乒乓操作。流数据进行重组数据格式如下:数据使能(触发)对应的数据格式,按照如下参数进行设计,信息单元标识、触发信息单元长度、时戳、触发长度、采样频率、方位码位数、视频位数、视频起始单元、视频信号数据个数以及N个视频信号数据。其中,信息单元标识为每一个数据使能(触发)数据开始标志(02A4)表示,触发信息单元长度表示该数据使能包含的所有信息的长度(字节表示),时戳表示该数据触发数据获取的时间,精度0.1 ms;触发长度通过内部时钟计算出该数据使能(触发)信号的时间信息,单位μs,方位码表示该acp/arp表示360°分成4 096或8 192个方位,即12位或13位。视频位数表示每一个数据是bit数据,视频起始单元表示后面的视频信号数据第一个数据的起点位置,视频信号数据个数表示后续的视频信号数据的个数;视频信号数据表示采集的视频数据。

一个网络包设计为不大于64 kB,故一个网络包可以包含多个触发数据格式。其网络包数据格式如下:网络包长度、目的地址、源地址、网络包种含触发个数N、网络包顺序、触发数据格式1、触发数据格式2……触发数据格式N。

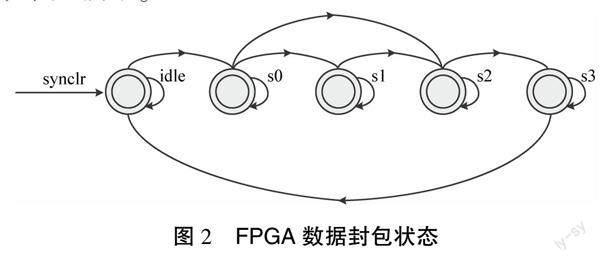

上述设计的一种网络数据包格式,为便于UDP数据包最优效率,网络包大小不大于64 kB。在FPGA接收外部数据按照网络包格式存储在内部2个64 KBRAM存储器中,并通过实时存储器地址,判断剩余空间是否满足下一触发数据存储。当64 kB剩余空间不足以存储下一个触发数据时,结束该网络包的触发数据写入,并将网网络包中的网络包长度,目的地址、源地址以及网络包中触发个数和该网络包的包序。根据上述设计,FPGA内部的逻辑设计状态机如图2所示。

(1)idel状态:每个数据使能或触发的使能开始状态,保存触发或数据参数信息至寄存器,如视频采样位数、视频个数、触发长度、触发个数等。

(2)S0状态:写入按照顺序地址保存的参数信息,当写入的触发个数满足數据包封包大小,状态跳转至S1,否则状态跳转至S2,进行内部存储器空间容量判断与地址处理。

(3)S1状态:当s1写入数据满足封包大小,写入数据包的头部网络参数,内容如表2所示,封包结束跳转至状态S2进行内部存储器空间容量判断与地址处理。

(4)S2状态:获取当前触发的IDEL状态下的参数信息;判断该数据封包是否满足64 kB大小,如不满足进行地址递增,用于后续雷达数据写入。

(5)S3状态:进行数据记录处理,并统计记录数据个数信息、地址信息,用于S0状态参数写入以及回写地址计算。

2.2 数据包通信设计

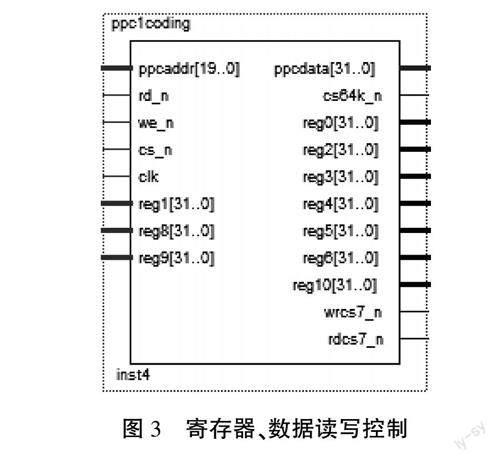

数据包设计后,通过内部的SRAM存储空间进行数据的存储,当64 KB的存储空间满足条件后需将其发送至PowerPC系统。FPGA与PowerPC之间通过本地局部总线进行数据传输,同时通过该总线PowerPC可对FPGA内部的功能模块进行控制。FPGA主要设计软件版本寄存器、复位寄存器、模拟测试寄存器、数据包源地址\目的地址寄存器、雷达信号故障告警等。本地局部总线包含读信号、写信号、片选信号、方向控制信号、时钟信号等。经测试局部总线带宽20MB/s,满足雷达视频数据接入、输出能力。寄存器控制及数据读取控制模块,如图3所示。数据封包模块,如图4所示。该设计所消耗的资源,从中可以看出FPGA资源充分,满足要求,如图5所示。

2.3 PowerPC系统设计

PowerPC包含一颗主处理芯片MPC8377E[4],该芯片接口丰富,含有2个RGMII/RMII/MII/RTBI接口,2个PCIE接口、2个SATA接口,1个32/64位DDR2控制器,32位加强型局部总线,最高频率133 MHz,串口、IIC接口等。芯片主频最高可达800 MHz,32 kB指令Cache,32 kB数据Cache,支持浮点运算。同时,主芯片具备低功耗特性,典型功耗为4 W。NorFlash,NandFlash挂载在局部总线eLBC上,NorFlash選用S29GL256P101系列,用于存储uboot、内核、文件系统等固件;NandFlash选用K9F5608U0D系列,作为用户存储接口,用于存放业务程序,每次系统运行后将业务程序读取至内存运行。4片DDR2内存颗粒,位宽为16,容量为1GB,内存总容量为512 MB。MPC8377E通过RGMII接口与网络PHY芯片88E1111进行网络通信;同时,CPU自带GPIO、串口等低速接口用于状态指示与调试。

PowerPC系统通过本地eLBC总线实现与FPGA系统数据通信,PowerPC系统将FPGA的打包数据读取至系统内存,并通过网络接口发送至远端的录取终端。系统采用双网口冗余设计,当某一网络发生故障时,可通过另一网络进行数据传输,切实有效保障设备的稳定可靠运行。

局部总线读写数据时序,如图6所示。因数据线和地址线为复用,通过LALE进行地址锁存,即LALE高有效,LAD输出数据为地址数据,对应FPGA逻辑控制模块中ppcaddr地址,LBCTL作为LAD总线的方向控制信号,高低代表读和写,故使用LBCTL作为读写控制型号。

3 设备实装效果

该设备已配备在南京禄口机场,郑州机场、浦东机场、萧山机场、厦门机场等塔台控制系统中。禄口机场通过该设备传输的视频与机场地图叠加显示。

4 结语

本文设计的设备已广泛应用在机场雷达的视频传输系统中。在实际使用中,遇到部分机场网络条件有限,不能实现现有网络化视频的传输,在设备的PowerPC系统中加入lz4压缩算法,极大地减少网络数据量,降低网络带宽占用,提升设备的适应能力。同时,该设备的设计思想已成功应用在其他传感器视频传输领域。

参考文献

[1]张睿,孔金凤.机场场面监视技术的比较及发展[J].中国西部科技,2010(1):34-35,52.

[2]赵海波,董昀.场面监视雷达系统在浦东国际机场的应用[J].中国民用航空,1999(2):48-50.

[3]嵇亮亮,郝延刚,叶玲,等.杂波图在场面监视雷达录取终端中的应用[J].江苏科技信息,2015(19):57-58.

[4]孙东亚,张亚棣,李亚辉,等.一种PowerPC和FPGA结构的远程接口单元设计方法[J].航空计算技术,2015(2):118-121.

(编辑 姚 鑫)

PowerPC + FPGA video transmission equipment design method

Xia Ning, Lian Jinbo, He Taotao, He Mingxue

(Nanjing Rice Electronic Equipment Co., Ltd., Nanjing 210007, China)

Abstract: The surface surveillance radar echo data studied in this article is used for data processing in the acquisition terminal. By processing the echo data, target recognition, tracking, display, etc. are achieved. This design method achieves video network transmission of surface surveillance radar, transmits radar data to the center of the tower, and cooperates with dedicated display software to display echo data, facilitating observation and data processing by operators.

Key words: scene surveillance radar; PowerPC system; programmable logic device