一种宽输入隔离式DC/DC 变换器设计

吴 磊,胡 进

(中国电子科技集团公司第四十三研究所,安徽 合肥 230088)

1 隔离式DC/DC 变换器的设计指标

随着国产装备的发展,整机系统对直流/直流(Direct Current/ Direct Current,DC/DC)变换器的需求越来越多。在DC/DC 变换器领域,常用的中低压输入直流母线电压有12 V、24 V、28 V、42 V 等几种,很多系统通常会出现多种直流母线电压共存的情况,从而给系统选型带来诸多不便,用户迫切需求一种宽输入电压范围DC/DC 变换器产品,可以满足其对上述不同输入母线电压的需求,进而实现器件选型标准化。针对上述需求,设计了一款输入电压8 ~50 V,15 V/2 A输出的隔离式DC/DC 变换器,其设计指标如表1 所示。

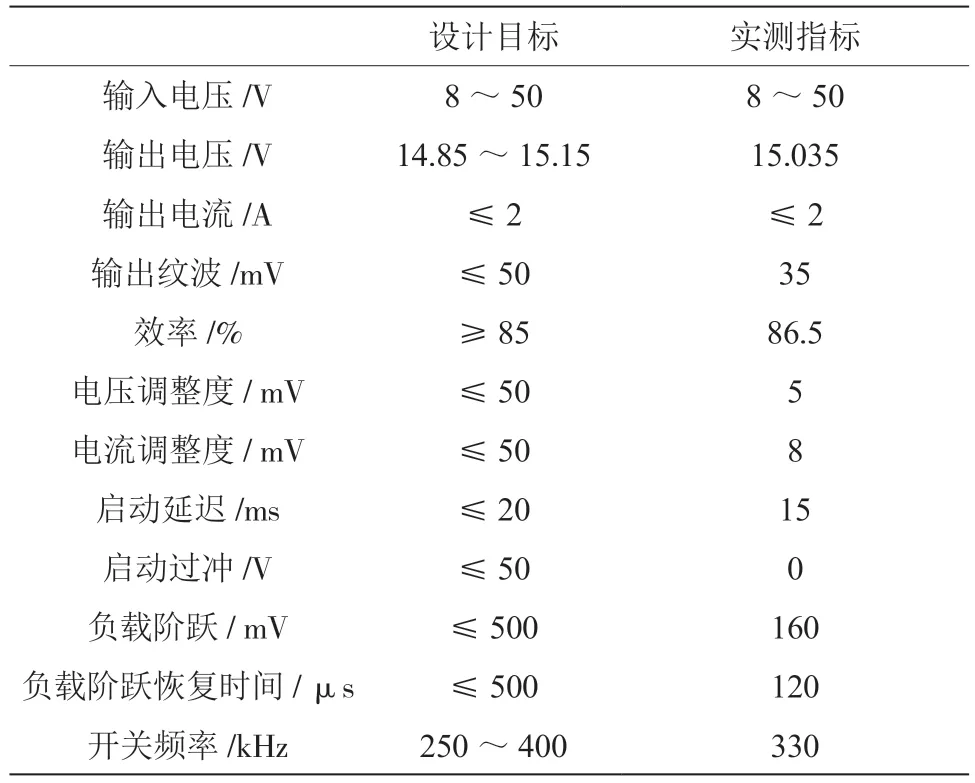

表1 隔离式DC/DC 变换器的设计指标

2 电路方案及工作原理

2.1 电路方案

电源拓扑结构是DC/DC 电源的基础,是DC/DC电源设计的具体实现形式[1]。对于宽输入隔离式DC/DC 变换器,常用的设计方案有2 种,一种是级联式拓扑结构设计,另一种是单端反激式拓扑结构设计。级联式拓扑结构的优点是控制电路简单,电路效率实现较高,缺点是电路结构相对复杂,不利于小型化;单端反激拓扑结构的优点是电路结构简单,易于小型化,缺点是电路控制相对复杂,且效率较低。由于电源对产品尺寸要求较高,设计中采用了单端反激拓扑结构。

开关电源常见的反馈方式有光隔离反馈和磁隔离反馈2 种[2]。其中,光隔离反馈依靠光耦将输出电压误差信号从主变压器的副边隔离反馈到变压器的原边,磁隔离反馈利用脉冲变压器将输出电压的误差信号从主变压器的副边反馈到原边。考虑光耦的电流传输比在外部环境恶劣,容易产生变化,影响DC/DC变换器的性能,本设计最终选择磁隔离反馈的方式。因此,本设计最终采用的电路方案为“单端反激拓扑结构+磁隔离反馈”,设计方案框图如图1 所示。

图1 设计方案框图

2.2 工作原理

如图1 所示,输入的直流电压经输入滤波,由辅助电源提供脉冲宽度调制(Pulse Width Modulator,PWM)脉宽调制器的工作电压。PWM 脉宽调制器产生驱动脉冲信号,驱动功率MOS 管,将输入直流电压变为高频功率脉冲,该脉冲经过变压器隔离传输到次级侧,然后经整流、滤波电路后得到所需要的直流电压。该直流电压经取样比较电路、误差放大电路和磁隔离反馈电路将控制信号传送到PWM 控制器,由该PWM 控制器控制功率变换电路输出的功率脉冲宽度,达到输出电压稳定的目的。

3 电路设计

3.1 主功率电路的设计

3.1.1 变压器的设计

(1)磁芯的选择。根据产品实际设计经验,磁芯的选择需要结合产品的外形尺寸和效率等因素,由于本设计采用的是单端反激拓扑结构,为了防止变压器磁芯饱和,必须选择带气隙的磁芯。经过综合考虑,根据产品的输出功率,利用面积乘积(Area Product,AP)法可以选择东磁公司生产的DMR95 T/RM6B70型磁芯[3]。

(2)变压器的原副边比值k。设电源的工作频率f=350 kHz,取其最大占空比为Dmax=0.6,则电源的工作周期为T=1/f=2.8 μs,Tonmax=1.7 μs,为确保磁芯不会偏离其磁滞回线(上、下方向),变压器导通期间伏秒数乘积必须与复位伏秒数乘积相等。假设开关管与整流管的导通压降都是1 V,则根据公式为

式中:Uinmin为最小输入电压,本设计中为8 V;Uo为输出电压,本设计中为15 V;k为变压器原边与副边的比值。

将已知的值代入式(1)得:k=0.71,取k=0.7。

(3)变压器的原边电感Lp。因为本变换器工作在连续导通模式(Continuous Conduction Mode,CCM),则输出电流很小时,也应有一个临界连续状态,设Io=0.1Io,根据能量关系

又

式中:Lp为原边电感量最小值;Ip为原边峰值电流;Pomin为最小输出功率,本设计中取3 W,即满载输出功率1/10;η1为最小输出功率时电源的效率,取此时效率为0.5。

由式(2)、式(3)得

将已知值代入式(4)得,Lp=5.5 μH。

(4)原边峰值电流Ip1。其计算公式为

式中:Pomax为最大输出功率,本设计为30 W;Ip为原边电感量,其值为5.5 μH;η2为输入最低电压,输出满载功率时电源的效率,取此时效率为0.82。

将已知值代入得Ip1=8.8 A。

(5)初级电流的有效值Irms1。CCM 模式时,原边的磁化电流为

将已知值代入得Irms1=5.9 A。

取导线的电流密度为20 A/mm2,则原边导线截面积为0.295 mm2,考虑导线的集肤效应,本电路选择由线径为0.35 mm 的漆包线并绕而成,易得到单股线径为0.35 mm 的漆包线的面积为0.1 mm2,则初级绕组的根数为0.295/0.1=2.95 根,取整数为3 根。

(6)次级电流的峰值Ip2。副边磁化电流为

则Ip2=5.9 A。

(7)次级电流的有效值。次级电流的有效值Irms2为

将已知值代入式(10)得Irms2=3.2 A。

取导线的电流密度为20 A/mm2,可计算出副边导线截面积为0.16 mm2,考虑导线的集肤效应,本电路选择由线径为0.35 mm 的漆包线并绕而成,易得到单股线径为0.35 mm 的漆包线的面积为0.1 mm2,则初级绕组的根数为0.16/0.1=1.6 根,取整数为2 根。

3.1.2 功率开关管的选择

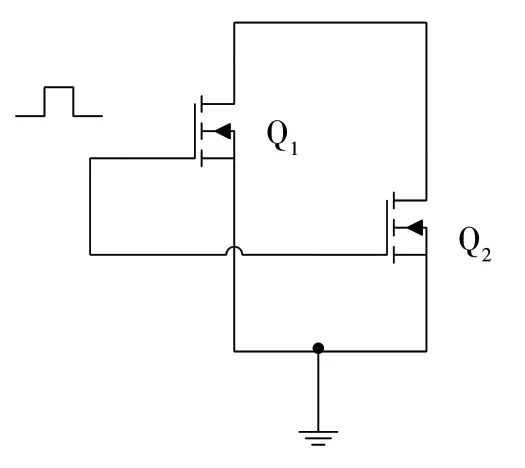

功率变换设计的重要部分是功率开关管的选择。常用的功率开关管一般为N 沟MOS 管,由于本设计的功率较大,当输入电压在8 V 输入时,MOS 管上流过的电流很大,为了减小MOS 管的导通损耗,本设计采用了2 个MOS 管并联的形式。MOS 管连接如图2 所示。

图2 MOS 管连接图

(1)MOS 管承受的电压应力。其计算公式为

式中:Uinmax为电源最大输入电压,取50 V;Uo为电源输出电压,取15 V;k为变压器原边与副边匝比,前面已计算得0.7。

(2)MOS 管承受的电流应力。因为开关管承受的电流应力If是流过变压器原边绕组上的阶梯形斜坡电流等效成的等效平顶初级电流脉冲的幅值[4]。其计算公式为

式中:Pomax为电源最大输出功率,取30 W;η为电源低端输入时的满载效率,取0.82;Uinmin为电源最小输入电压,取8 V;δmax为电源的最大占空比,取0.6。

将上述已知值代入式(11)、式(12)得到,Ur≥80 V,If=7.6 A,考虑降额设计,最终本项目选择2 个150 V/20 A 的功率MOS 管并联。

3.1.3 整流滤波电路设计

由于反激电路的变压器相当于输出电感的作用,输出整流滤波电路不需输出电感与续流二极管,如图3 所示。但是由于本设计输出电流较大,为了降低整流管的导通压降,本设计采用了2 个肖特基管并联使用的模式。

图3 输出整流滤波电路

(1)整流管承受的电压应力。整流器应能承受的最大反向电压Ur的计算公式为

式中:Uinmax为电源最大输入电压,取50 V;Uo为电源输出电压,取15 V;k为变压器原边与副边匝比,前面已计算得0.7。

(2)整流管承受的电流应力。因为整流管承受的电流应力Ir是流过变压器副边绕组上的阶梯斜坡电流,等效成的同脉宽的平顶次级电流脉冲的幅值,其计算公式为

式中:IOmax为电源最大输出电流,取2 A;δmax为电源的最大占空比,取0.6。

将上述已知值代入式(13)和式(14),计算得到Ur=110 V,Ir=5 A,考虑降额设计,最终本项目选择150 V/10 A 的肖特基二极管作为整流管。

(3)输出滤波电容的选择。输出滤波所需的最小电容计算公式为

式中:Iomax为电源最大输出电流,取2 A;δmin为电源的最大占空比,取0.1;Urip为期望输出电压纹波峰峰值,取50 mV;fS为开关频率,取350 kHz。

将已知值代入式(15),得到Comin=91μF,最终经过模拟试验调试确定,输出电容的值取3 个47μF/25 V 的电容并联。

3.2 控制电路的设计

3.2.1 PWM 控制芯片的选择

本设计采用PWM 控制方式,如果选择常用的控制芯片作为主控芯片,最低启动电压一般在8 V 左右,当电源的输入电压低至8 V 时,如果考虑线压降,这些控制片可能无法正常启动。经过综合考虑,本设计最终选择了TI 公司的UCCX803 作为主控制芯片,具有如下特点:

(1)启动电压低,供电电压只要超过4.1 V,芯片就能正常启动工作;

(2)启动电流和静态工作电流小,启动电流只有0.1 mA,静态工作电流只有0.5 mA;

(3)输出采用图腾柱结构,可以提供1 A 的驱动能力。

这些特点完全可以满足8 ~50 V 输入的DC/DC变换器的设计需求。

3.2.2 反馈控制电路的设计

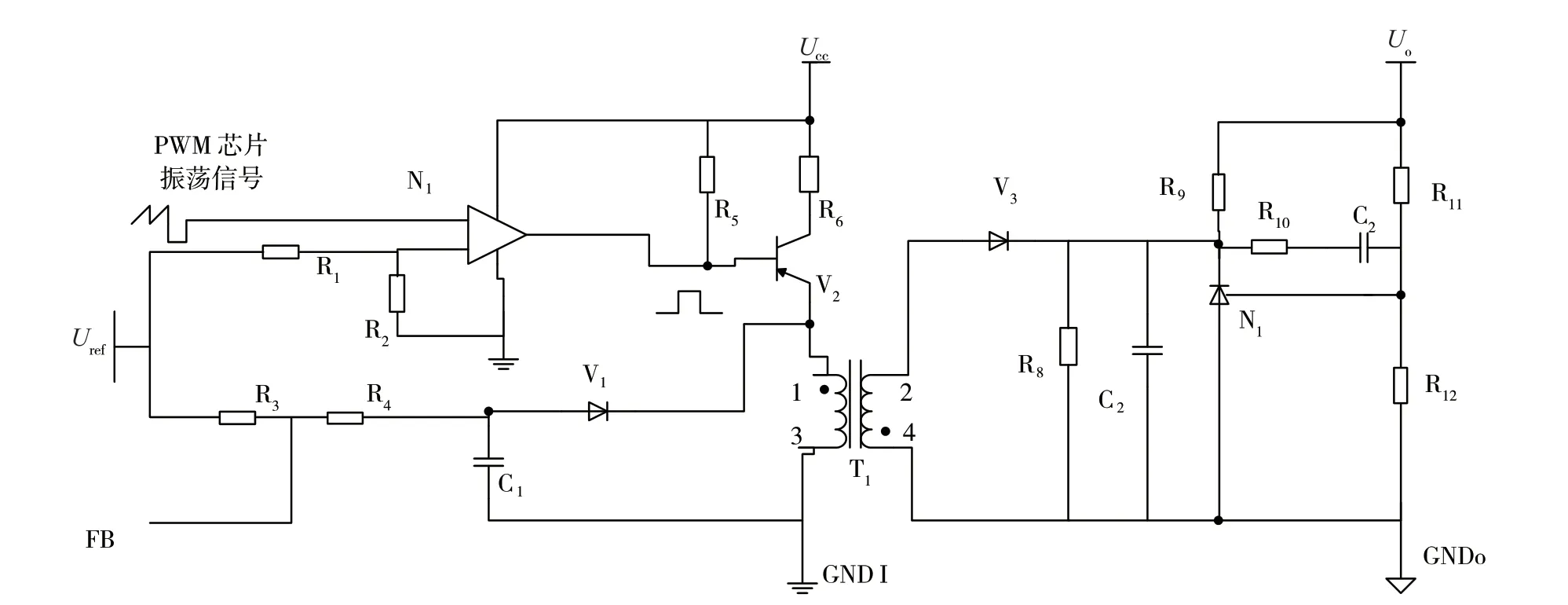

磁隔离反馈电路相较于传统光耦反馈电路,具有更高的可靠性[5]。由于本设计是针对高可靠供电系统设计的,对可靠性要求很高,采用磁隔离反馈的形式,具体电路如4 所示。

如图4 所示,在隔离变压器的T1的初级侧,利用PWM 控制芯片的振荡锯齿波与基准电压通过比较器N1比较得到一个方波控制信号,通过该方波信号控制由R5、R6、V2构成的电流源,同时利用该电流源给隔离变压器T1进行逐周期充电。这样在隔离变压器的初级也能得到一个频率与PWM 振荡信号相同的方波信号,该方波信号被感应到隔离变压器的次级,作为载波信号,电源的输出电压经过电阻R11和R12取样,然后与N1内部基准比较放大以后得到一个误差信号。该误差信号利用前面载波信号进行幅度调制后,形成一个脉冲信号,该信号被隔离变压器传送到初级,经过二极管V1和C1构成的解调电路变换为直流信号,该直流信号经过R3和R4构成的直流偏置电路后,连接到PWM 反馈端,使环路受控。

图4 磁隔离反馈回路

4 测试结果与关键波形

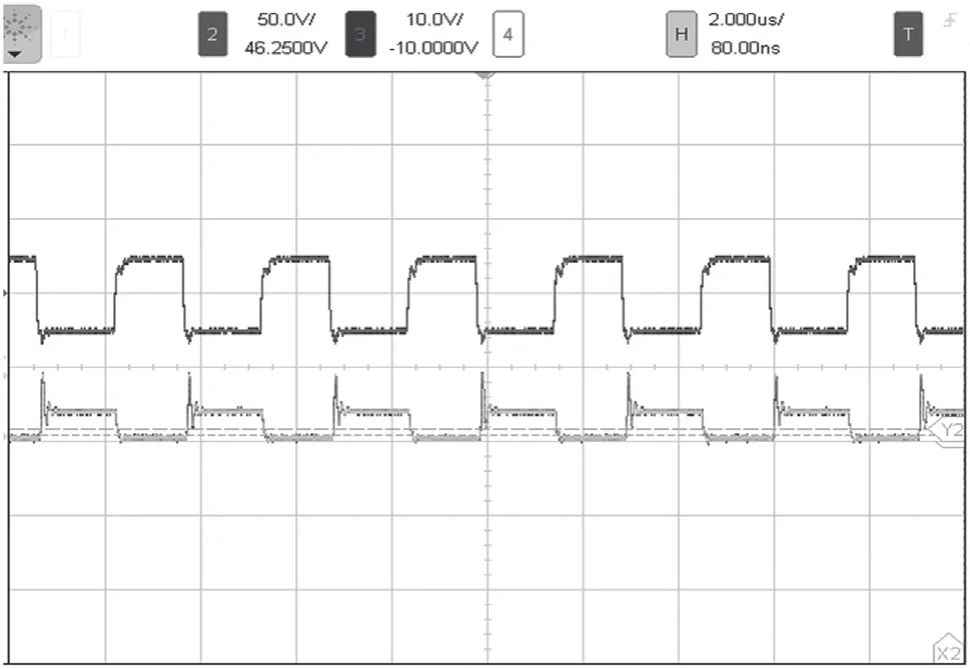

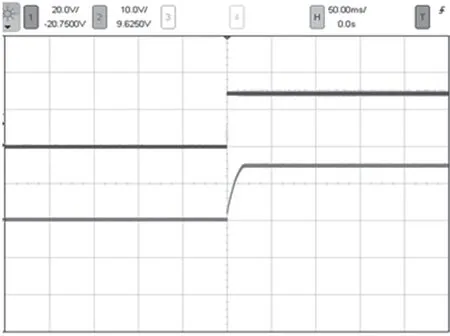

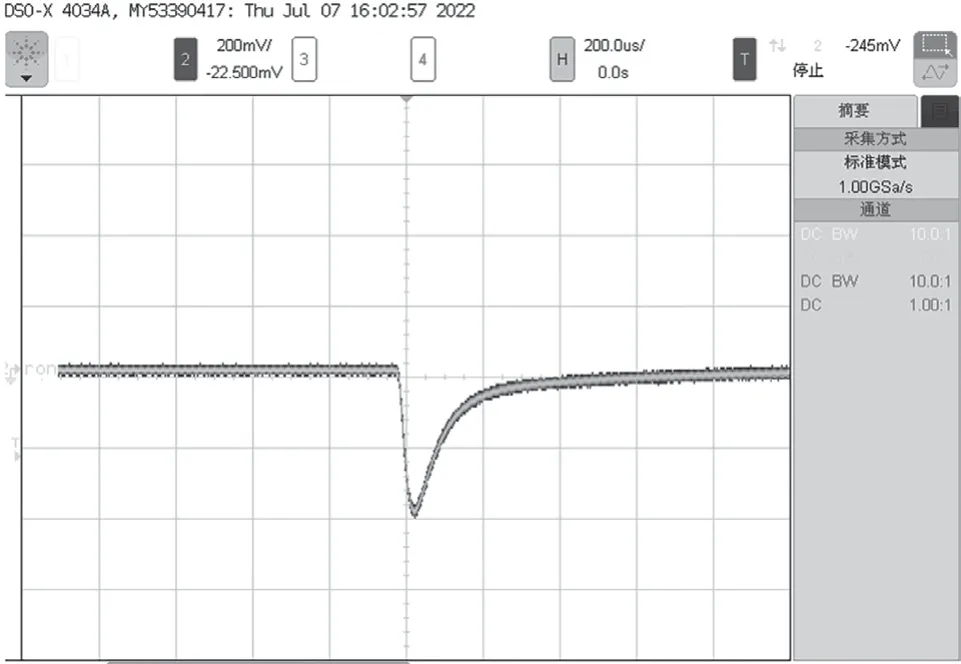

表2 给出了本设计实测指标与设计目标的对比结果,以及产品各关键点波形如图5、图6、图7、图8、图9、图10 所示,从测试结果可以看出,本设计实测指标良好,可以满足设计目标的要求。

表2 实测指标与设计目标比较

图5 Uin=8 V 时的驱动波形与MOS 漏极波形

图6 Uin=28 V 时的驱动波形与MOS 漏极波形

图7 Uin=50 V 时的驱动波形与MOS 漏极波形

图8 输出电压启动波形

图9 输出负载瞬变波形(半载→满载)

图10 输出负载瞬变波形(满载→半载)

5 结 论

文章介绍了一种8 ~50 V 输入的宽范围DC/DC变换器的设计,并对其电路方案和设计过程进行了详细阐述,给出了测试结果和相关波形,测试结果达到预期设计目标。