一种10~20GHz宽带二倍频放大芯片设计

傅 琦,高 显

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引 言

目前低频频谱资源紧张,因此射频器件逐渐向高频方向发展,从Ka 波段到W 波段的高频电路以及跨倍频程的超宽带电路,受到越来越多的关注。在电路设计中,通常需要将低频信号与本振信号混频产生高频信号,因此需要更高频和更宽带宽的本振源。倍频器作为本振链路的关键元器件,其性能指标直接影响本振源的高频特性和宽带特性[1-3]。由于倍频器存在较强的非线性,输出频谱分量较多,通常需要在输出级增加滤波器以抑制杂波,极大遏制了倍频器的宽带特性和高频特性。因此,高杂波抑制的倍频器成为本振链路研究关键。

根据是否需要外加栅压,倍频器可分为有源倍频器和无源倍频器。有源倍频器通过在三极管栅极增加合适的偏置,使信号通过非线性器件产生需要的倍频分量,再通过巴伦、滤波等方式滤除杂波。有源倍频器包括基于高电子迁移率晶体管(High Electron Mobility Transistor,HEMT)工艺[4,5]和基于异质结双极晶体管(Heterojunction Bipolar Transistor,HBT)工艺[6]。无源倍频器多采用肖特基二极管,通常需要输入较大信号以调制肖特基二极管,再通过巴伦、滤波等方式滤除杂波[7,8]。两者相比,无源倍频抑制效果更好,但输入功率较大。

本振链路中的放大器和二倍频器后面通常级联滤波器,用来抑制基波和三次谐波。文章分析了放大器和倍频器级联后抑制杂波恶化的原因,并基于差分电路提出了一种新的拓扑结构,可有效抑制基波和三次谐波。基于此理论,设计了一款不含滤波器、输入频率覆盖10 ~20 GHz 的砷化镓二倍频放大芯片。当输入功率为0 dBm 时,其基波抑制和三次谐波抑制均优于35 dBc。

1 原理分析

无源二倍频器芯片的工作原理:信号通过巴伦产生的差分信号,馈入反接的2 个二极管,倍频后的信号通过输出巴伦进行信号合成。对于宽带倍频器而言,该电路拓扑可以有效抑制输入信号的奇次谐波,且基波和三次谐波抑制度大于30 dBc[9]。

输入信号可以通过肖特基二极管阳极阴极的寄生电容和衬底耦合,直接耦合至倍频器输出端,使基波抑制恶化。在本振链路中,放大器工作处于饱和状态,输出频谱包含多个频率分量,其中功率较大的,除了基波,还有二次谐波。放大器的基波和二次谐波进入倍频器后(双音输入),在非线性器件作用下进行混频。混频产生的基波与三次谐波功率较大,远大于二倍频器在单音输入下的基波与三次谐波功率,导致链路整体的谐波抑制进一步恶化。文章对二倍频器输入级联放大器前后的基波与三次谐波抑制进行仿真,仿真如图1 所示,发现放大器与倍频器级联后基波和三次谐波抑制均恶化。对于二倍频器芯片,与输出频率相近的是基波与三次谐波,因此着重分析链路对基波与三次谐波的抑制。

图1 级联放大器前后二倍频器基波、三次谐波抑制

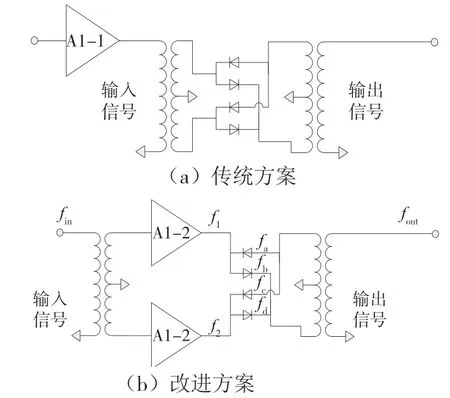

本振倍频放大电路如图2 所示,通过在输出级级联带通滤波器抑制基波和三次谐波。对于跨倍频程的二倍频放大电路,其基波和三次谐波频率产生交叠,无法通过滤波器优化指标。文中引入差分电路设计思想,通过优化设计,将倍频放大电路传统方案调整至改进方案。

图2 本振倍频放大电路

其基波和三次谐波抑制优化原理如下文所述。

在图2 改进方案中,假设输入信号fin=Acosωt,初始相位为0°,巴伦为理想巴伦,即幅度相等、相位相反,通过放大器A1-2 后的两路信号分别为

由于放大器的三次谐波功率较小,因此仅对基波和二次谐波进行分析。f1和f2分别输入两组反接的二极管后有fa=-fb,fc=-fd。

以信号通过其中2 个二极管产生的非线性为例,通过泰勒级数展开后表示为

式中:A、B、C、D、E、F、G、M1,M2均为系数;Z为直流;Bcos2ωt为基波产物;Dcos4ωt为二次谐波产物;Ecosωt为差频;Gcos3ωt为和频。

由式(3)和式(4)可知,通过方案改进,在倍频器输出端,奇次谐波相消,偶此谐波相长,可以有效抑制基波和三次谐波。该方案无须依靠滤波器,通过相位对消,即可最大化发挥倍频器性能。

2 电路设计与仿真

针对章节1 描述的倍频放大电路进行芯片设计。先针对输入和输出频率设计2 款180°巴伦,采用频率响应较好的Marchand 巴伦。该结构广泛应用于单块微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)设计,有较好的宽带特性,且能够通过片上绕线有效缩减面积。通过优化,在10 ~20 GHz 的宽带,巴伦幅度平衡度全频带优于0.5 dB,相位平衡度全频带优于2°;在20 ~40 GHz 的宽带,巴伦幅度平衡度全频带优于0.8 dB,相位平衡度全频带优于5°。

放大器采用2 级放大管结构,信号通过第一级放大后推动第二级,放大器设计中通过在栅漏之间增加负反馈,提高放大器稳定性。通过优化仿真,放大器增益15 dB,输入输出电压驻波比优于1.2,二次谐波抑制20 dBc,静态电流20 mA,输出1 dB 压缩功率大于11 dBm。

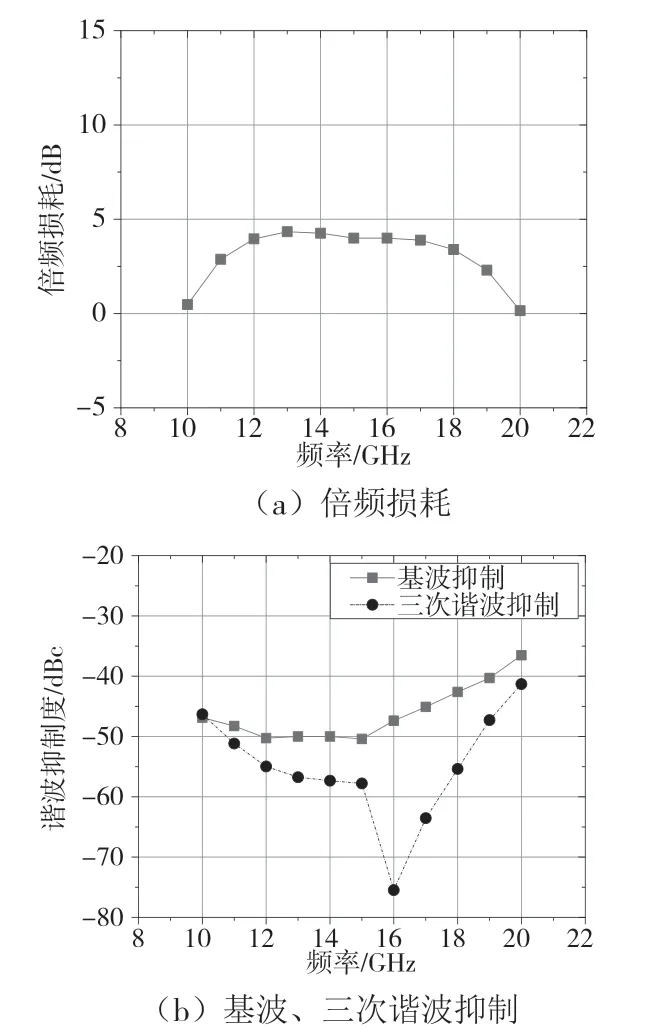

利用电磁仿真软件对电路进行建模仿真,得到倍频放大电路的倍频损耗、基波抑制和三次谐波抑制仿真结果,如图3 所示。

图3 仿真曲线

由图3 的仿真结果可知,二倍频放大电路性能优异,由于存在放大器增益,倍频损耗大于0 dB,三次谐波抑制优于40 dBc,基波抑制优于35 dBc。

3 测试结果与分析

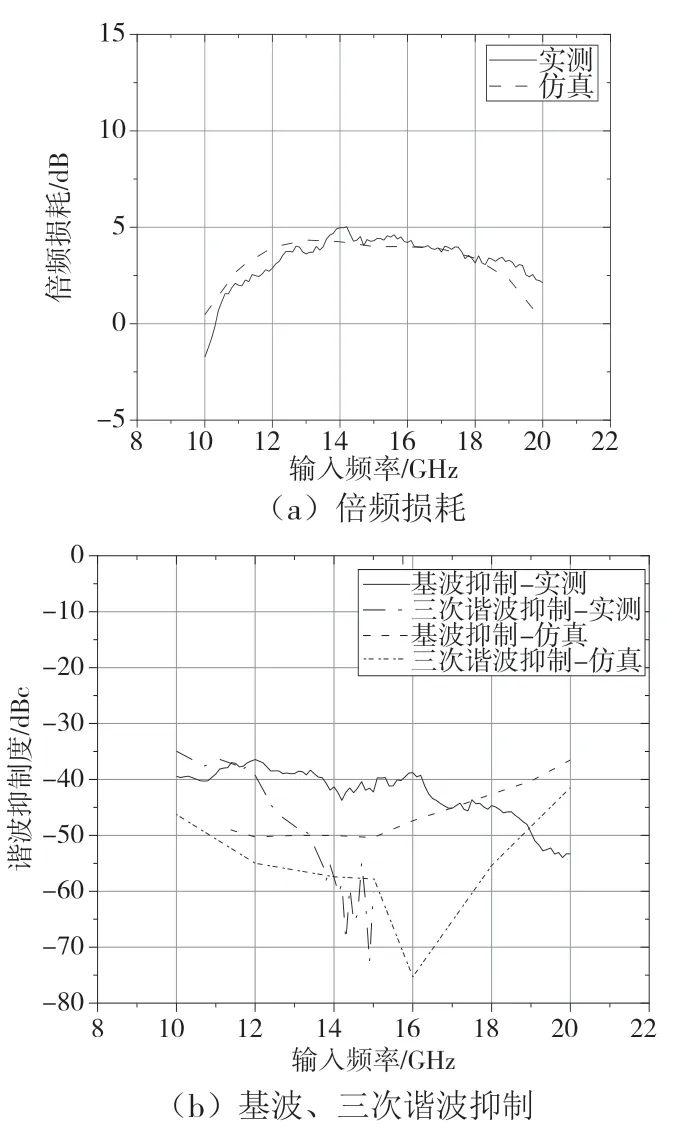

采用砷化镓HEMT 工艺对二倍频放大芯片进行流片。流片使用了经数次参数修正后的改进型外延层材料。完成流片后,通过探针台对倍频放大芯片进行在片测试,电路测试结果与仿真结果对比如图4 所示。

图4 实测仿真曲线对比

由于测试条件受限,探针台矢网高频未能覆盖整个三次谐波频段,因此三次谐波抑制未能完全验证。从测试结果可以看出,倍频损耗在10.5 ~20.0 GHz大于0 dB,三次谐波抑制(部分)优于38 dBc,基波抑制优于37 dBc。谐波抑制度曲线趋势有差异,数量级一致,可以预测电路三次谐波抑制的的最终性能。其中,基波抑制实测与仿真在高频内差异较大,通过分析,主要有2 个方面原因。一方面,在仿真过程中,20 GHz 信号耦合至输出端仿真存在偏差,造成基波抑制在该频点恶化;另一方面,倍频损耗出现频偏。该现象是由于小尺寸肖特基二极管寄生电容不准确,导致仿真实测结果存在偏差,后期将从二极管模型提取入手,优化电路指标。

4 结 论

文章基于差分电路,提出了一种新的二倍频放大拓扑结构,在二倍频放大电路设计中,可以有效抑制基波和三次谐波。基于该方案设计的砷化镓芯片,基波和三次谐波抑制指标能够满足组件中对该类产品的要求。该设计丰富了倍频放大电路的设计思路,并为更高谐波抑制的倍频放大电路奠定基础。