利用FPGA实现轴承三维力采集的高速采集卡设计

张亚平 高聪颖

摘要:轴承的受力检测应用场合广泛,这里采用一种便携式采集卡的方式实现轴承三维力的检测、信号处理、模数转换和上传。信号采集采用应变测量的方式,信号处理采用放大隔离和AD转换的方式,然后通过FPGA实现分时分段采集,可实现多路力信号采集和处理。应变片通过一个特殊设计的支撑体组装成一个三维力传感器,经模拟量信号处理后,通过AD转换传输给FPGA,再经过FPGA的逻辑处理和USB的通讯协议处理,经过USB上传至电脑。

关键词:FPGA;轴承三维力检测;轴承寿命预测;数据采集卡

一、前言

轴承的受力测量应用场合十分广泛,轴承检测相关的应用场合大部分都需要进行受力检测,例如在轴承的寿命预测中,所承受的力与寿命有直接的关联,是必须测量的检测项。在轴承检测仪器中,需要检测轴承预紧力或作用力的场合均需要进行轴承力的测量。轴承是一个高精密部件,转动速度越高,要求的受力检测响应速度越快,为提高实时性,本设计采用FPGA作为外设采集信号,并作为核心处理芯片,为AD转换提供时钟和控制,同时实现数据通过USB接口上传控制。

二、高速采集卡各分模块设计

(一)三维力传感器采集模块

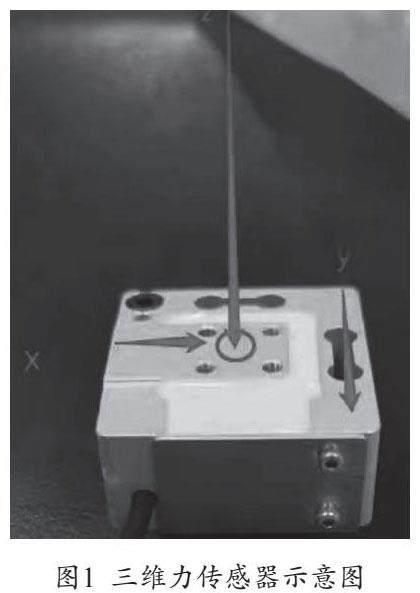

三维力传感器可以检测X、Y、Z三个方向的力,如图1所示,每一方向的力之间相互独立,每个方向都是一个应变桥,通过应变反应检测力的大小。X、Y、Z三路中的每一路的信号处理原理图都一样,以X方向的这一路信号处理为例进行介绍。

传感器可采集到X轴正负两个方向的信号很微弱,输出电压为-5mV~+5mV。该信号需要经过两级放大电路放大至-12V~+12V,首先经过一个低功耗高精度仪表放大器,通过调整R1的大小来调节该级放大器的放大倍数。第一级放大的输入是差分形式输入[1],S1N信号必须和三维传感器输出的COM端相连接,因为这个COM端并不是真正意义的地而是力传感器的电平参考点。

在第一级放大器之后是第二级放大器,第二级放大器采用4路差分放大器LM324,这里采用单端输入,因为第一级放大器已经将传感器的参考电平转换为整个电路的参考点了,也就是AGND,这里采用一个调零机构,对温漂和零漂进行调整,调零机构采用R3、R4电阻和可调电阻R5串联进行分压调整。

(二)隔离放大模块

为提高测量的准确性,防止后续电路对测量端电路的干扰[2],这里增加一个隔离放大电路,如图2。隔离放大电路是采用精密隔离放大器ISO124芯片。该芯片采用了一种新的占空比调制解调技术,通过2-pF差动电容栅进行数字传输[3]。通过数字调制,势垒特性不会影响信号完整性,因此在势垒上具有出色的可靠性和良好的高频瞬态抗扰性,隔离性能良好[4]。隔离电路的输入端连接力信号处理模块的输出端,用于将前面放大处理后的模拟量进行隔离,防止干扰[5]。

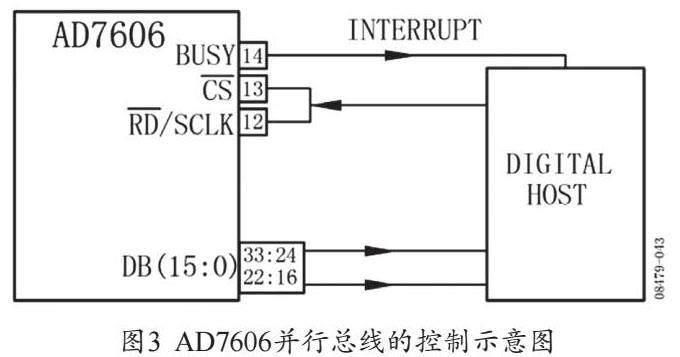

(三)模拟量转数字量模块

AD转换采用8路双极性输入同步采样的A/D转换芯片AD7606进行转换,转换速率达到200kbps。采用并行总线模式提高传输速率,这里需要将PAR/SER/BYTE SEL引脚与低电平连接,通过内部选通CS和RD信号,可以将转换结果输出到数据总线。如图3所示。

CS是片选信号,用于使能芯片,上升沿用于使能总线,下降沿去使能,利用该片选信号可以多个AD7606芯片共用一个并行数据总线,非常适合于本应用。RD引脚用来读取并行数据总线上的数据,当对该RD施加一个脉冲序列,各通道的转换结果通过升序方式输出到数据输出端。当每一次AD转换结束之后,BUSY变为低电平后,RD下降沿输出一个通道结果,第一个下降沿对应第一个结果,以此类推,得到1~8个数据结果。

(四)主控芯片FPGA

主控芯片采用FPGA,其优点是接口丰富,并行速度快,抗干扰能力强,采用FPGA实现对AD7606的时序控制。

当AD7606转换完成后,FPGA读取,通过设定RD引脚控制。

(五)USB上传模块

USB芯片采用CYPRESS的USB3.0的外设控制器CYUSB3014(以下简称FX3),FX3 兼容USB 3.0和USB 2.0物理层(PHY)以及32位ARM926EJ-S微处理器,可以解决USB2.0带宽限制,该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,仅需要下载FX3的固件库,通过配置并行通用可编程接口GPIF II,就可以与控制器FPGA进行连接通讯。

固件设置4个32位并行缓冲区,可以以此来实现338MB/s通信传输。

1.配置FX3的GPIF口

CYUSB3014芯片与FPGA连接还是和usb2.0的一样,使用的是GPIF接口,只需要把CYUSB3014当成FIFO来使用即可,本配置采用slave FIFO模式。其中,FLAGA、FLAGB、FLAGC、FLAGD设置成低电平有效的专用标志,初始值可以随意设置。如图4为配置图。

设置完成后,需要编译并生成所需的头文件,替换固件相应的.h文件即可。

2.各线程的标志位水印值设置

FIFO的大小是16k,P2U的缓冲区设置为8个,U2P缓冲区设置为4个,这种配置可以最大提高传输速度。

FLAGA和FLAGB配置为线程0专用标志,FLAGB为带水印值标志。数据写满时,FLAGA变为低电平,这其中有延迟,将导致FPGA检测到FLAGA为低电平时,数据已经写溢出了,这里FLAGB的水印值可以使标志在数据未满前就变为低电平,FPGA通过检测FLAGB电平,避免数据写溢出。因为SLWR信号是要根据FLAG来驱动的,假如没有水印值标志,使用FLAGA,检测到FLAGA=0时,再将SLWR拉高,就会发生写溢出。需要将FLAGAFLAGA需要提前4个周期拉低,相应水印值为4。

FLAGC和FLAGD配置为线程3的专用标志,其中,FLAGD采用有水印值标志,当数据读空时,FLAGC会变为低电平,但是有延迟,这将导致FPGA检测到FLAGC为低电平时,数据已经读空,通过设置FLAGD的水印值可以使标志提前变为低电平,FPGA通过检测FLAGD电平,避免数据读空的情况发生。和写操作类似,SLRD信号是要根据FLAG来驱动的,假如没有水印值标志,使用FLAGC,检测到FLAGC=0时,再将SLRD拉高,就会发生读空。需要将FLAGC提前3个周期拉低就可以满足要求。所以设置水印值为3。

另外FIFOADDR有3个周期延迟。这些设置好之后,通过USB引导下载固件,即完成了固件配置。

3.上位机通过USB向FPGA下发指令

Streamout是电脑端发送批量数据到FX3,并通过指示位告知FPGA有数据待读取,随后通过SlaveFIFO接口读取电脑端发送过来的数据并缓存到内部的FIFO中。然后FX3读写状态机的状态迁移。FXS_REST为上电状态,随后就进入FXS_IDLE状态,再次判断是否有可读取数据存在SlaveFIFO中,若有则进入“读取状态”读出SlaveFIFO中所有的数据,接着停留一个时钟周期进入FXS_RSOP状态,最后回到FXS_IDLE状态,随后重复以上状态。

程序采用hsc主程序,usb_controller子模块,PLL子模块。usb_controller模块是控制读取模块,该模块会检测FX3的SlaveFIFO看是否有数据可以读取,并读取这些数据,随后写到FPGA片内RAM中。FX3读写状态机一旦检测到SlaveFIFO有可读取的数据,就进入数据读取状态,读取SlaveFIFO中所有的数据,并缓存到RAM中。

4.FPGA通过USB向上位机上传数据

该部分程序与上一部分的一致部分就不再描述,不同的是上传机制,也就是usb_controller。该模块生成FX3的从机FIFO读写操作序列,并检测FX3的从机FIFO是否为空。上电状态FXS_REST,后跟FXS_空闲状态,确定SlaveFIFO是否为空,可以写入数据,如果是,则进入FXS_令状状态将数据写入FX3的SlaveFIFO,然后进入WSOP状态保持一个时钟周期,最后返回到FXS_IDLE状态,如此重复进行。

三、结语

三维应变传感器每个方向采用一组应变片进行检测[6],是完全设置在轴承体外的传感器,本文专注于把轴承的受力进行模拟量处理和上传的研究。需要提及的是,应变片也可以装在轴承内部或直接贴在轴承上,用于测量轴承受力,这里可以应用于智能轴承项目中,把模拟量采集后的结果通过蓝牙传输给FPGA,就可以实现无线检测。

这里涉及的应变片的信号处理、核心处理芯片的FPGA程序架构和设计可以完全应用于智能轴承,希望能给智能轴承应用提供一定的参考和支持。

参考文献

[1]唐正强,惠佳博,周东东,等.磁力耦合器空气散热结构设计与分析[J].组合机床与自动化加工技术,2020(3):136-139+143.

[2]孙中圣,周丽萍,王向东,等.筒式永磁调速器的磁场分析与特性研究[J].中国机械工程,2015,26(13):1742-1747.

[3]陈丽香,王正祥.多磁路结构永磁电机气隙磁密波形优化[J].组合机床与自动化加工技术,2014(6):38-41+50.

[4]刘瑞芳.电磁场计算中永磁体励磁等效处理方法的研究[J].北京交通大学学报,2008(5):94-97+106.

[5]田录林,贾嵘,杨国清,等.永磁铁磁贴合体的磁场及磁力[J].电工技术学报,2008(6):7-13.

[6]王黎钦,陈观慈,古乐,等.高速圆柱滚子轴承工作温度研究[J].航空动力学报,2008(1):179-183.

作者单位:张亚平,信阳职业技术学院;高聪颖,洛阳轴承研究所有限公司