AVS 浅压缩模式决策硬件设计与实现

黄贺焜,吴林煌,蔡江震

(福州大学 先进制造学院,福建 泉州 362200)

0 引言

为解决国际音视频编解码标准垄断问题,我国建立了自己的标准制定团队——数字音频视频编解码技术标准工作组,于2003 年提出了第一代数字音视频编解码技术标准(Audio Video coding Standard,AVS),实现了与H264 标准相当的编码效率。随着对高清、超高清、3D 视频需求的增加,第二代视频编码标准AVS2 被提出。AVS2 标准相比AVS 标准平均减少了45%的码率,在编码速度与效率方面与高效率视频编码(High Efficiency Video Coding,HEVC)、H.265 标准相当[1]。AVS2 采用了与HEVC[2]类似的编码结构,并加入了许多新的编码工具,如内方向预测、短距离帧内预测、非方形四叉数变换、逻辑变换以及双标准系数编码等[3]。为了保证编码压缩率,AVS2 标准采用了9 种分式和33种方向预测[4],以及多种类型的变换编码,实现了高效视频编码,但也有着较大的编码复杂度与计算量。目前,对AVS 编码器的研究在普通平台上已经取得了较好的成果,满足了大部分产业化应用需求。但随着移动多媒体等设备的普及,现如今的AVS 压缩效率和压缩质量已经无法满足低延时、轻量化、浅压缩场景的需求,故需要对AVS 模块如帧内预测[5]、量化与反量化[6]、模式决策[7-8]、熵编码[9]或码率控制[10]中的算法进行改进,通过硬件实现加速,得到更优化的视频编解码性能。

AVS 编码器在我国的广阔前景驱使从业者深入研究AVS、AVS2 及AVS3 编码器的优化与应用,以便其更广地实现产业化。因此,为了实现AVS 编码器的在浅压缩场景下的应用,需要对其编码过程进行优化。2021 年,AVS 视频组织确认了浅压缩需求以及测试方案,于2022 年4 月提出浅压缩参考软件平台HIM。该平台通过低复杂度的预测、量化、模式决策和熵编码方案,实现主观视觉无损的高性能压缩。因此,最新的AVS 浅压缩编码器的算法实现与优化研究具有非常重要的理论价值。

针对上述问题,本文首先分析AVS 浅压缩模式决策算法原理,其次介绍一种适配于硬件的算法实现方案以及系统整体方案设计流程,并对结果进行分析。本文方案在VCS 平台上进行功能仿真验证并上板进行部署,验证了本方案的可行性。

1 AVS 浅压缩编码器架构

AVS 浅压缩可以处理YUV 和RGB 格式的图像和视频,并支持YUV4 ∶0 ∶0、YUV4 ∶2 ∶0、YUV4 ∶2 ∶2、YUV4 ∶4 ∶4 和RGB4 ∶4 ∶4,支持8 bits、10 bits、12 bits 和16 bits 的输入比特深度,并根据不同图像格式产生不同的基本处理单元。图像格式有亮度通道(Y 分量)和色度通道(U、V 分量),在YUV4 ∶0 ∶0、YUV4 ∶2 ∶0、YUV4 ∶2 ∶2、YUV4 ∶4 ∶4 和RGB4 ∶4 ∶4格式下,亮度通道为固定的16×2 像素块,色度通道在YUV4 ∶4 ∶4 和RGB4 ∶4 ∶4 格式下为16×2 像素块,YUV4 ∶2 ∶2 格式下为8×2 像素块,YUV4 ∶2 ∶0 格式下为8×1 像素块。

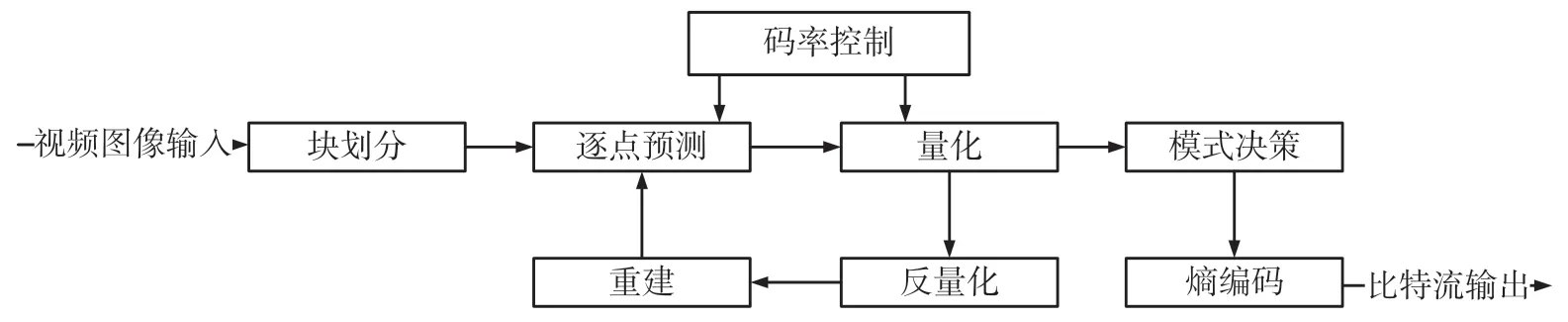

编码层架构如图1 所示。AVS 浅压缩编码器顶层包含块划分、逐点预测、量化、模式决策、熵编码及码率控制等模块,负责各个模块之间的数据传递及模块之间的工作顺序安排。根据外部输入图像的不同格式,首先进行图像格式转换,其中非YUV的图像需要进行颜色空间转换,将其统一到YUV颜色空间中。此时编码器所需的编码信息如比特深度、图像格式及块数量等将通过外部APB接口输入。通过码率控制模块得到量化参数QP,并将量化参数QP 送入预测模块。预测模块通过4 种预测方式得到的残差值需要进行QP 调整,并将调整后的残差送入后级的量化、反量化与重建模块中。将量化后的残差值送入模式决策模块,模式决策模块计算当前使用到的每一种编码块中的各个预测模式下的编码比特数和失真代价,对求和的结果进行比较后得到最优的一种预测模式,将最佳预测模式下的残差等信息传输至后级的熵编码模块进行比特流的传输。

图1 编码层架构

2 AVS 浅压缩模式决策算法设计

在AVS 浅压缩中,模式决策的准则如式(1)所示,通过比特代价和绝对误差和(Sum of Absolute Difference,SAD)值进行求和,得到最优的预测模式为率失真代价最小的模式。

式中:m表示模式(mode),Ψ表示所有模式的集合,λQP表示率失真优化中的拉格朗日因子,R(m)表示不同预测模式下编码当前像素块的比特代价,D(m)表示表示不同预测模式下重建像素块与原始像素块的SAD 值。λQP由码率控制模块生成的量化参数QP 导出,具体描述如下。

首先计算QP 对应的Qstep。再计算码控满度fullness 对应的系数α,计算公式为

最后计算λQP,计算公式为

R(m)为需要传输的语法信息所计算出的比特代价,其中需要传递的语法元素包括逐点预测的模式pred_mode、系数分组rpm、残差编码长度lc 以及边界符号trailing。

2.1 比特代价计算

2.1.1 逐点预测模式

逐点预测共有4 种预测模式,通过在模式决策中进行代价比较,得到4 种预测模式最佳的预测模式,进而输入到后级的熵编码模块中进行编码。pred_mode 的比特代价计算方式是:定义数组pred_mode_code 用于存储不同模式下的初始值,通过判断模式类型进行索引,取值为{3,3,0,0,2,4,4,5,5,5,6,6,0,0,2},{0,1,0,0,3,11,10,19,18,17,33,32,0,0,1}。

2.1.2 残差编码长度和边界符号

在当前最佳预测模式下,首先计算当前通道宏块对应的最佳预测模式的残差值。其次将其分组为大小为4 的子集,计算每组内残差最大值占用的比特数,作为当前4×1 块内残差码长度。最后,检查每组残差值是否位于当前残差码长度能表示的范围边界上,根据具体的取值情况,对边界符号修正符进行相应的设定。残差编码长度lc的比特代价计算方式为

式中:ccl为残差编码长度lc的代价,d是当前图像的比特深度。

边界符号trailing 的比特代价为每个cl 块的trailing 之和。

2.1.3 系数分组

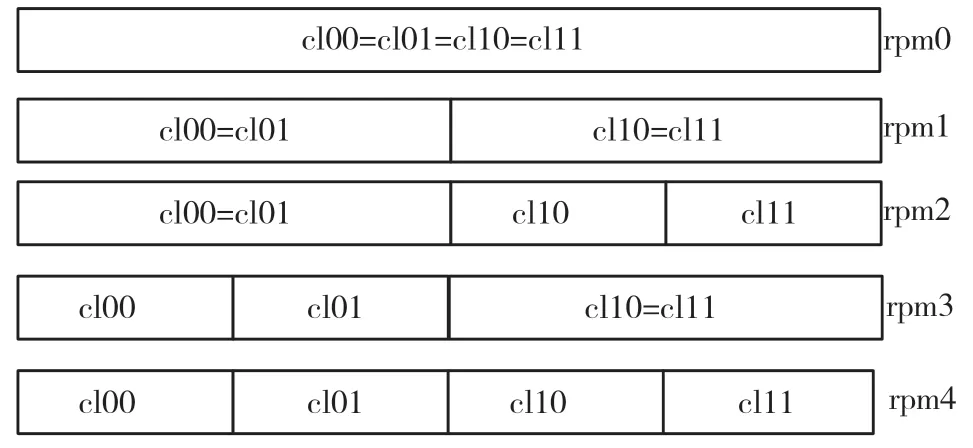

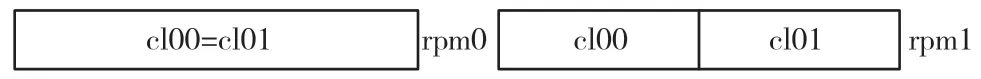

当编码块处于亮度通道,可采用5 种方式进行划分,如图2 所示。

图2 16×2 编码块系数分组方式

根据计算出的残差编码长度lc进行系数分组。每4 个像素为一个cl,标记为cl00、cl01、cl02 和cl03。cl 块两两相比较得出系数分组rpm 的具体方法是:当4 个块的残差编码长度都相等,rpm 为PRM0;当cl00=cl01 且cl02=cl03,rpm 为PRM1;当cl00=cl01 且cl02 ≠cl03,rpm 为PRM2;当cl00 ≠cl01 且cl02=cl03,rpm 为PRM3; 当cl00 ≠cl01 且cl02 ≠cl03,rpm 为PRM4。

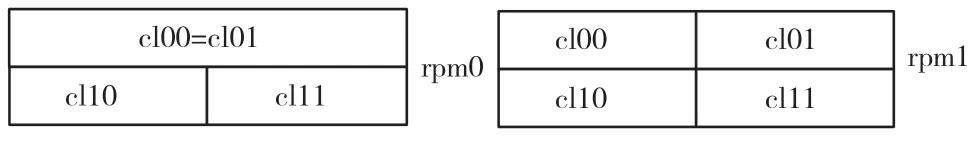

当编码块为色度通道时,需要根据不同的图像格式进行不同的编码块大小判断。若编码块大小为8×2,可采用2 种方式进行划分,如图3 所示。

图3 8×2 编码块系数分组方式

若编码块大小为8×1,可采用2 种方式进行划分,如图4 所示。

图4 8×1 编码块系数分组方式

rpm 的比特代价计算公式为

式中:crpm为系数分组rpm 的比特代价,mrpm表示rpm 分组模式,其中e[j]为两种索引模式的索引,j=0,1。rpm 在亮度模式下有两种模式,需要对两种模式下的rpm 分别计算代价,相加得到最终的crpm。

2.2 SAD 计算

SAD 的计算公式为

式中:porg为每个编码宏块的各点原始像素,prec为该点对应的重构像素。重构像素由模式决策模块上一级的逐点预测模块得到。

3 模式决策硬件方案

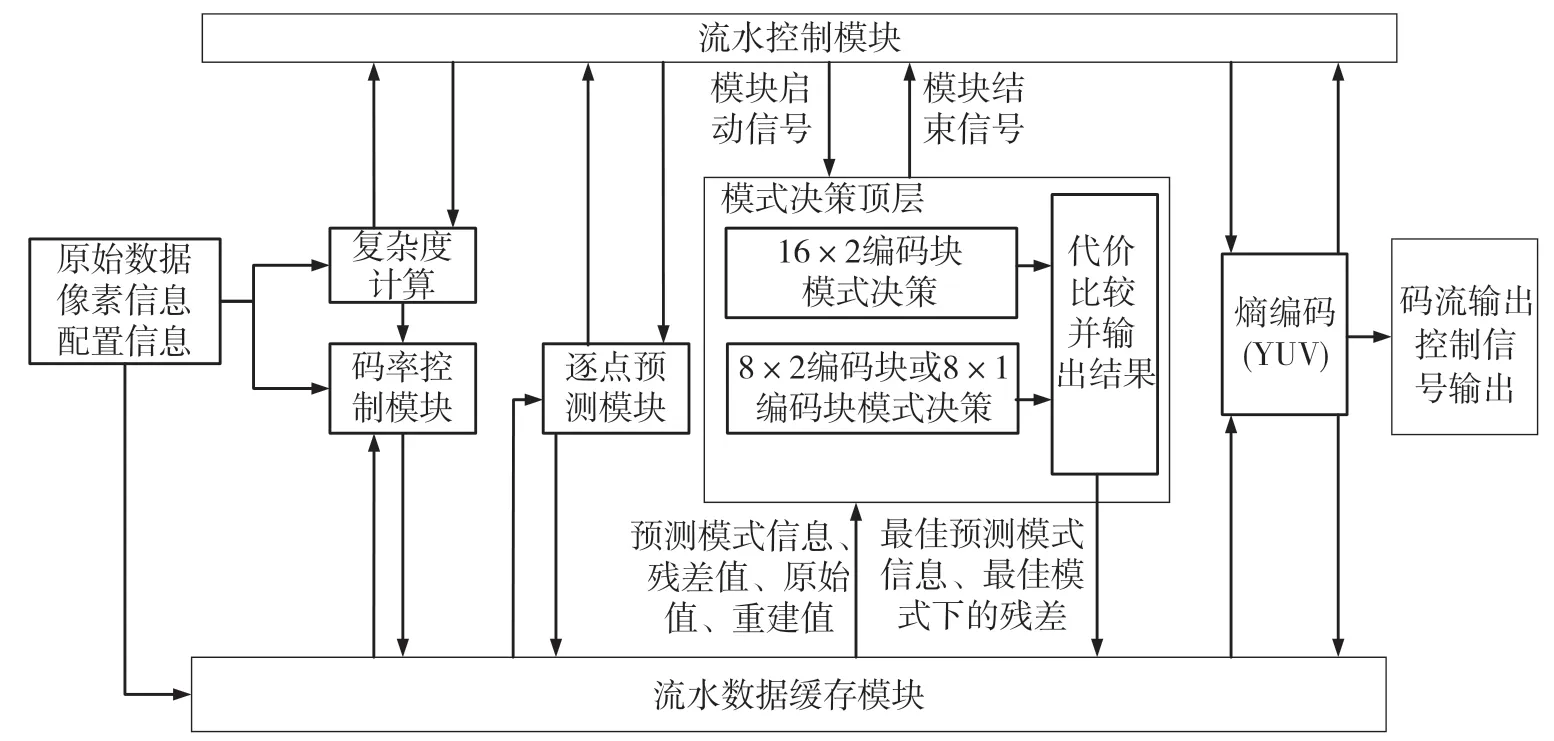

本文根据算法设计一套面向低延时的AVS 浅压缩编码的模式决策硬件方案。其中编码器硬件的顶层架构如图5 所示。为加快编码器运行频率,采用流水架构设计,各模块的启动信号由流水控制模块控制,每隔12 个时钟进行一级模块启动,收集每个模块的结束信号以开启下一级模块,将每个模块得到的结果进行数据缓存。得到上一级逐点预测模块顶层模块输出的预测残差值、重建值、预测模式等信息和模式决策启动信号后,模式决策模块按图像格式所对应的通道进行处理,若图像为YUV444或RGB444,则选择的亮色度通道在16×2 编码块模式决策中进行,否则亮度通道在16×2 编码块模式决策中进行,色度通道则进一步判断,从而准确送入8×2 或8×1 编码块模式决策中分别进行,最终进行比较后得到最佳预测模式下的残差值、rpm、lc 等信息进行数据缓存。

图5 编码器硬件顶层架构

模式决策内部硬件设计如图6 所示。根据模块输入的重建值可得到SAD 代价。根据残差值和预测模式,可得到lc、trailing,并根据lc 得到系数分组rpm,进行编码比特代价计算,最终进行加权求和的总代价值进行比较,得到最佳的预测模式。将该预测模式对应的预测模式信息、残差值、lc、trailing 及rpm 等信息输出。

图6 模式决策硬件顶层

4 模块测试结果分析

本文考虑了工作频率、资源使用等多方面要素,对模式决策模块设计进一步深入分析,以优化路径,提高编码器性能。

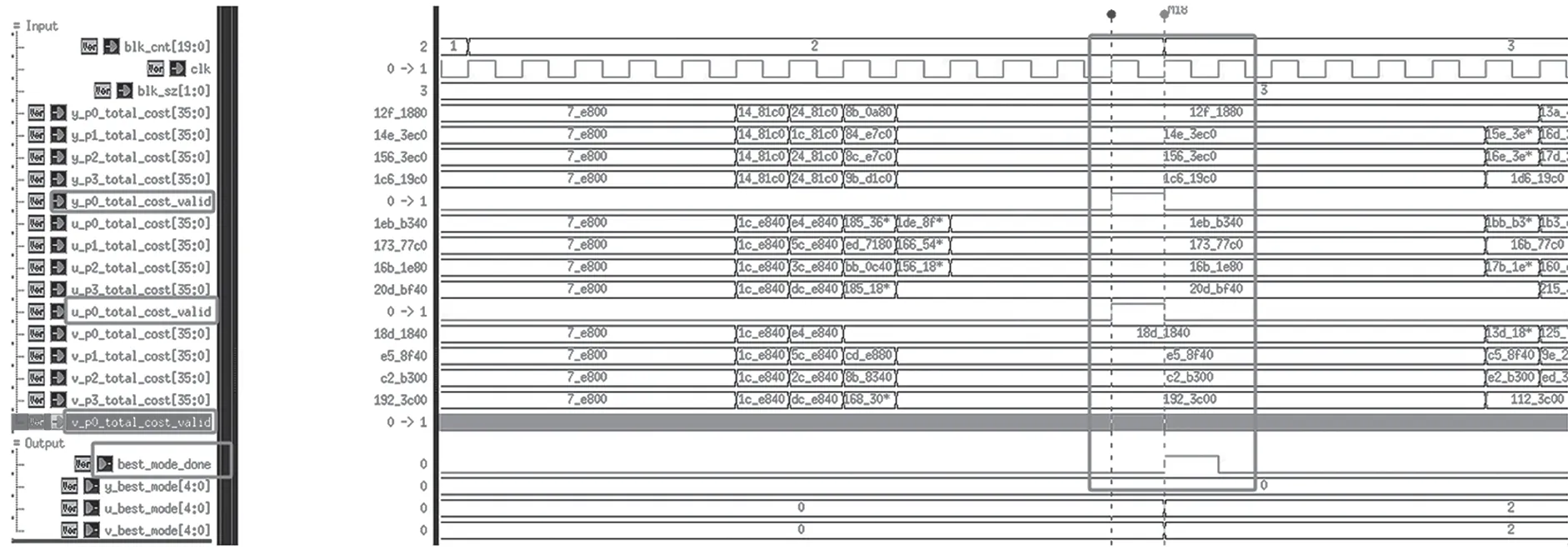

使用VCS 仿真EDA 工具完成仿真波形的数据结果后,利用Verdi 工具查看波形结果,模式决策代价计算波形如图7 所示。本设计仿真采用两幅不同图像格式(YUV444、YUV420),在8 bits 深度下进行测试,在时钟信号的激励下,模块接收到pred_done 信号后,模式决策模块开始工作,在3 个时钟后得到lc、trailing 信息,紧接着得到系数分组rpm信息;在11 个时钟后得到总加权求和后的代价,并输出该时钟下的代价有效信号total_cost_valid。

图7 模式决策模块代价计算端口时序图

得到代价有效信号后,通过比较得到最佳预测模式和该最佳预测模式下所对应的值,并将best_mode_done 信号置1。该过程的时序如图8 所示。总体模块总计花费12 个时钟。

图8 模式决策模块选择端口时序图

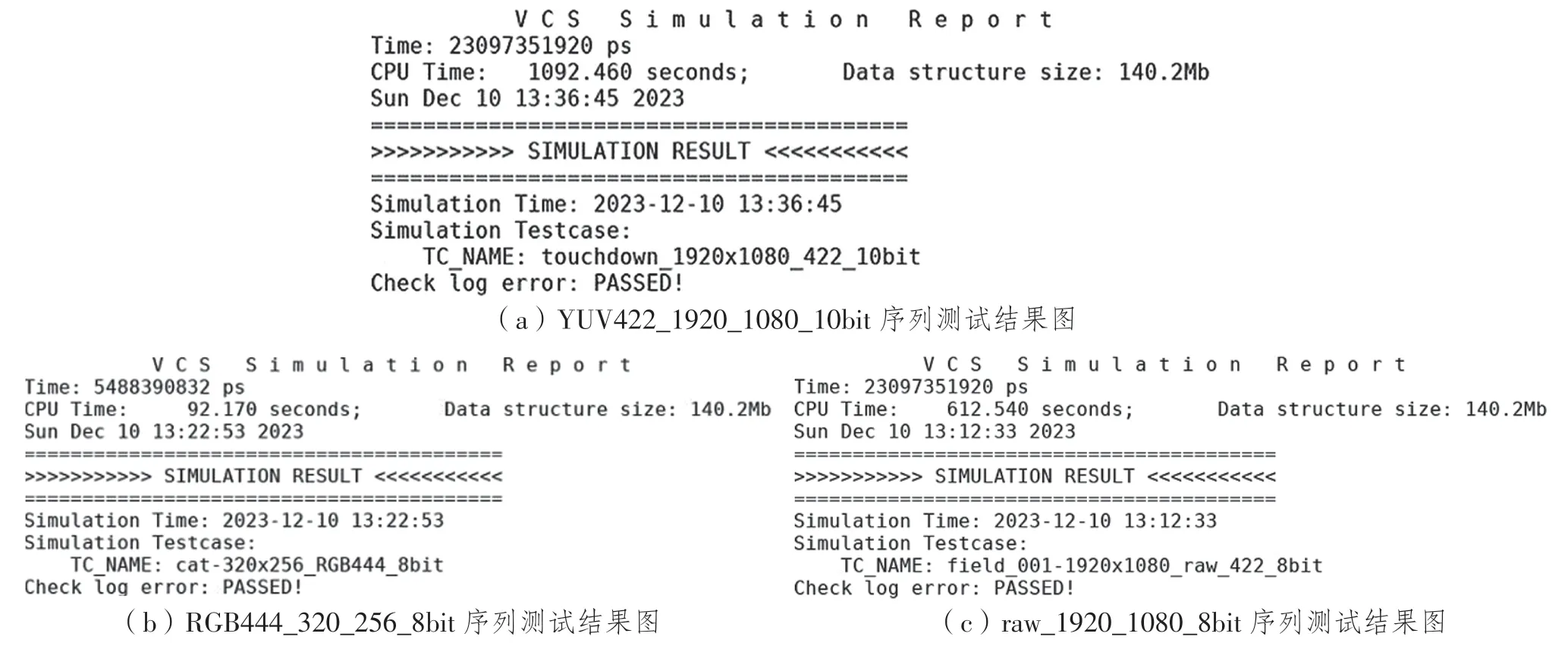

完成各个子模块的仿真验证工作确保各模块输出的时序正确后,将各模块信号端口连接并使用脚本对所设计的硬件整体进行仿真测试。图9 为测试脚本测试不同图像序列的输出结果。3 帧图像的测试结果与算法模型得到的数据完全吻合时,检查结果输出“PASSED”。

图9 各序列模式决策模块测试图

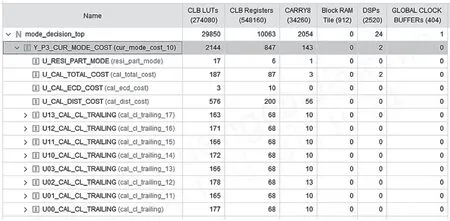

在Vivado 2022.2 软件上编译实现后,得到系统的资源使用评估报告,如图10 所示。其中,Y、U、V 各个分量所消耗的硬件资源与Y 分量下的预测模式3 类似,编码器核心使用了芯片中的大部分逻辑资源。

图10 模式决策顶层硬件资源

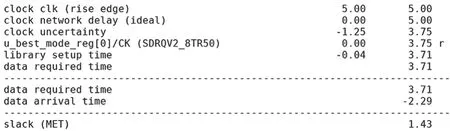

浅压缩编码器需要支持至少1 920×1 080、60 帧率,因此预设200 MHz 时钟频率,在40 nm工艺下用DC 综合工具进行编译后,生成设计模块综合后的时序报告,如图11 所示。最终slack 为1.43,表明时序收敛,主频可满足浅压缩编码器整体的100 MHz 编码时钟需求。且同样工艺节点下,ASIC 芯片所能实现的最高主频通常远高于在现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)上实现的主频。

图11 时序分析

将模式决策模块集成在编码器内部,使用高清摄像头拍摄笔记本电脑上显示的图像,由解码板上的解码器进行硬解码,编解码效果如图12 所示。

图12 编解码效果图

5 结语

本文基于AVS 浅压缩标准,提出针对模式决策算法的硬件实现方案;介绍了AVS 浅压缩整体设计,分析了模式决策模块所采用的算法并设计了其硬件实现方案;最后对实现的硬件进行功能仿真验证、资源和时序评估,通过仿真数据分析验证了所设计的硬件模块经过运算后输出的数据与算法模型输出的数据完全吻合;最后进行编码器的集成,并进行上板测试。结果显示端到端延时为60 ms,主频为150 MHz,大于需求的100 MHz,可满足1 080p@60 的视频浅压缩需求,并与编码器低延时、低资源的标准相适配,达到了设计要求。