一种低噪声硅微条探测器读出电子学系统的设计*

贺跃光 韦家驹 郭建华

(1 中国科学技术大学天文与空间科学学院 合肥 230026)(2 中国科学院紫金山天文台 南京 210023)(3 中国科学院暗物质与空间天文重点实验室 南京 210023)

1 引言

自20世纪80年代以来,随着半导体技术的不断发展,各类半导体探测器的制作工艺也得到了长足的发展,其中针对径迹测量的硅微条探测器凭借时间响应快、位置分辨率好等特点被广泛地应用到高能物理、天体物理和核医学等领域.在空间观测实验如费米γ射线空间望远镜(Fermi Gamma-ray Space Telescope,FGST)[1]和阿尔法磁谱仪(Alpha Magnetic Spectrometer 2,AMS-02)[2]中,为了准确地获知带电粒子的径迹信息,其径迹探测器一般由多层硅微条探测器阵列组成,而每个阵列又由多块硅微条探测器单元构成.

为了精确测量入射到硅微条探测器中带电粒子的信息,需使用低噪声、高精度的电荷测量系统对探测器输出电荷进行测量,另外,由于硅微条探测器单元上有成百上千条微条,一般每隔一条或者数条微条连接一路读出电子学,因此需要前端电子学具有较高的集成度[3].

考虑到硅微条探测器[4–6]的输出信号比较小,工作电磁环境复杂,电子学系统需要提高信噪比抑制噪声;另一方面,基于前端电子学高集成度的要求,国际上许多高能物理实验中,径迹探测系统的前端电子学都采用了低噪声、高精度、多通道的专用集成电路(Application Specific Integrated Circuit,ASIC).例如,FGST上径迹探测器所使用的Glast Tracker Front-end electronics(GTFE)和Glast Tracker Readout Controller electronics(GTRC)芯片[7]、AMS-02上径迹探测器所使用的VA64hdr9a芯片[8]、暗物质粒子探测卫星上(Dark Matter Particle Explorer,DAMPE)硅径迹探测器(Silicon-Tungsten Tracker,STK)所使用的VA140芯片[9]等等.本研究中前端读出电路选择Integrated Detector Electronics AS(IDEAS)公司的128通道的电荷读出专用芯片VATAGP8[10–11],并使用FPGA建立硅微条探测器单元读出电子学的控制系统,实现了对硅微条探测器单元的信号读出.在对电子学系统进行了相关的功能及性能测试后,配合硅微条探测器单元进行了宇宙线缪子的最小电离粒子(Minimum Ionizing Particle,MIP)的响应测试.

2 硅微条探测器单元

本论文中电子学系统所使用的硅微条探测器单元为日本滨松公司生产的单面硅微条1http://www.hamamatsu.com.cn/.(Silicon micro-Strip Detector,SSD),主要由768条P+型微条和N型硅衬底构成.硅微条探测器单元的尺寸为95 mm×95 mm×320 μm,条间距为121 μm,多晶硅电阻约为几十兆欧姆,全耗尽电压约为40 V.这款探测器曾应用于2007年的敏捷号γ射线天文卫星(Gamma-ray Light Detector,AGILE)项目[12]以及2015年DAMPE卫星项目[9]中.

探测器单元正常工作时,外加的反向偏压将会使灵敏区扩大到探测器单元的整个体积.如果有带电粒子穿过探测器单元,探测器单元的灵敏区将会产生电子-空穴对,数量正比于带电粒子损失的能量.在偏压电场的作用下,电子、空穴分别向两极漂移,微条上的电极感应形成的电流脉冲被前端电子学捕获并沿着相应的电子学通道读出.根据有信号的通道号可以准确地反映粒子的位置信息,而电荷大小(电流脉冲积分)可以反映粒子在硅微条探测器单元中沉积的能量信息.

3 读出电子学系统的设计

3.1 电子学系统的需求和考虑

参考DAMPE中径迹探测器STK的前端电子学设计方案[13],要求输入电子学系统的电荷动态范围0–200 fC.为了保证系统在输入范围内有良好的线性指标,要求积分非线性(Integer Non-Linearity,INL)不超过2%.

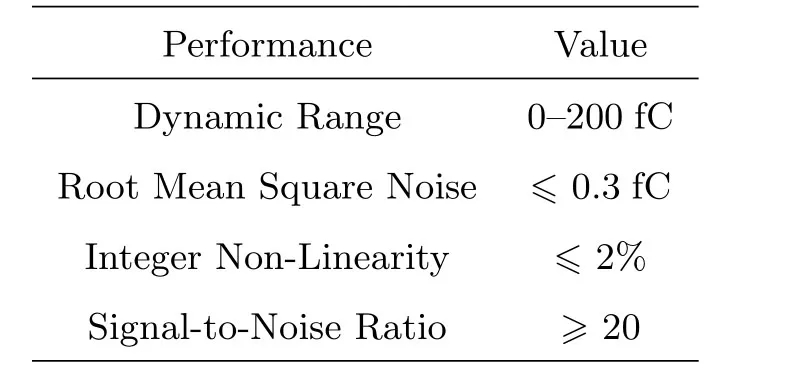

根据物理学模拟的结果,300 μm硅探测器单元中最小电离粒子的峰值电荷为3.5 fC.因此读出电子学噪声不能超过0.3 fC,以便探测器对宇宙线MIP获得良好的能量分辨率[13].根据硅微条探测器仿真的结果,高信噪比(Signal-to-Noise Ratio,SNR)能够改善硅微条探测器的位置分辨能力[14],一般要求读出系统的信噪比大于20.表1总结了读出电子学系统的各项指标.

表1 SSD读出电子学的性能指标Table 1 Performance index for SSD readout electronics

这些设计指标给电子学系统的设计带来较大的挑战.首先,电荷读出芯片的选择需要综合考虑到多个因素,如:动态输入范围、等效噪声电荷、成形时间、增益、功耗等.其次,电子学系统需要精心设计以满足设计指标.一些寄生参数对电子学系统的噪声存在一定的影响,需要电路设计以及布局布板时减小这种影响,比如印刷电路板(Printed Circuit Board,PCB)上的布线或者过孔、PCB之间的线缆、PCB上的接插件都存在一定的寄生电容,增加了通过信号的噪声和延时,降低了信号质量.为此需要合理的设计PCB的层叠结构,挑选合适的连接线缆和接插件.电路中的数字信号对模拟信号也会有一定干扰,影响电子学系统的噪声、线性等性能,需要数字器件和模拟器件合适的布局和隔离来减少这种干扰.

另外,前端电子学板的封装需要特殊设计的封装方法,要求封装好的探测器单元能有效屏蔽光和电场干扰、距离电荷读出芯片的输入端尽可能近、背电极与高压的接触电阻尽可能小.为此专门设计了特殊的前端电子学板来承载探测器单元,并使用超声波引线键合技术连接探测器单元、PCB和电荷读出芯片,最后设计了屏蔽盒对光和电场干扰进行良好的屏蔽.

3.2 总体设计

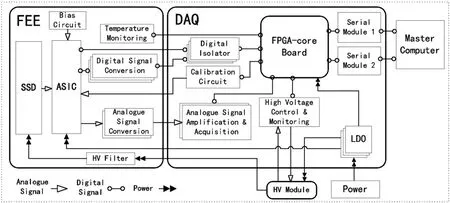

整个电子学系统分为前端电子学(Front-End Electronics,FEE)和数据获取电路以及用于自动化测试的上位机软件.其中,数据获取电路由数据采集板(Data Acquisition Board,DAQ)母板、FPGA核心板(FPGA-core Board)子板、高压模块(High Voltage Module,HV_Module)组成.图1显示了电子学系统设计完成后的硬件实物图,其中,前端电子学被放置于金属屏蔽盒内.

图1 设计完成后的电子学系统硬件构成Fig.1 Hardware composition of electronic system after the design is completed

电子学系统的整体电路结构及其信号流向如图2所示,在FEE上ASIC负责接收硅微条探测器单元输出的电荷信号,放大输出后由模拟信号转换电路将其转换成电压信号送往DAQ,同时FEE还负责温度的监控.FPGA核心板根据上位机发送的指令,在DAQ上控制整个电子学系统实现不同的任务,包括对运放电路输出的模拟信号进行数字化采集、对高压模块的输出高压进行监控以及对指定电子学通道进行线性刻度等等.高压模块的主要功能是产生反偏高压使探测器单元发生全耗尽,并提供监测电压供外部采集监控.上位机提供控制电子学系统工作的交互界面,通过下发指令、解析数据来控制系统的运行状态.整个系统由外部直流电源供电,经过多级线性稳压芯片(Low DropOut linear regulator,LDO)后产生各个模块所需的工作电压.

图2 电子学系统的整体结构Fig.2 Overall structure of electronic system

整个系统设计了3种工作模式:基线模式、线性刻度模式和正常工作模式.基线模式通过FPGA提供的触发信号对VATAGP8的128条输入通道进行多次采集,测试128条通道的噪声和基线水平.线性刻度模式则是通过芯片专用的测试管脚向每条通道注入不同的电荷信号,并使用芯片的自触发信号进行采集,从而得到128条通道输入电荷与采集结果的线性关系.正常工作模式是通过芯片的自触发实现对探测器单元输出信号的采集、存储和传输.在电子学系统工作时将会产生两种数据:电荷信号相关的科学数据以及温度、电压、电流的实时监测数据.这两种数据分别通过不同的串口模块传送至上位机.

3.3 前端电子学设计

前端电子学的主要功能是对硅微条探测器单元输出的电荷信号进行放大,由于探测器单元的输出电荷信号很小,因而要保证通道噪声尽可能低.考虑到硅微条探测器单元的通道数量很多且通道间距很小,一般采用高集成度的专用芯片进行电荷采集.

为了满足电子学系统低噪声、大动态范围的设计要求,前端电子学采用IDEAS公司设计的VATAGP8芯片.VATAGP8是一款电荷读出专用集成电路2https://ideas.no/products/vatagp8/.,用来测量探测器多通道输出的电荷信号,测量电荷动态范围在+/-250 fC之间,满足0–200 fC电荷输入动态范围的设计指标.VATAGP8芯片的等效噪声电荷(Equivalent Noise Charge,ENC)为390 e+5 e/pF,而硅微条探测器单元单根微条的等效电容约为20 pF[4],理想条件下得到的噪声约为490 e,相当于0.078 fC的电荷,满足电子学系统低噪声的设计要求.

图3显示了VATAGP8芯片的内部原理图,芯片的每个通道都有一个用于电荷积分(Charge Integrator)的前置放大器(Preamplifier)、“快”成形电路(“Fast”Shaper)、高通滤波电路(HP-filter)、“慢”成形电路(“Slow”Shaper)、采样保持电路(Sample & Hold,S/H)、阈值电压比较器(Levelsensitive Discriminator).当有电荷注入并且快成形输出的脉冲高度超过可编程阈值电压(Vthr)时,电压比较器将产生该条通道的触发脉冲.多条通道的触发输出相“或”(OR)后,产生整个芯片的触发信号(Trigger).慢成形电路输出的准高斯(Semigaussian)波形经过峰值保持(hold)后,再根据读出时序(Readout Logic)从所有通道或所选通道输出脉冲高度值.

图3 VATAGP8芯片的内部原理图Fig.3 Internal schematic diagram of VATAGP8 chip

为了进一步提高集成度,同时减小与探测器单元之间连接线的分布电容,VATAGP8芯片是没有管壳的裸芯片,需要用导电胶粘贴在FEE板上,再通过引线键合的方式将芯片的管脚(Pad)连接到FEE板的焊盘上.VATAGP8芯片与探测器单元的封装连接是电子学设计的另一个难点.VATAGP8裸片尺寸为8180 μm×6075 μm×300 μm,128个输入通道的Pad交错排列,相邻通道的Pad垂直间距仅有45.6 μm,而常规PCB工艺不能加工出间距很小的焊盘,因而很难用较低成本做到芯片的128个Pad都与PCB上的焊盘相连.在不影响研究内容的前提下,从VATAGP8裸片的128个输入Pad中挑选了的42个,#0-6(依次选择)、#24-30(依次选择)、#45–57(间隔选择)、#73-79(依次选择)、#97-103(依次选择)、#115–127(间隔选择),以PCB上的金属线为过渡,通过引线键合技术连接探测器单元.图4显示了VATAGP8芯片、SSD、PCB之间的连接关系,其中与VATAGP-8上42个Pad相连的微条在探测器单元上自上而下隔条连续排列.

图4 集成在前端电子学板上的VATAGP8芯片Fig.4 The VATAGP8 chip integrated on FEE board

VATAGP8芯片收集硅微条探测器单元的电荷信号,经过放大成形后以差分电流形式输出.电流信号通过三极管PUMX1和电阻网络转化为电压信号送入DAQ.此外,FEE板上的温度通过两片温度传感器DS18S20进行实时监控,并通过π型滤波器对接入硅微条探测器单元的输入高压进行滤波处理.

3.4 数据获取电路设计

数据获取电路主要功能包括控制VATAGP8的工作时序、控制ADC(Analog-to-Digital Converter)的数据采集、与上位机实现通讯交互、监控高压模块输出状态等等.为方便功能调试,数据获取电路分成DAQ母板和两个子板(FPGA核心板、高压模块),其中FPGA核心板负责提供控制逻辑,高压模块提供反向偏压,DAQ母板负责组织、调配相关的电路资源.

DAQ母板通过预留的接口与FEE板、FPGA核心板、高压模块相连接.FEE板输出的差分电压信号传入DAQ母板后,通过运放AD8032芯片实现差分信号到单端信号的转换,单端电压信号再经过ADC采集得到原始数据.ADC芯片的选型需要综合考虑精度、功耗、采样率等因素,其中Delta-Sigma架构的ADC精度较高,但是采样率偏低;流水线架构的ADC的具有较高采样率,但是功耗较大;因此DAQ母板采用逐次逼近寄存器架构的ADC芯片AD74763https://www.analog.com/cn/products/ad7476.html.,该芯片具有12 bit精度,总体性能较为均衡,能够在较低的功耗下实现高的数据吞吐量.DAQ母板上设置了双串口模块,采用FTDI公司的LC231X4https://ftdichip.com/products/lc231x/.和Adfruit公司的FT232H5https://www.adafruit.com/product/2264.通信模块实现FPGA芯片与上位机之间的串口通信.在DAQ母板上,通过DAC(Digital-to-Analog Converter)芯片AD5060控制高压模块(CA02P)的输出电压,从而提供探测器单元正常工作所需的反向偏压.CA02P输出的监控电压,在DAQ母板上经过电压跟随器后使用ADC进行采集从而实现高压的监控.为了实现高压模块电流的监测,在电源输入端串联了小阻值的采样电阻,使用电流检测芯片INA199检测该采样电阻两端的电压信号,并使用ADC芯片进行采集.

FPGA核心板上的主控芯片采用Intel公司Cyclone 10系列的10CL025YU256C8G6https://www.intel.com/content/www/us/en/products/details/fpga/cyclone.html.,并在板上配置了能够正常工作的最小系统.板上预留了大量的I/O拓展端口连接DAQ母板,驱动控制信号逐级传输到其他模块或者接收信号输入.FPGA的时钟信号由外部50 MHz的有源晶振提供,经过锁相环(Phase Loop Lock,PLL)分频出20 MHz的时钟供逻辑设计使用.

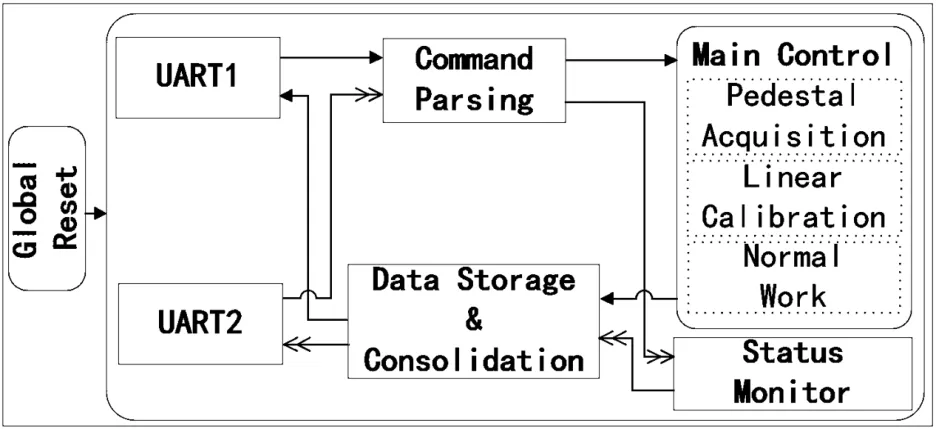

整个系统的工作时序由FPGA控制,FPGA逻辑功能划分如图5所示,主要包括串口收发(UART)、全局复位(Global Reset)、命令解析(Command Parsing)、数据整合(Data Consolidation)、主控(Main Control)和状态监控(Status Monitor)模块.当系统上电后,通过全局复位对系统进行初始化.FPGA通过串口1接收上位机发送的指令,根据指令解析的结果,选择主控模块中的一种模式进行工作,采集得到的数据经过处理、存储、打包后通过串口1回传到上位机.串口2主要负责接收上位机发送的高压模块控制指令以及发送状态监控模块采集的温度、电压、电流数据到上位机.在主控模块中,VATAGP8芯片以200 kHz的频率对128条通道的信号进行移位输出,ADC的采样率为500 kHz,因而在FPGA中设计了256×8 bit的FIFO(First Input and First Output)来缓存ADC采集的数据,并使用256000波特率的串口进行数据传输.在每次数据传输完成后,电子学系统才会对下一次的触发进行采集.状态监控模块使用6×8 bit的FIFO缓存采集的高压、电流以及温度信息,电子学系统的状态信息将每秒更新1次并发送到上位机.

图5 FPGA逻辑设计基本框架Fig.5 Basic framework of FPGA logic design

3.5 上位机软件的设计

上位机软件使用LabWindows CVI进行设计开发,主要负责对上传数据的接收、分析、显示、筛选、分类存储等操作,也可以向数据获取电路发送不同的工作指令,实现对VATAGP8芯片寄存器的配置以及不同工作模式的切换.图6显示了上位机软件的主界面,其中包含了工作模式切换、串口配置、温度及高压状态监控、VATAGP8寄存器及测试配置菜单.系统通过上位机配置完成后,可以对电子学系统的状态(温度、电压、电流)进行实时监控,并在菜单栏的子面板中实现工作模式的切换.此外,系统还可以通过上位机软件来配置VATAGP8芯片各种设置参数,如阈值电压、成形时间等,从而可以优化VATAGP8芯片的工作状态.

图6 上位机主界面Fig.6 The main interface of the master computer software

4 电子学系统的性能测试

在系统搭建完成后,需要对电子学系统进行一系列性能测试,包括128通道的基线和噪声测试、线性刻度测试以及宇宙线缪子的响应测试.

4.1 基线和噪声测试

VATAGP8芯片有两对差分输出管脚(outp_d/outm_d和outp u/outm_u),在系统串行读出下分别对应从#0到#127通道顺序读出以及#127到#0通道逆序读出的输出.电路中使用了两个ADC(ADC-1、ADC-2)分别对VATAGP8芯片两路输出后经过转换、运算、放大后的信号进行采集.串行读出下ADC每次采集的原始数据可以表示为[15]:

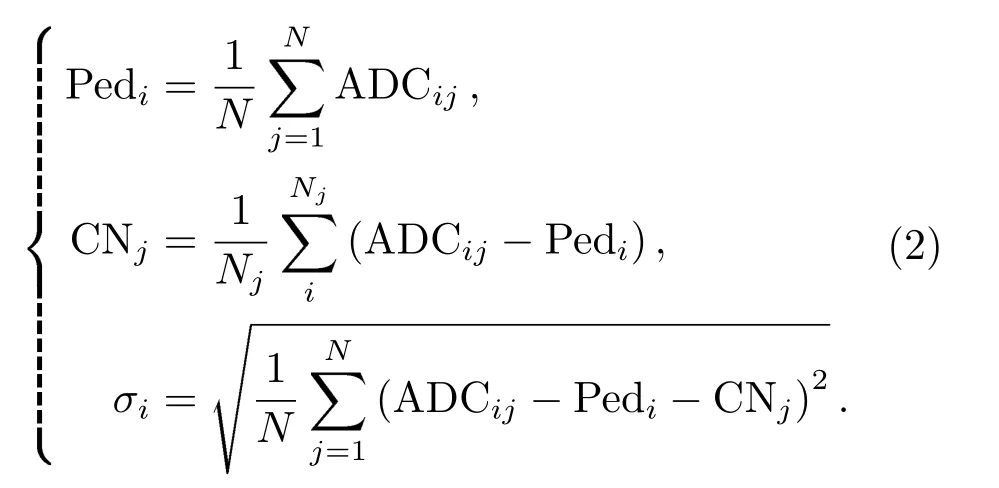

其中Pedi表示通道i的基线,CNj表示第j次采集时的共模噪声,Noisyij表示通道i第j次采集的随机噪声,Signalij表示通道i在第j次采集得到的信号.基线采集模式下,没有外部信号输入,Signalij可视为0.在经过N次采集后,通道i的基线Pedi和随机噪声表征水平σi以及扣除坏道(噪声过大的通道和没有信号的通道)后所有Nj条通道的共模噪声CNj可以由下面的公式得到[15]:

一般系统在正常工作模式下,VATAGP8芯片采用顺序读出的方式进行输出,并根据输出的原始数据计算出芯片128条输入通道在ADC-1所在电路的基线和噪声水平.而在ADC-2所在电路,VATAGP8芯片也可以通过逆序读出的方式测试128条输入通道的基线和噪声水平,从而对系统的基线和噪声水平进行对比验证.

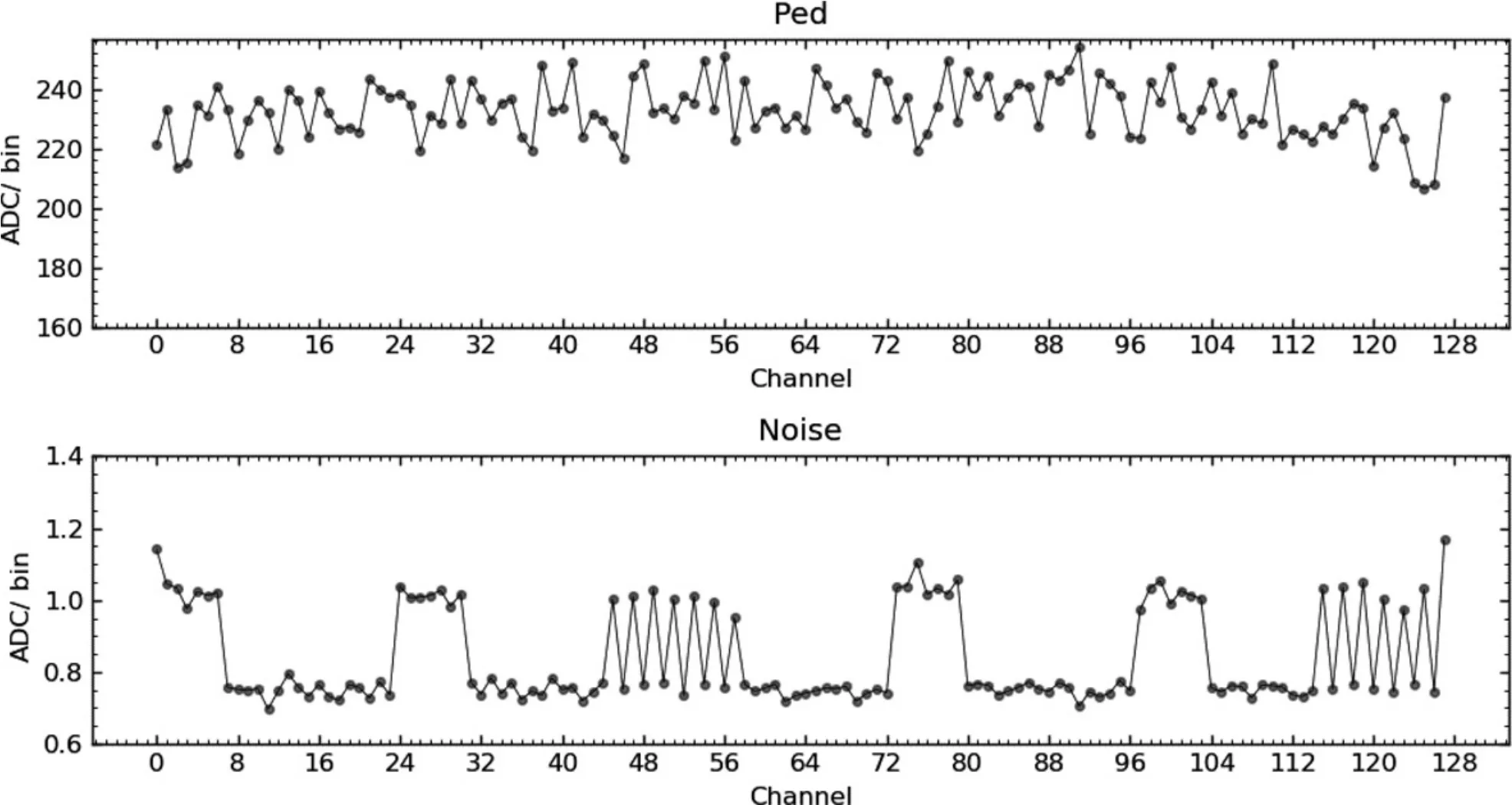

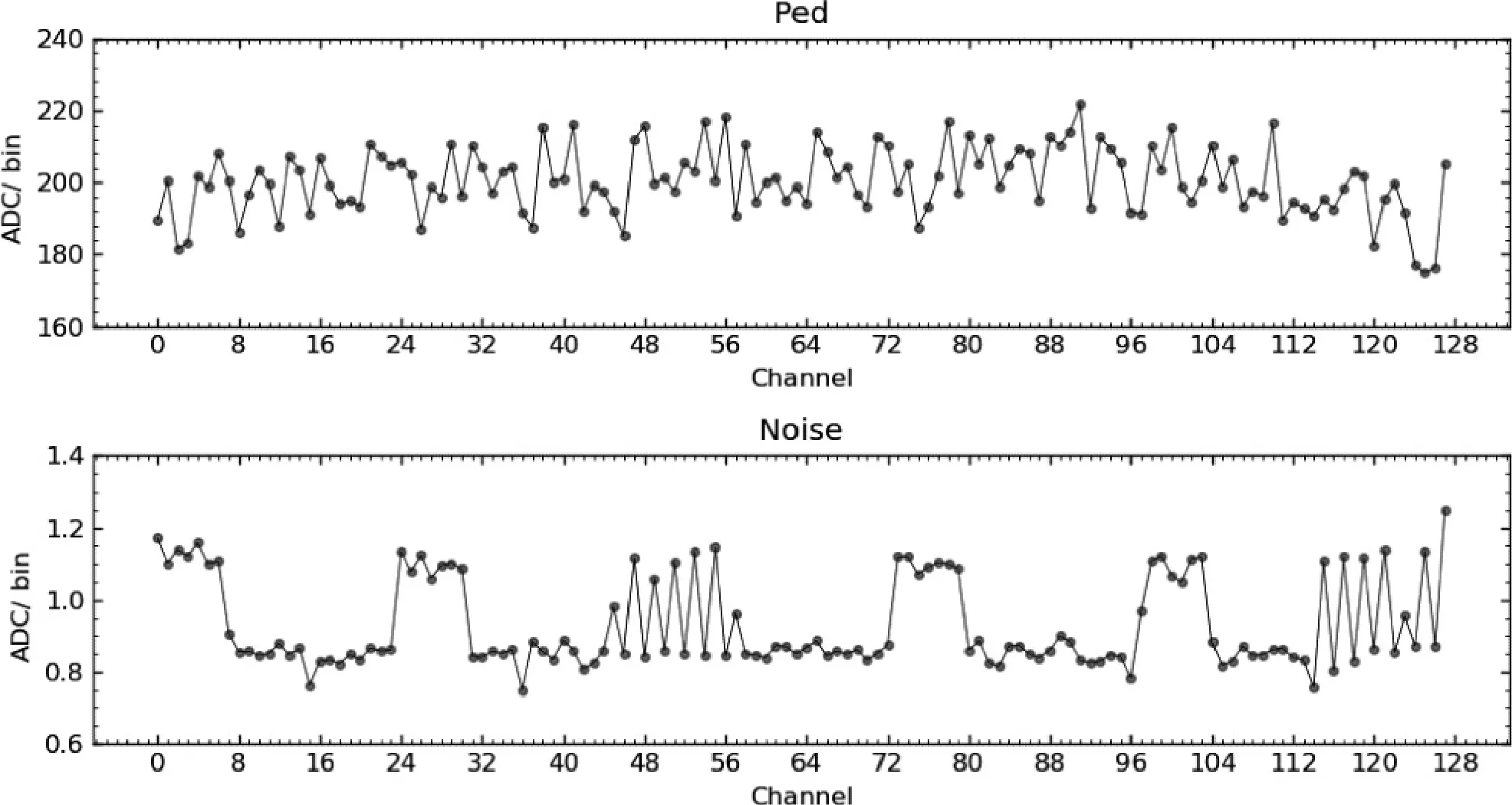

图7和图8显示了电子学系统中VATAGP8芯片分别在顺序、逆序读出条件下128条通道的基线和噪声水平测试结果.系统在基线模式下测试的结果表明,由ADC-1采集得到128条通道的噪声水平在0.70–1.17 bin之间,基线在206.31–254.30 bin之间.而ADC-2采集得到的128条通道的噪声水平在0.75–1.25 bin之间,基线在174.92–221.87 bin之间.VATAGP8芯片顺序读出和逆序读出在芯片内部的电路略有差异,因而两种读出的基线和噪声数据也略有差异,但在可接受范围内.图7和图8中有42个通道的噪声明显大于其余通道的噪声,这是由于这42个通道连接了探测器单元,VATAGP8芯片的输入电容增大导致噪声增加.根据4.2节线性刻度的结果可以计算出128条输入通道的噪声水平均低于0.093 fC,噪声性能表现良好,满足电子学系统低噪声的设计要求.

图7 128条通道顺序读出的基线(上)和噪声(下)Fig.7 The sequential order readout of pedestal(above)and noise(below)of 128 channels

图8 128条通道逆序读出的基线(上)和噪声(下)Fig.8 The reverse order readout of pedestal(above)and noise(below)of 128 channels

4.2 线性刻度测试

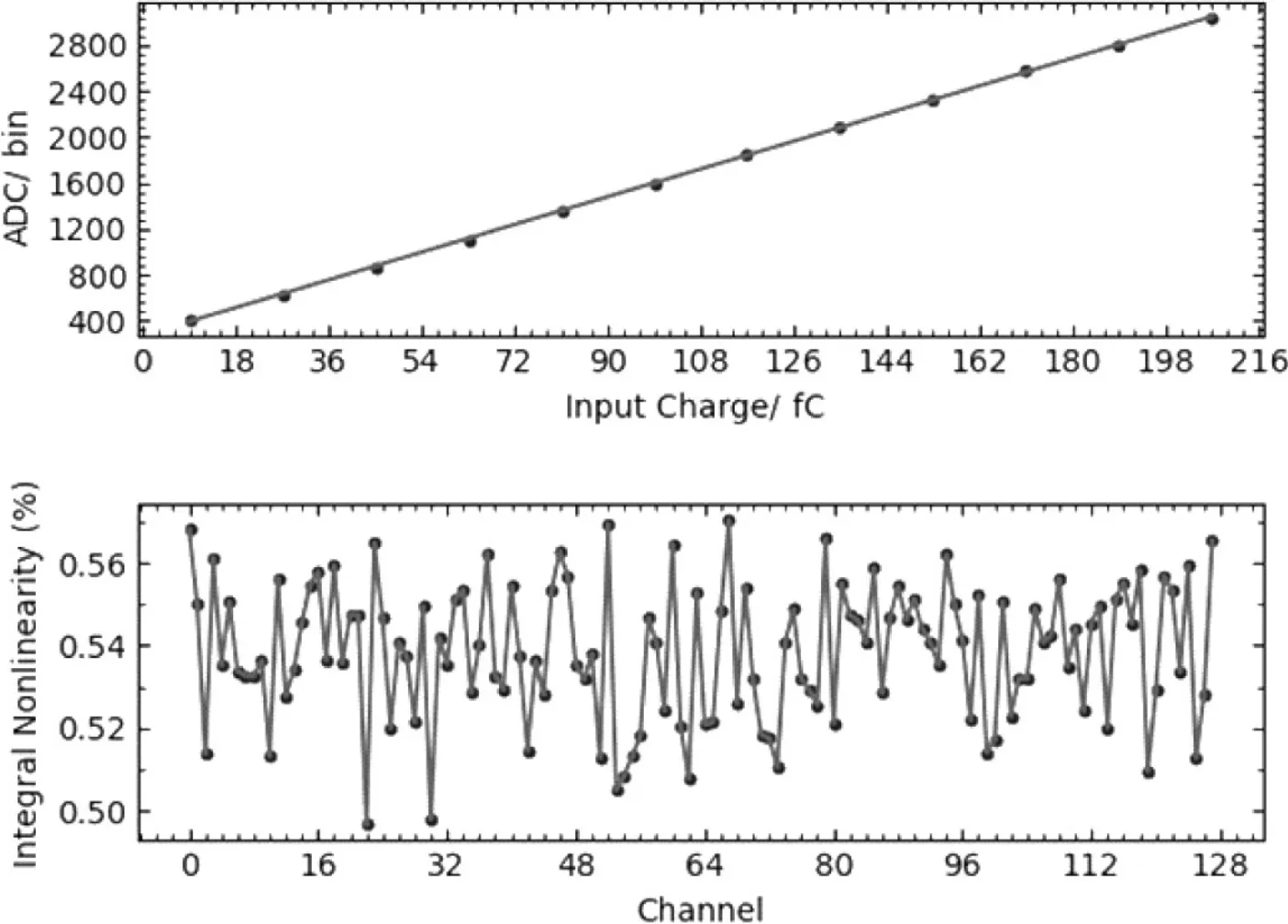

在线性刻度模式下,电子学系统通过线性调整测试信号的大小,实现对VATAGP8芯片各个通道0–200 fC动态范围内的扫描,并将扫描结果上传至上位机.上位机根据128通道的采集结果,依次对每个通道的标定数据进行线性拟合.图9是标定结果,#2通道在0–200 fC的输入范围内的线性增益约在13.41 bin/fC,而128条通道线性标定的积分非线性优于1%.

图9 #2通道线性标定的结果(上)以及128条通道线性标定的积分非线性(下)Fig.9 The results of #2 channel’s linear calibration(above)and the INL of 128 channels(below)

4.3 宇宙线缪子的响应测试

为了测试硅微条探测器单元对宇宙线中缪子的响应能力以及电子学系统长时间工作时的稳定性,将连接探测器单元的FEE板屏蔽外界光、电场和灰尘的干扰,搭建了图10所示的宇宙线缪子测试平台,该平台主要由上位机、直流电源、FEE、DAQ和高压模块组成.系统进行测试时,外部电源提供读出电子学所需的直流电压,高压模块提供探测器单元所需偏压,电子学系统采集探测器单元产生的缪子事例并上传至上位机处理、保存,每隔20 min电子学系统自动更新一次基线.

图10 测量宇宙线缪子搭建的测试平台Fig.10 Test platform for measuring cosmic ray Muon

缪子最小电离粒子在320 μm厚的硅微条探测器单元中由于能损而产生的电子-空穴对数量大约在22000[16]左右,相当于3.52 fC的电荷.系统的线性增益约为13.41 bin/fC,因而可计算出缪子最小电离粒子对应的理论峰值为47.20 ADC bin.在系统稳定工作20 h后,得到了约35241个缪子事例,对采集的事例数据进一步处理后绘制出图11所示的缪子的电离损失能谱.如图所示,能谱图上可以清晰地显示出一个MIP峰,经过pyLandau7https://github.com/SiLab-Bonn/pyLandau.包中的朗道-高斯卷积拟合后得到的峰值约为39.59 bin,与理论峰值存在偏差可能是由于硅微条探测器单元中电子-空穴对在漂移和扩散时发生损失[17],未能全部被硅微条上电极收集读出.结合噪声测试的结果,可以计算出电子学系统的信噪比大于32,满足系统高信噪比的设计要求.

图11 Landau-Gaussian卷积拟合的缪子电离损失能谱Fig.11 The spectrum of ionization energy loss of Muon fitted by Landau-Gaussian convolution

5 总结

本文介绍了一种使用VATAGP8芯片来实现硅微条探测器单元读出的电子学原型系统,测试了电子学系统中VATAGP8芯片128条输入通道的基线、噪声水平以及42条硅微条通道对宇宙线中缪子的响应能力.结果表明,该电子学系统能够满足设计要求:系统的128条输入通道的噪声水平低于0.093 fC,在0–200 fC输入动态范围内具有良好的线性,积分非线性优于1%,测试得到电子学系统的信噪比大于32,宇宙线缪子在硅微条探测器单元中电离损失的能谱与Landau-Gaussian分布符合较好.