电力半导体场效应管瞬态响应特性研究

鞠 晨

(国能神东煤炭集团公司,陕西 神木 719315)

在电力半导体器件中,电力半导体场效应管(MOSFET)由于其独特的高输入阻抗、低驱动功率、高开关速度等特点,使得其在开关电源、马达驱动、电机调速、不间断电源、逆变器等各种电力电子设备中得到广泛应用[1-3]。随着工艺的不断发展,电力半导体场效应管集成度的不断提高,单胞的尺寸越来越小,加之该类器件经常工作在快速开关转换、大电流的状态下,在实际使用过程中,其可靠性问题获得了研究人员的普遍关注[4-5]。

开关损耗过大导致的功率烧毁是造成电力半导体场效应管失效的主要原因之一。为了从芯片级有效的改善电力半导体场效应管在点火控制器、开关电源等电路系统中的开关性能,并提高电力半导体场效应管的使用可靠性,利用TCAD半导体器件仿真软件,在击穿特性、输出IV特性、转移特性等静态特性满足电参数指标要求的前提下,对电力半导体场效应管的使用条件和结构参数进行优化。详细地分析了不同测试条件(栅极脉冲电压、漏源电压、栅极电压脉冲宽度及占空比)、不同结构参数(多晶硅窗口区宽度(LW)与多晶硅区宽度(LP)的比例、N型外延层掺杂浓度、源极金属芯片的覆盖面积比例、栅氧化层厚度)对器件栅充电时间及器件开通时间的影响。

1 场效应管单元结构参数及物理模型

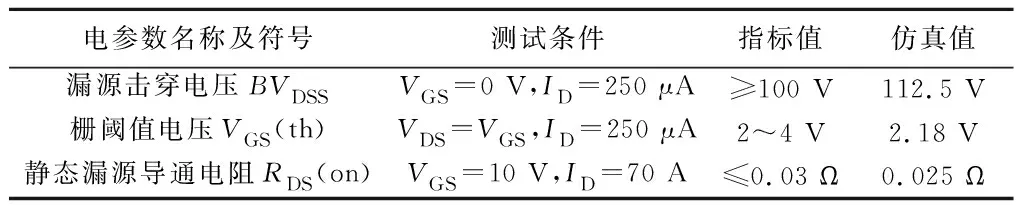

根据电参数指标(表1)的要求,利用TCAD半导体器件仿真软件对电力半导体场效应管单元结构进行设计。设计得到的结构参数为:采用平面栅、槽型源区结构,单胞为条形,单胞半宽度为10 μm,多晶硅区半宽度(LP)为7 μm,窗口区半宽度(LW)为3 μm,沟道长0.92 μm。N型外延层晶向为<100>,厚度为7 μm,掺杂浓度为1×1015cm-3,外延层少子寿命为0.1 μs。P体区结深为1.81 μm,沟道表面平均浓度1.5×1017cm-3。N+源区结深为0.48 μm,表面浓度为3.5×1019cm-3。栅氧化层厚度为60 nm,多晶硅栅厚度为0.35 μm,多晶硅栅极集成防静电二极管,多晶硅防静电二极管PN结两侧杂质浓度由N+源区、P体区杂质横向扩散浓度决定。源极引线孔半宽度为2.5 μm,源区槽深度为0.8 μm。

表1 电力半导体场效应管电学参数指标Tab.1 Electrical parameters of power semiconductor MOSFET

电力半导体场效应管半单胞结构如图1所示。仿真得到的器件输出特性均满足产品的电参数指标要求,表明器件结构参数设计较合理。基于上述设计得到的单元结构来对器件的开通性能及结构参数进行仿真研究。

图1 电力半导体场效应管半单胞结构Fig.1 Power semiconductor MOSFET semicell structure

仿真过程中,复合模型考虑了与掺杂浓度相关的SRH复合和俄歇复合;迁移率模型考虑了与温度、掺杂浓度、横向及纵向电场相关的载流子迁移率模型。还考虑了重掺杂引起的禁带变窄效应和能带简并效应。对电力半导体场效应管进行瞬态特性仿真时还需要考虑器件的自热效应。计算由自热引起的器件内部的温度分布需要求解下面的热传导方程[6-8]:

(1)

式中,T为热力学温度;c为晶格热容;k为热导率;Pn和Pp分别为电子和空穴的绝对热电功率;φn和φp分别为电子和空穴准费米势;Jn和Jp分别为电子和空穴电流密度;κB是玻尔兹曼常数;EC和EV分别为导带底和价带顶能级;q为基本电荷;R为复合率。

为了精确仿真自热效应对电力半导体场效应管瞬态特性的影响,利用非等温能量平衡传输模型模拟载流子的输运过程。非等温能量平衡传输模型对漂移—扩散模型在非等温情况下进行了扩展,它考虑了晶格温度梯度对电流密度的贡献。考虑晶格温度梯度影响后的电子和空穴电流密度方程为[6-8]:

Jn=-nqμn(▽φn+Pn▽T)

(2)

Jp=-pqμp(▽φp+Pp▽T)

(3)

式中,n和p分别为电子和空穴浓度;μn和μp分别为电子和空穴迁移率。

假设单元结构左、右边界及上边界与外界均无热量交换。瞬态特性测试条件:栅压脉冲上升、下降时间均为0.1 ns,脉冲宽度10 μs,占空比50%,空气自然冷却(空气自然换热系数为1/0.3)。

2 仿真结果与分析

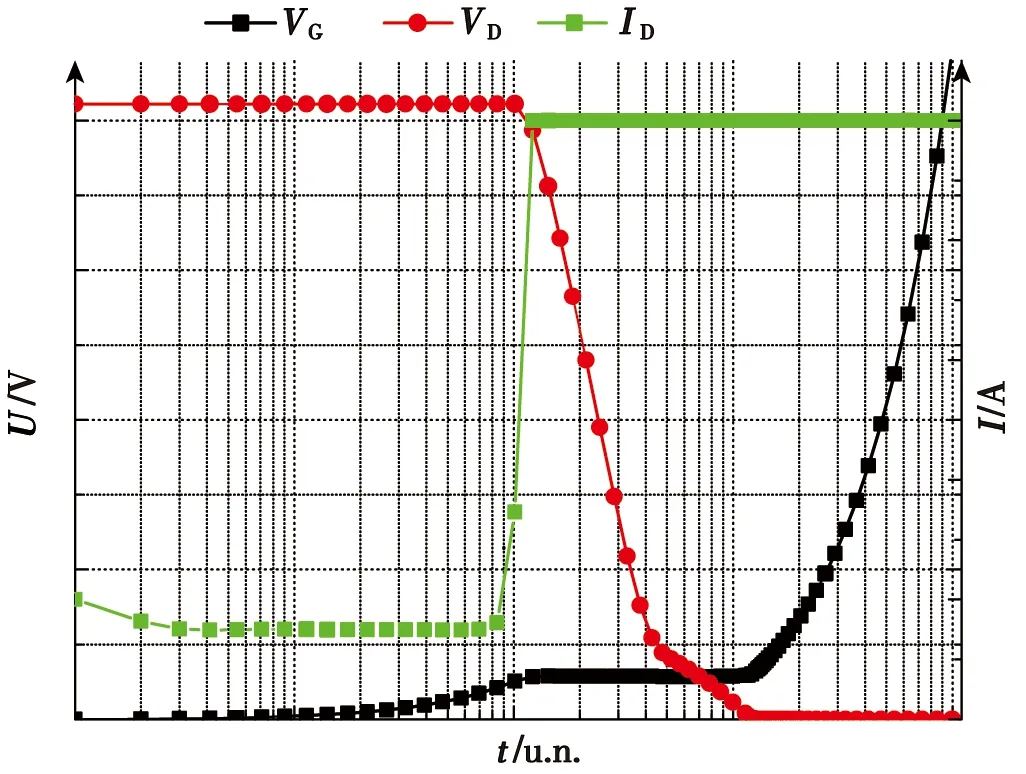

电力半导体场效应管的导通过程电流电压曲线如图2所示,测试电路为钳位非感性负载电路。电力半导体场效应管的导通过程分为3个阶段。第1阶段:开通延迟阶段(开通延迟时间),栅极驱动电压从0上升,对栅源电容充电,该阶段栅源电压几乎线性上升,栅源电容越小,栅源电压上升越快。第2阶段:开通上升阶段(上升时间),电力半导体场效应管的栅源电压达到阈值电压,漏极电流开始上升;漏源等效输出电容会对器件容性放电,漏源电流上升,漏源电压下降。同时受到栅漏反馈电容的影响,栅源电压的上升速率非常平缓(平台)。第3阶段:漏源电容电荷放完,漏源电压近似为0,并保持不变;反馈消失。栅源电压升高到开路脉冲,进入稳态导通期。由图2可见,在栅源电压平台阶段,漏极电流上升的速度是漏极电压下降速度的几倍,导致器件开通功率损耗的增加。

图2 电力半导体场效应管的导通过程电流电压曲线Fig.2 Output characteristics of power semiconductor MOSFET during conduction

电力半导体场效应管在导通的3个阶段中,单胞内部电流线分布的变化如图3所示。当栅源电压较低(图3(a),第1阶段)时,沟道尚未形成,漏源电压反向施加在P体区与N-外延层形成的PN结上,电流较小,为PN结泄漏电流,大部分流经P体区与外延层在表面处的结边缘。随着栅源电压的增大(图3(b),第2阶段),栅源电压大于器件阈值电压,漏源电流由两部分组成,一部分为流经P体区与N-外延层形成的PN结的反向泄漏电流,另一部分为流经沟道(P体区表面反型层)的沟道电流。随着栅源电压进一步增大,P体区表面反型程度进一步加强,沟道电阻进一步减小,导致PN结反向泄漏电流进一步减小,沟道电流进一步增大。最终,电力半导体场效应管电流全部为沟道电流(图3(c),第3阶段)。

图3 电力半导体场效应管导通过程Fig.3 Power semiconductor MOSFET conduction process

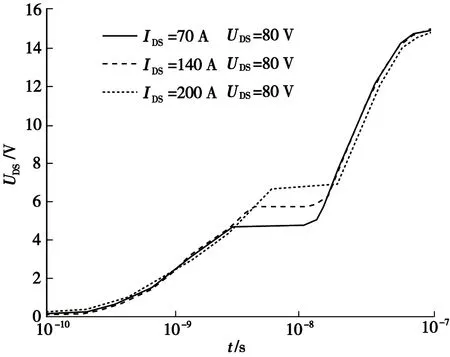

仿真得到的漏源电流对器件开通特性的影响如图4所示。栅源电压为15 V,栅源电阻为5 Ω,漏源电压为80 V。由图4器件开通时间曲线可见:随着漏源电流的增大,器件开通时间随之增长,对导通延迟时间的影响较显著。当电力半导体场效应管处于饱和导通状态时,漏源电流近似与栅源电压的平方成正比。即漏源电流越大,沟道反型电荷密度越大,栅源电容的充电时间越长,器件导通延迟时间越长。且由于栅漏电压和栅漏电容(栅漏电荷QGD)几乎相同,因此栅源电压维持恒定的时间(miller平台时间)几乎相同。因此,随着漏源电流的增大,导通延迟时间随之增大,上升时间变化幅度较小。

图4 漏—源电流对电力半导体场效应管瞬态响应特性的影响Fig.4 Influence of drain-source current on transient response characteristics of power semiconductor MOSFET

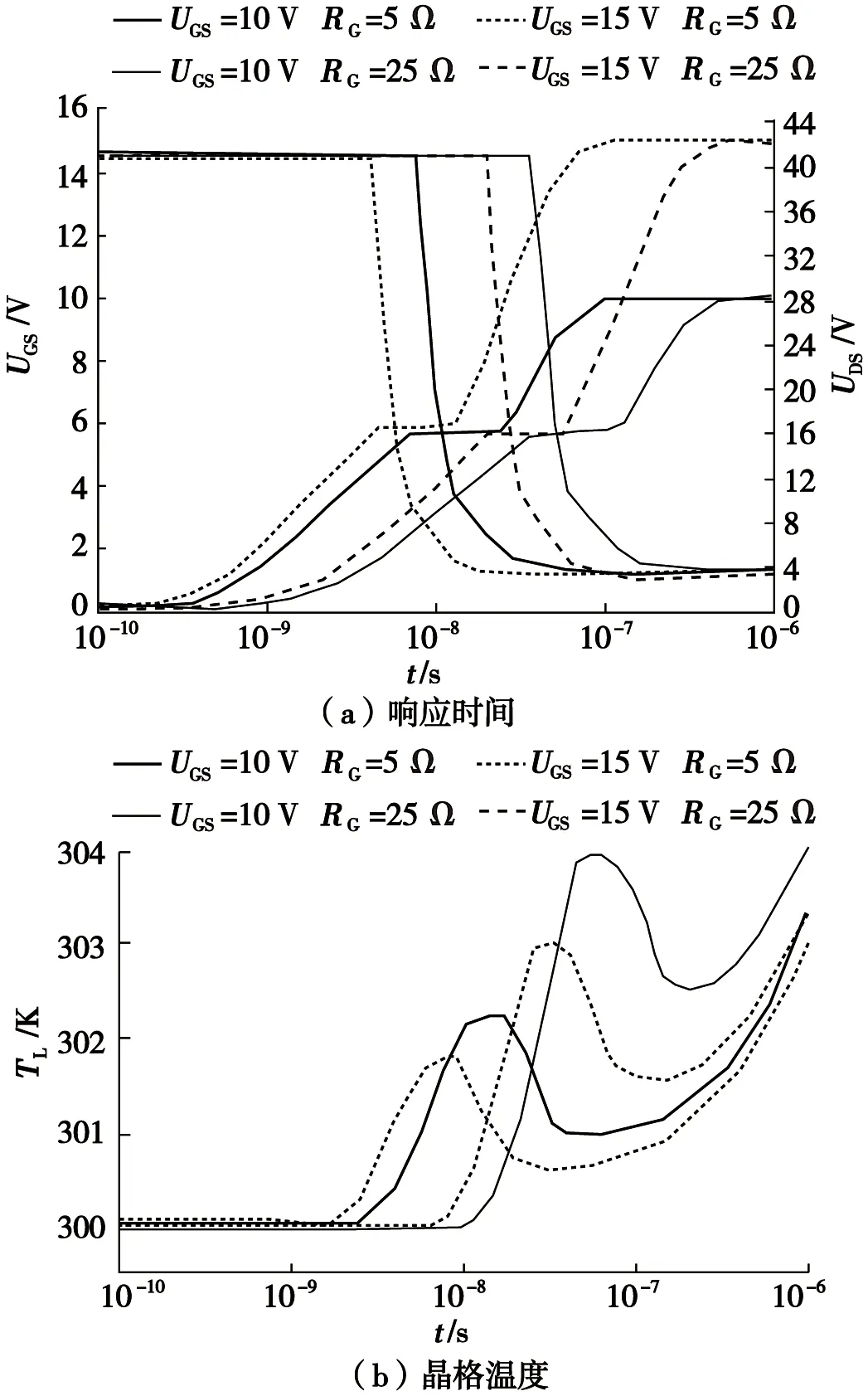

仿真得到的栅源电压和栅源电阻对器件开通特性的影响如图5所示。

图5 栅—源电压和栅极电阻对电力半导体场效应管瞬态响应特性的影响Fig.5 Influence of gate-source voltage and gate resistance on transient response characteristics of power semiconductor MOSFET

由图5(a)可知,导通时间最短的情况为栅源电阻为5 Ω,栅源电压为15 V情况,导通时间最长的情况为栅源电阻为25 Ω,栅源电压峰值为10 V的情况。由图5(b)可知,电力半导体场效应管开通时间越短,其开通过程中器件峰值晶格温度越低。原因为:随着栅源电压的增大或/和栅源串联电阻的降低,对栅源电容CGS的充电电流较大,栅源电容充电达到相同阈值电压的充电时间缩短,因此器件导通延迟时间随之缩短。电力半导体场效应管在开通过程中受到栅极—漏极电荷QGD的影响。QGD越大,UGS-QG波形中栅源电压维持恒定的时间越长,漏源电压从关断电压降低到饱和漏源电压VDSsat(达到饱和状态)的时间越长。在栅漏电容相同的情况下(器件结构参数相同),栅源电压越高,漏栅电压越低,漏栅电荷越小,相应的栅源电压维持时间(miller平台)越短,因此,器件上升时间随之缩短。漏极电流在miller平台开始时出现,且漏极电流上升的速度是漏极电压下降速度的几倍,器件上升时间越长,电力半导体场效应管开通损耗越大,器件产生大量热量,开通过程中器件峰值晶格温度越高。

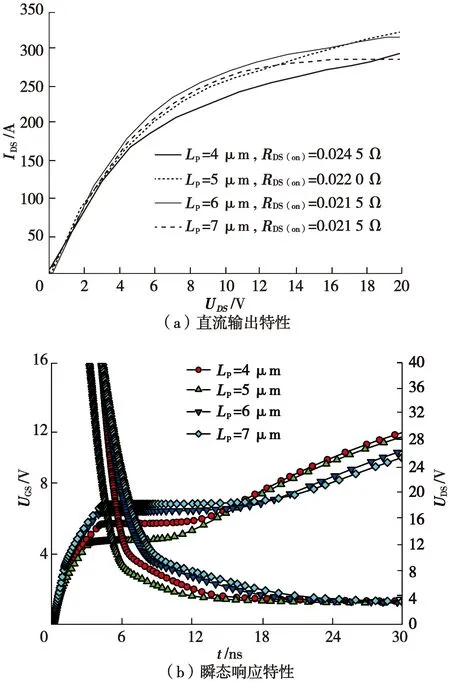

仿真得到的不同多晶硅宽度LP对电力半导体场效应管输出电流—电压特性及开通时间的影响如图6所示。窗口区宽度LW为2 μm,栅氧化层厚度为60 nm。由图6(a)可知,当多晶硅宽度在4~7 μm内时,电力半导体场效应管导通电阻均满足电参数指标要求。随着多晶硅宽度LP的增大,电力半导体场效应管导通电阻随之减小。当多晶硅宽度LP≤5 μm时,在相同的漏源电压情况下,多晶硅宽度越大,漏源电流越大。当多晶硅宽度LP增大到6 μm时,在较低漏源电压下,输出特性曲线几乎重叠在一起,而在漏源电压较高时,多晶硅宽度越大,漏源电流越低,即出现了“电流饱和效应”。原因为:随着多晶硅区宽度的增大,由沟道流出的电子电流在对晶硅区域中的输运路径发生了显著变化,电子电流由沟道边缘到漏极的输运路径展宽,等效于器件导通电阻减小。当多晶硅宽度较大(LP≥6 μm),且漏源电压较高时,漏源电流减小的原因为:随着多晶硅宽度的增大,P体区间距增大,P体区之间不能成为彼此的有效分压环,导致达到一定的漏源电压下,P体区表面电场强度较大,电子迁移率在强电场下降低,导致随着漏源电压增大漏源电流减小的现象。

由图6(b)开通特性可见:当LP=5 μm时,电力半导体场效应管阈值电压较低,其导通延迟时间较短,为3.43 ns,其上升时间为9.59 ns。当LP=4 μm时,其导通延迟时间为4.39 ns,其上升时间为11.46 ns,当LP=6μm时,其导通延迟时间为4.49 ns,其上升时间为14.57 ns。当LP=7 μm时,其导通延迟时间为4.64 ns,其上升时间为17.81 ns。对于LP=4 μm,其导通时间为15.85 ns;对于LP=5 μm,其导通时间为13.02 ns;对于LP=6 μm,其导通时间为19.06 ns;对于LP=7 μm,其导通时间为22.45 ns。除LP=5 μm外,随着多晶硅区宽度LP的增大,器件导通时间随之增大。原因为:随着多晶硅区宽度的增大,电力半导体场效应管阈值电压增大,所需栅电荷较多,栅源电容充电时间较长,即器件导通延迟时间随之增大。同时随着多晶硅区宽度的增大,栅漏电容面积增大,在相同的漏源电压情况下,栅漏电容较大,栅漏电荷QGD较多,从而导致栅源电压维持恒定值的时间随之增长,即器件上升时间随之增长。

图6 多晶硅栅极宽度对电力半导体场效应管电性能的影响Fig.6 Influence of polysilicon gate width on electrical performance of power semiconductor MOSFET

仿真得到的栅氧化层厚度对电力半导体场效应管电性能的影响如图7所示。

图7 栅氧化层厚度对电力半导体场效应管电性能的影响Fig.7 Influence of gate oxide thickness on electrical performance of power semiconductor MOSFET

图7(a)为仿真得到的栅氧化层厚度tox对电力半导体场效应管直流参数的影响,在仿真过程中,多晶硅宽度LP为4 μm,多晶硅栅电极下的氧化层厚度均匀。由图7(a)可见:栅氧化层厚度tox在30~100 nm内变化时,随着栅氧化层厚度tox的增大,电力半导体场效应管导通电阻随之增大。原因为:在相同栅源电压下,随着栅氧化层厚度tox增大,P体区反型层中电子浓度降低,等效的沟道电阻增大,从而导致电力半导体场效应管导通电阻增大。图7(b)为仿真得到的均匀氧化层厚度对电力半导体场效应管开通时间的影响。由图7(b)可见:在器件开通过程中,开通延迟时间和开通上升时间均随着栅氧化层厚度的增大而增大,且增大幅度较大。原因:随着器件栅氧化层的增大,器件的阈值电压随之增大,器件达到阈值电压所需要的充电时间较长,导致器件开通延迟时间随着栅氧化层厚度的增大而变长。随着栅氧化层厚度的增大,器件导通电阻随之增大,漏源等效电容放电的过程中所需要的放电时间增大,漏源电压下降到稳定电压所需的时间较长,因此随着栅氧化层厚度的增大,器件开通时间增大。当栅氧化层厚度为30 nm时,器件开通时间为10.8 ns,当器件栅氧化层厚度增大到100 nm时,开通时间增大到23.4 ns。器件的开通时间越长,开通过程中的功率损耗越大,器件的峰值晶格温度越高。因此,为了降低器件的导通电阻和较短的导通延迟时间,在保证氧化层质量和成品率的前提下,需要减薄栅极氧化层厚度。

为了在不影响器件导通电阻和导通延迟时间的情况下,降低电力半导体场效应管的上升时间,即减小栅漏电容对开通时间的影响,器件结构可采用非均匀栅极氧化层结构,器件结构如图8所示。

图8 非均匀栅氧化层厚度电力半导体场效应管单元结构Fig.8 Power semiconductor MOSFET unit cell structure with non-uniform gate oxide thickness

仿真得到的厚栅氧化层结构对电力半导体场效应管瞬态响应特性的影响如图9所示。图9(a)为仿真得到的当薄栅氧化层为60 nm,厚栅氧化层宽度为3 μm时,厚栅氧化层厚度变化对电力半导体场效应管开通时间的影响。由图9(a)可见:随着厚栅氧化层厚度的增大,电力半导体场效应管导通延迟时间基本相同,而上升时间随之显著降低,表明在一定程度增加厚栅极氧化层厚度有利于降低器件的开通时间。图9(b)为仿真得到的当薄栅氧化层为60 nm,厚栅氧化层厚度为100 nm时,厚栅氧化层宽度变化对电力半导体场效应管开通时间的影响。由图9(b)可见:随着厚栅氧化层宽度增大,器件导通电阻越高,漏源等效电容放电时间越长。厚氧化层越宽,漏栅等效电容对栅源电容的充电时间影响越小,栅源电压越快地达到阈值电压,开通延迟时间越短。而对于开通上升时间,随着厚氧化层宽度的增大,存在最小值。当Lox1为2.5 μm时,器件开通上升时间最短。表明该条件下器件在折衷miller耦合电容和导通电阻方面最优。当Lox1为1.5 μm时,器件开通时间为12.5 ns;当Lox1为2 μm时,器件开通时间为11.5 μm;当Lox1为2.5 μm时,器件开通时间为11.1 ns;当Lox1为3 μm时,器件开通时间为11.4 ns。

图9 厚栅氧化层结构对电力半导体场效应管瞬态响应特性的影响Fig.9 Influence of thick gate oxide structure on transient response characteristics of power semiconductor MOSFET

3 结论

本文利用TCAD半导体器件仿真软件对电力半导体场效应管的瞬态响应特性进行了详细研究。仿真结果表明,由于影响栅—源电容的结构参数对器件的直流参数影响较显著,不能仅仅通过调整栅氧化层厚度、多晶硅栅极宽度等结构参数来改善开通性能。为了在不影响导通电阻和导通延迟时间的情况下,降低器件的上升时间,可采用非均匀厚度栅氧化层结构。适当提高栅—源电压、减小栅极电阻可缩短导通延迟时间。增大栅—漏氧化层厚度、优化栅—漏氧化层宽度可减小miller平台时间,从而减小开通上升时间。