H 型栅PMOS 跨导双峰效应建模

彭宏伟,曹梦玲,黄 天,王青松,朱少立,徐大为

(中国电子科技集团第五十八研究所 江苏 无锡 214035)

随着半导体工艺技术的飞速发展,绝缘体上硅(silicon on insulator, SOI)技术因为其集成度高、功耗低、器件速度快、抗辐照能力强、寄生电容小等优点,已经逐渐代替体硅技术成为集成电路应用中的主流技术[1]。

SOI MOS(metal oxide semiconductor) 器件根据埋氧(BOX) 上的硅膜厚度分为部分耗尽(partialy depleted, PD) SOI MOSFET 和全耗尽(fully depleted,FD) SOI MOSFET[2]。PDSOI CMOS 器件结构的体区通常是浮空的,这就导致器件内部累积着大量的空穴,易产生浮体效应[3]。而FDSOI CMOS 器件硅膜厚度较小,短沟道效应弱,源漏结寄生电容低,器件速度高于PDSOI CMOS 器件[4-6]。但超薄的硅膜厚度在实际工艺过程中很难控制,成本较高,所以SOI 电路中PDSOI 器件的应用更为广泛,本文中H 型栅PMOS 为PDSOI CMOS 器件[7]。

针对PDSOI 结构电学特性的建模研究,国内外研究人员已取得了一定的进展与突破。文献[8]建立了一种适用于300℃高温的SOI MOSFET 模型。文献[9]开发了一种PDSOI 器件自热效应和浮体效应的模型提取方法。文献[10]提出了一种新型SOANN 埋层SOI 结构,有效地抑制了器件的自热效应。文献[11]提出了一种PDSOI 工艺H 型栅MOS 结构的热敏电阻测试和提取方法。文献[12]设计了一种在MOSFET 栅极高漏电情况下,晶体管沟道的电流提取方法。以上研究成果主要解决了SOI 器件的自热效应、浮体效应和高温高漏电情况下模型的建立,但对于H 型栅MOS 结构的跨导双峰效应模型的建立暂未涉及。

本文首先使用0.15 µm SOI 工艺制备了3.3 V工作电压下BTS 型和H 型栅两种MOS 实验器件。在仿真和实际测试两方面分析了H 型栅PMOS结构器件发生跨导双峰效应的机理。通过增加一条与主晶体管并联的寄生晶体管导电沟道的方式修正了BSIMSOI 模型,极大程度地提高了跨导双峰曲线的拟合精度。

1 器件结构和测试结果

PDSOI MOS 结构内部的浮体效应可以通过不同的体接触方式来减轻其对器件性能的影响,典型的体接触结构有BTS 型、H 型栅和T 型栅结构3 种。

BTS 型PMOS 器件的剖面结构如图1a 所示。为了抑制器件的浮体效应,将其源体短接,但源漏不可互换,在电路应用中受限。而H 型栅器件的源漏完全对称,漏(D)、栅(G)、源(S)、体(B)四端均可引出,并且H 型栅PMOS 结构的栅边缘的寄生三极管效应较弱,器件的抗辐照能力强,其剖面结构如图1b 所示。T 型栅结构的体接触原理与H 型栅结构类似,但T 型栅结构只在沟道区一端布置了体接触通孔,抗辐照能力偏弱。此外,与BTS 型PMOS 相比,H 型栅PMOS 存在两种类型的Polysilicon Gate。其中,CG 被P+杂质注入,为P+-Polysilicon Gate;PG 被N+杂质注入,为N+-Polysilicon Gate。

图1 器件剖面结构

图2 展示了基于0.15 µm SOI 工艺制备了BTS型PMOS、H 型栅NMOS 和H 型栅PMOS 实验器件的跨导Gm曲线,其中,W表示栅宽,L表示栅长。实验数据由Keysight B1500A 测试系统进行电学特性测试后收集得到。漏电流的变化量 ΔIDS与栅压变化量ΔVGS之比为栅跨导Gm。

图2 器件跨导Gm 曲线

对于BTS 型PMOS 器件和H 型栅NMOS 器件,当VGS接近器件的阈值电压时,源端形成反型层,器件开启,跨导Gm曲线出现了峰值,然后随着VGS持续增大,Gm值逐渐降低,与传统MOS器件的Gm变化趋势一致。但H 型栅PMOS 结构在达到第一个峰值之后,若继续加大VGS,发现跨导曲线会出现第二个峰值,即双峰效应,这就使得目前的器件模型不适用于H 型栅PMOS 器件,为其电路特性的预测增添了难度。

2 器件特性原理及仿真

H 型栅PMOS 结构的双峰效应是由于其器件内部存在两种类型的Polysilicon Gate,当栅上施加一定的电压后,由S、D 和CG 构成的晶体管导电沟道开启,将其视为主晶体管。同时,H 型栅PMOS 内部还存在另一条由S、D 和PG 构成的寄生晶体管导电沟道。

为了探究主晶体管和寄生晶体管的开启顺序,本文引入了半导体物理中功函数差概念加以分析。不同类型的Polysilicon Gate 功函数差随衬底浓度的变化规律如图3 所示[13]。

图3 器件跨导随栅压变化测试曲线

本次工艺PMOS 衬底浓度为5×1014cm-3,所以P+-Poly Gate 的功函数差 Φms等于0.68 V,N+-Poly Gate 的 Φms等于-0.35 V,并且MOSFET 处于强反型时,阈值电压的计算公式为:

式中,Q0为有效界面电荷;Cox为单位面积的栅氧电容;ΦF为衬底费米势;γ 为衬偏系数;Vsb为衬偏电压。从上可知主晶体管阈值电压(Vth1)小于寄生晶体管阈值电压(Vth2),所以,当VGS达到Vth1时,主晶体管开启,跨导Gm曲线出现第一个峰值;而随着VGS逐渐增大到Vth2时,寄生晶体管开启,跨导Gm曲线会出现第二个峰值。

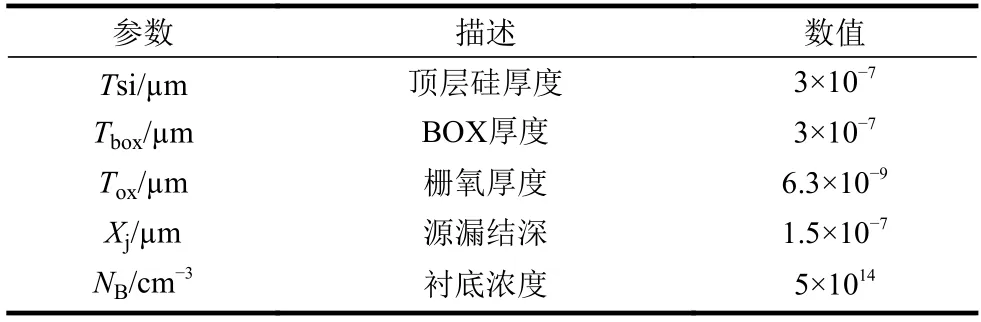

器件的实际工艺参数如表1 所示。为了更好地研究和验证H 型栅PMOS 器件双峰效应产生的原因和机理,依照实际的工艺参数,利用Sentaurus仿真软件,对H 型栅PMOS 器件和去掉体区的N+-Polysilicon Gate 器件的电学特性进行了3D TCAD 仿真对比。其中,漏端的电压固定为-0.1 V,栅端电压-1.5 V,源端和体端电压为0,器件三维结构和网格分布如图4 所示。

表1 器件的主要工艺参数

图4 器件电流密度分布

利用Sdevice 三维仿真的总电流密度模块辅助分析器件内部开启机制。对两个器件的栅极上施加相同的电压VGS。图5a 和图5c 分别为去掉体区的N+-Polysilicon Gate 与H 型栅PMOS 结构同一时刻的电流密度图。可以发现,去掉体区的N+-Polysilicon Gate,器件开启后,内部只存在一条由源区、漏区和P+-Polysilicon Gate 构成的晶体管沟道,而H 型栅PMOS 器件内部存在两条晶体管沟道,即源区、漏区和CG 构成的主晶体管沟道和源区、漏区和PG 构成的寄生晶体管沟道。

通过上述仿真结果可以得出,H 型栅PMOS由于其体区的N+-Polysilicon Gate,导致器件内部存在两条晶体管沟道。为了探究两条晶体管沟道的开启顺序,本文结合H 型栅PMOS 不同时刻下器件电流密度分布图进行分析,如图5 所示。在t1时刻,CG 区域电流密度较大,主晶体管沟道开启,寄生晶体管沟道未开启,如图5a 所示。在t2时刻,CG 和PG区域电流密度较大,两条晶体管沟道均开启,与上述理论分析相符。

图5 器件电流密度分布

此外,对于H 型栅NMOS 器件,其内部同样存在由不同功函数差的Polysilicon Gate 产生的两个不同阈值电压的晶体管沟道,但是测试结果未发现双峰效应,如图2a 所示。这是由于NMOS 的导电沟道为N 型,靠电子流动输送电流;PMOS 的导电沟道为P 型,靠空穴流动输送电流。但电子迁移率约为空穴迁移率的2.5 倍,所以H 型栅NMOS结构中主晶体管电流较大,寄生晶体管电流所占的比例较低,双峰效应不太明显。

3 H 型栅PMOS 双峰建模

在SOI 电路设计中,BSIMSOI 是业界最常用的SPICE 仿真模型,支持HSPICE 和SPECTRE 仿真器进行电路仿真[14]。该模型是在BSIM3v3 基础上开发出来的,保证了兼容性,延续了其物理含义强、收敛性好等优点。但是,作为SOI 电路中使用频率最高的SPICE 模型,BSIMSOI 无法反映H 型栅PMOS 结构跨导双峰效应。而栅跨导Gm为MOS器件的增益,是电路设计中的关键参数[15]。

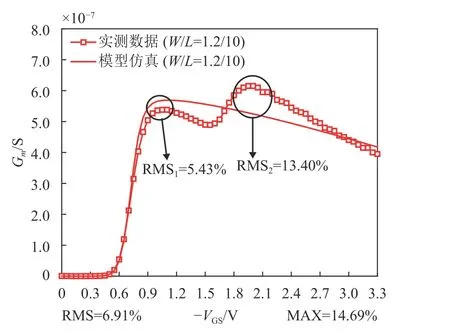

BSIMSOI 内部的等效电路如图6 中黑色实线所示,跨导Gm曲线的模型仿真结果和实测数据如图7 所示,左下角的RMS 值表示的是BSIMSOI模型仿真与实测所有数据的误差均方根值,右下角的MAX 值表示为模型仿真与实测所有数据的最大误差值。由图7 可知,BSIMSOI 的跨导Gm模型仿真曲线只存在一个峰值,无法表现出H 型栅PMOS 的跨导双峰效应,RMS 值为6.91%,MAX值为14.69%,其中,跨导Gm曲线在第一个峰值附近和第二个峰值附近的RMS 值分别为5.43%和13.40%,拟合精度差。

图6 器件等效电路图

图7 实测与模型仿真跨导Gm 曲线

在BSIMSOI 基础上,根据对跨导双峰效应内部物理机制的分析,对H 型栅PMOS 结构进行建模。由于H 型栅PMOS 器件内部存在两条晶体管导电沟道,因此,在图6 中增加了一条与主晶体管并联的寄生晶体管沟道,如图中虚线所示。

本文利用Keysight 公司MBP(model builder program)软件将寄生晶体管通过子电路的方式写入BSIMSOI 模型中。首先,定义子电路模型名字mp33_H,表示为3.3 V 工作电压下H 型栅PMOS器件,nrd 和nrs 分别表示漏端和源端电阻方块数,ad 和pd 表示漏区的面积和周长,as 和ps 表示源区的面积和周长,W和L表示主晶体管的栅宽和栅长,W_para 和dL_para 表示寄生晶体管的栅宽和栅长。最后,用子电路定义p33_H_core 为主晶体管,p33_H_para 为寄生晶体管,并将其并联。

子电路设定好后,利用BSIMSOI 模型参数对跨导Gm曲线进行拟合。模型拟合结果如图8 所示,将p33_H_core 主晶体管参数用于拟合跨导Gm曲线的第一个峰值附近区域。使用p33_H_para寄生晶体管参数用于拟合跨导Gm曲线的第二个峰值至3.3 V 区域。可知,新建的H 型栅PMOS 模型可有效反映其跨导双峰效应,并且RMS 值为1.91%,MAX 值为6.68%,极大程度地提高了模型精度。

图8 实测与模型仿真跨导Gm 曲线

此外,由图9 可知,固定L,随着W变小,H 型栅PMOS 器件的跨导双峰效应越来越明显,这是由于主晶体管电流降低,寄生晶体管电流占总电流比例上升。为了能够很好地拟合W方向的跨导双峰变化趋势,本文增加了BSIMSOI 内部的W方向bin 参数。

通过增加BSIMSOI 内部u0、ua 和ub 的迁移率W方向bin 参数:wu0、wua 和wub,可以良好地提高器件W方向的模型拟合精度,模型仿真结果如图9 所示。不同W尺寸下的H 型栅PMOS 模型拟合误差值结果如表2 所示,其中,RMS1、MAX1表示优化前的模型误差值,RMS2、MAX2 表示优化后的模型误差值。由此可知,在模型中增加W方向bin 参数后,模型精度得到了较大提升。

图9 实测与模型仿真跨导Gm 曲线

表2 模型仿真精度

4 结 束 语

本文结合Sentaurus 3D TCAD 仿真,首先分析了H 型栅PMOS 结构跨导双峰效应的内部电学机理,得出器件内部由于功函数差,存在两条不同阈值电压的晶体管导电沟道的结论。针对该器件特性,在标准BSIMSOI 模型的基础上,提出了与主晶体管并联的寄生晶体管模型,该模型使同尺寸下的H 型栅PMOS 结构的预测精度从6.91%提高至1.91%,最大误差从14.69%下降至6.68%。此外,利用BSIMSOI 内部的W方向bin 参数良好地优化了W较小尺寸的模型精度。本实验方案可以为PDSOI 工艺条件下电路的MOS 器件设计提供参考。